Level-triggered D flip-flop circuit based on resistive memory

A memory and flip-flop technology, which is applied to parts, electrical components, and electric pulse generation of electric pulse circuits, can solve the problems of insufficient layout area advantage and insufficient refinement of circuit structure, etc., and achieve layout area advantage and simple structure , the effect of large layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

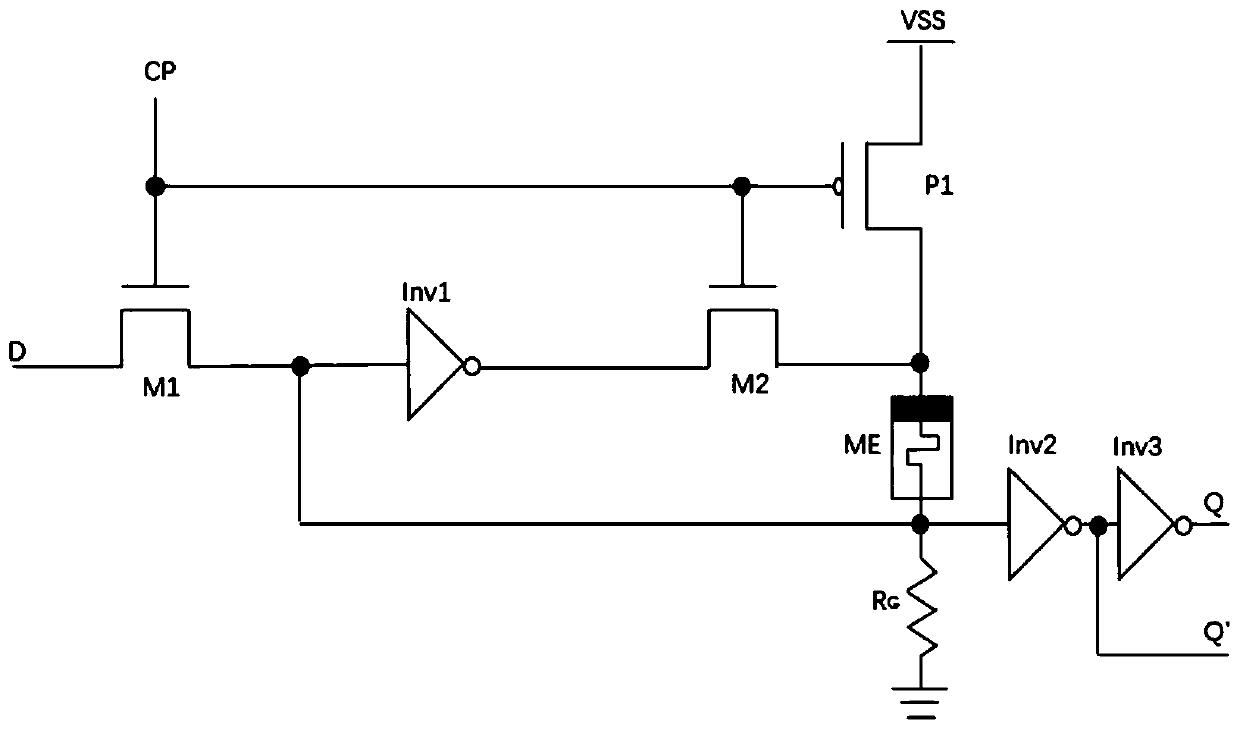

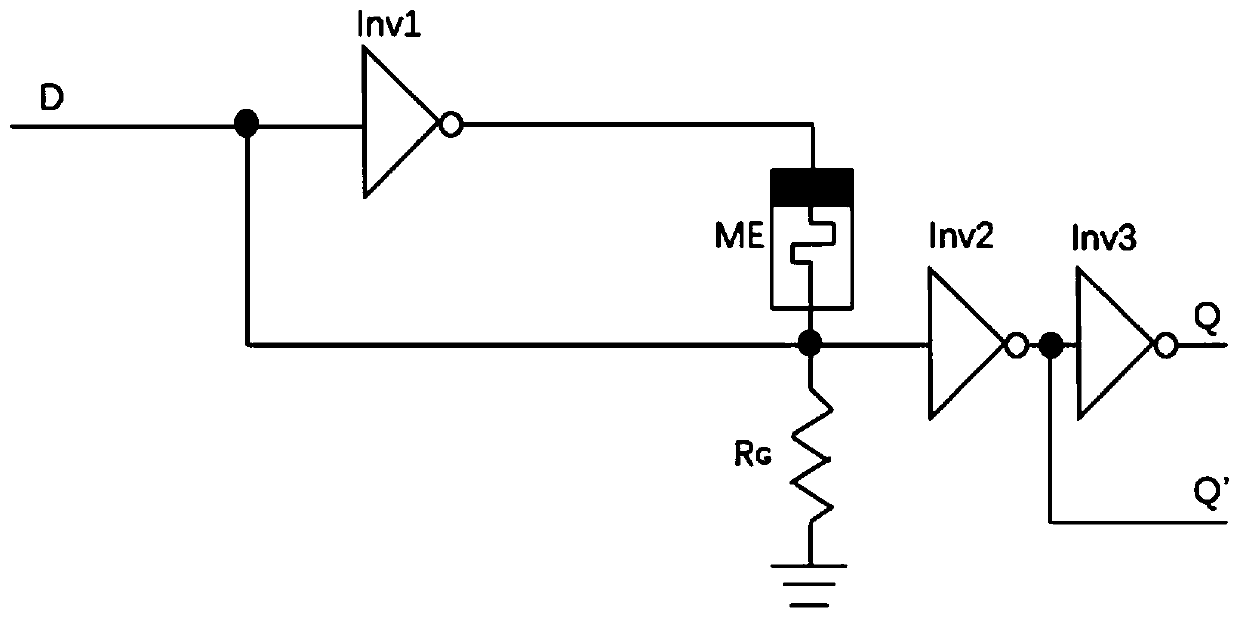

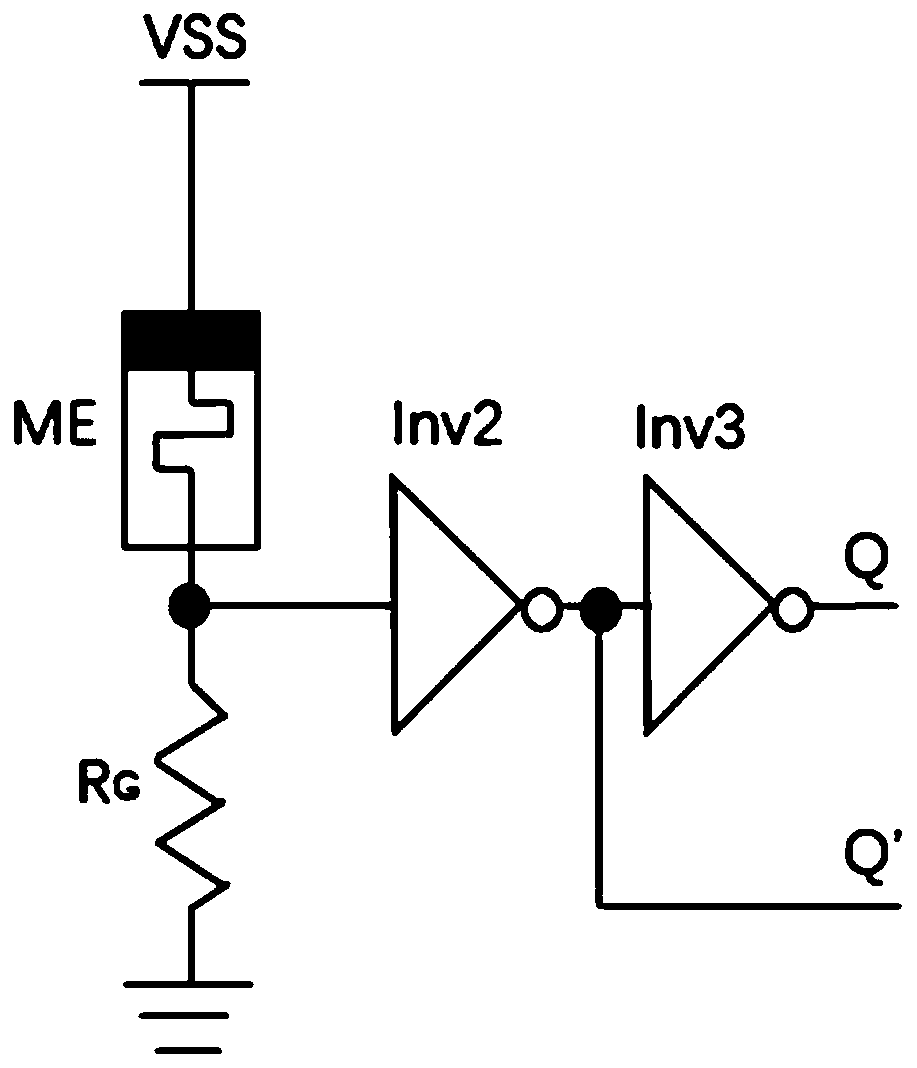

[0031] see Figure 4 As shown, the present invention relates to a level-triggered D flip-flop circuit based on resistive memory, comprising a MOSFET tube M1, a first memristor ME1, a resistor R G , the first inverter INV1 and the second inverter INV2;

[0032] The source of the MOSFET M1 is electrically connected to the input signal D, the gate of the MOSFET M1 is electrically connected to the clock pulse signal CP, and the drains of the MOSFET M1 are respectively electrically connected to the first memristor ME1 positive pole, resistor R G One terminal of the first inverter INV1 and the input terminal of the first inverter INV1, the output terminal of the first inverter INV1 is electrically connected to the input terminal of the second inverter INV2, and the output terminal of the second inverter INV2 is electrically The negative pole of the first memristor ME1 is electrically connected to the output terminal of the NAND logic circuit for auxiliary setting thereof, and one ...

Embodiment 2

[0046] see Figure 10 As shown, the present invention also relates to another level-triggered D flip-flop circuit based on resistive memory, including a MOSFET tube M1, a first memristor ME1, a resistor R G , the first inverter INV1, the second inverter INV2 and the fourth inverter INV4;

[0047] The source of the MOSFET M1 is electrically connected to the input signal D, the gate of the MOSFET M1 is electrically connected to the output terminal of the fourth inverter INV4, and the input terminal of the fourth inverter INV4 is electrically connected to The clock pulse signal CP, the drain of the MOSFET M1 is electrically connected to the anode of the first memristor ME1 and the resistor R G One terminal of the first inverter INV1 and the input terminal of the first inverter INV1, the output terminal of the first inverter INV1 is electrically connected to the input terminal of the second inverter INV2, and the output terminal of the second inverter INV2 is electrically The ne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More