Semiconductor device

A semiconductor and device technology, applied in the field of three-dimensional stacked semiconductor devices, can solve problems such as interference, unfavorable 3D integrated circuit integration and promotion, and achieve the effect of reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

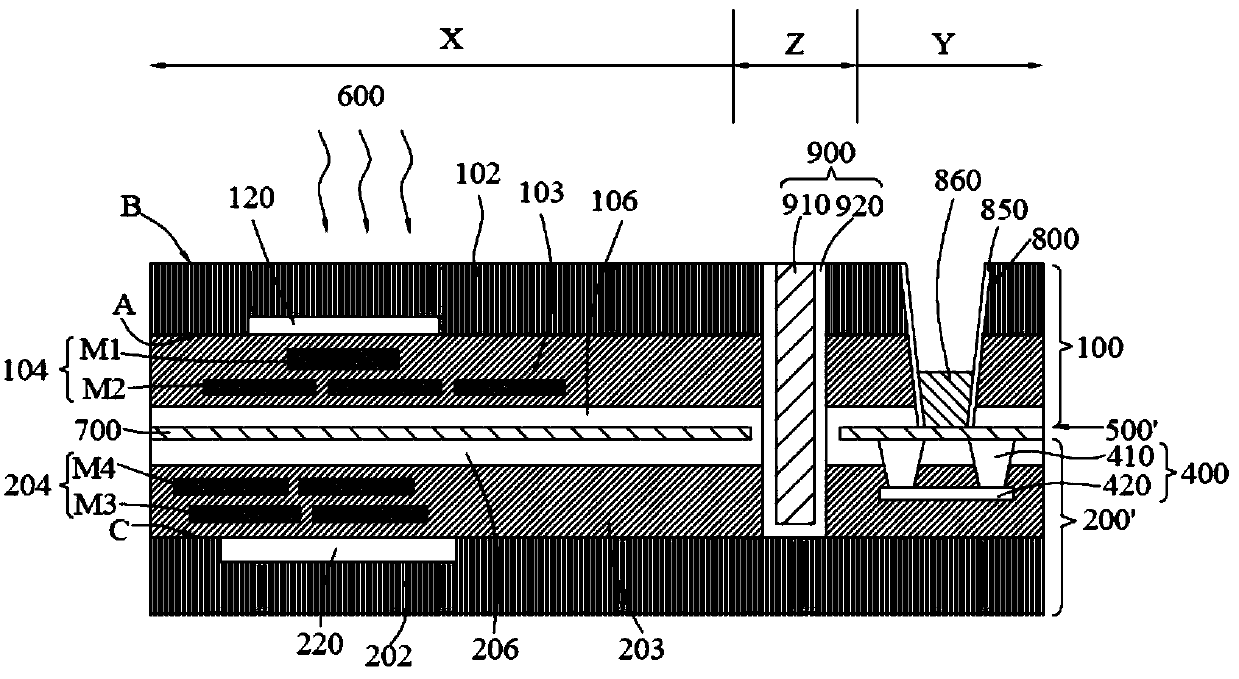

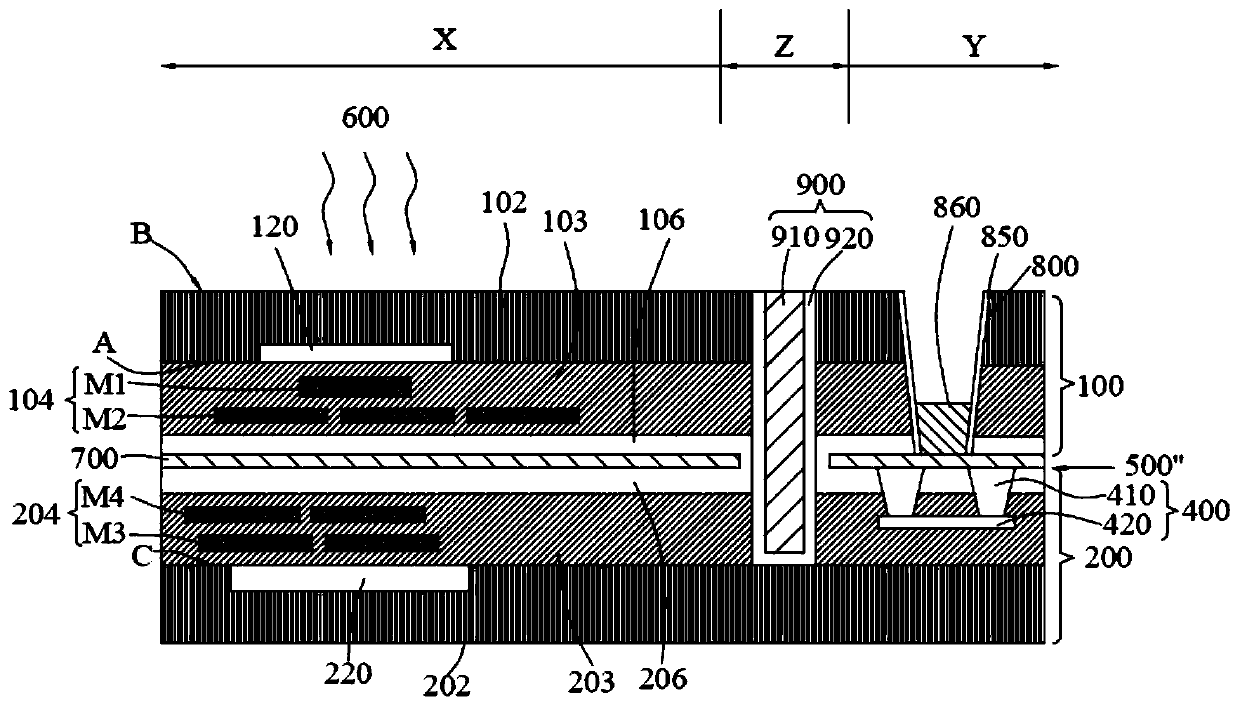

Embodiment Construction

[0025] The following descriptions of the various embodiments refer to the accompanying drawings to illustrate specific embodiments in which the invention may be practiced. The directional terms mentioned in the present invention, such as [top], [bottom], [top], [bottom], [left], [right], [inside], [outside], [side], etc., are only for reference The orientation of the attached schema. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention. In the figures, similar elements are denoted by the same reference numerals.

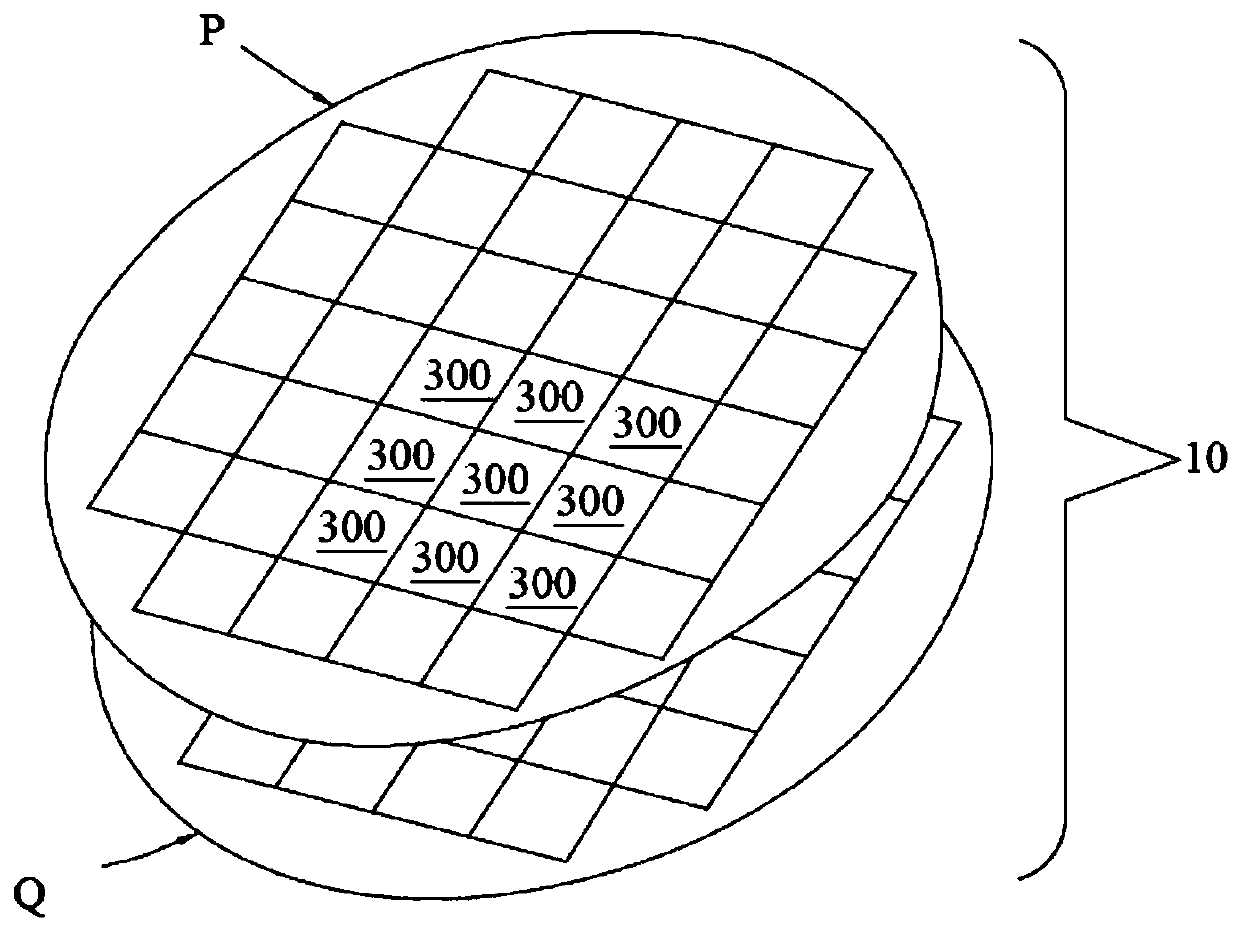

[0026] figure 1 is an exploded view of the three-dimensional integrated circuit 10 of the present invention. see figure 1 , the three-dimensional integrated circuit 10 is formed by stacking a first integrated circuit wafer (IC wafer) P and a second integrated circuit wafer Q. The first integrated circuit die P and the second integrated circuit die Q may include silicon, gallium ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More