Preparation method of rewiring layer and semiconductor structure

A technology for rewiring layers and semiconductors, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of high cost, long time, and complex RDL process, avoid grooves, improve Flatness, the effect of reducing process risk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

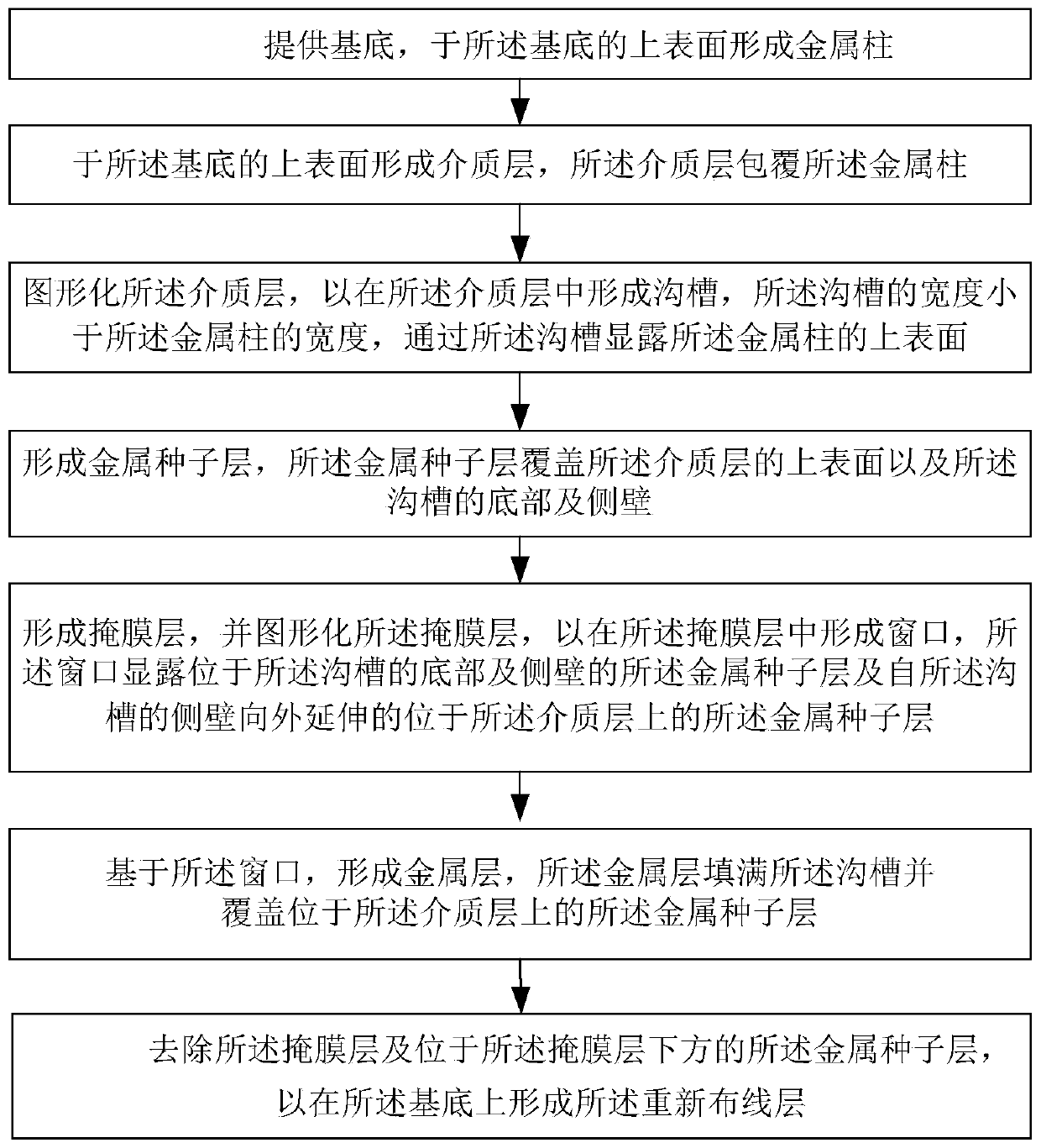

[0059] like figure 1 , this embodiment provides a method for preparing a rewiring layer, comprising the following steps:

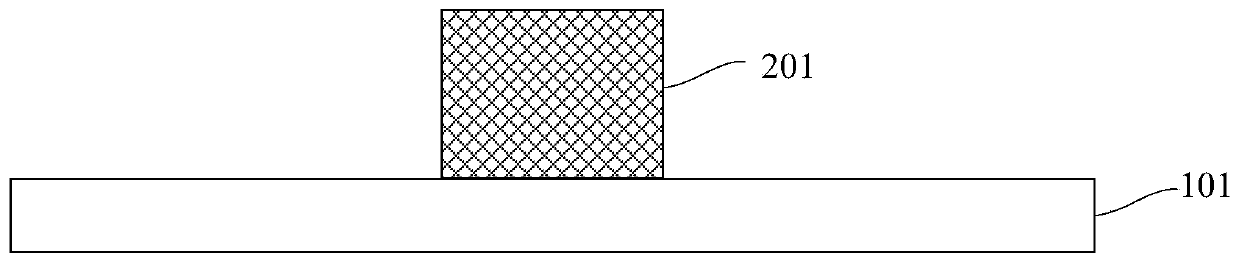

[0060] providing a base, and forming metal pillars on the upper surface of the base;

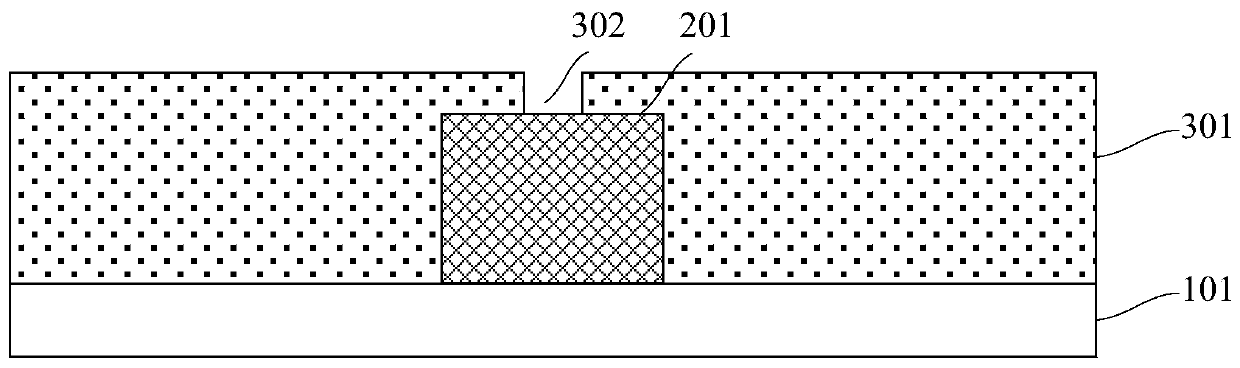

[0061] forming a dielectric layer on the upper surface of the substrate, the dielectric layer covering the metal pillar;

[0062] patterning the dielectric layer to form a groove in the dielectric layer, the width of the groove is smaller than the width of the metal pillar, and the upper surface of the metal pillar is exposed through the groove;

[0063] forming a metal seed layer, the metal seed layer covering the upper surface of the dielectric layer and the bottom and sidewalls of the trench;

[0064] forming a mask layer, and patterning the mask layer to form windows in the mask layer that expose the metal seed layer at the bottom and sidewalls of the trench and from the trench the metal seed layer on the dielectric layer with the sidewalls of the groove extending...

Embodiment 2

[0092] like Figure 7a , this embodiment also provides a semiconductor structure, the semiconductor structure includes: a base 101 and a rewiring layer, and the rewiring layer is located on the upper surface of the base 101 . Wherein, the rewiring layer includes: metal pillars 201, the metal pillars 201 are located on the upper surface of the substrate 101; a dielectric layer 301, the dielectric layer 301 is located on the upper surface of the substrate 101, and the dielectric layer 301 Covering the metal pillar 201, and the dielectric layer 301 includes a groove 302, the width of the groove 302 is smaller than the width of the metal pillar 201, and the upper surface of the metal pillar 201 is exposed through the groove 302. surface; a metal seed layer 401, the metal seed layer 401 covers the upper surface of the dielectric layer 301 and the bottom and sidewalls of the trench 302; a metal layer, the metal layer fills the trench 302 and covers The metal seed layer 401 located ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More