Digital signal processor layout distribution positioning method

A digital signal and positioning method technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of lack of applicability, single function, time-consuming and high cost of reverse analysis methods, and achieve The effect of solving the problem of layout positioning, simple technical thinking, and reducing time and funding costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the purpose, technical solution and advantages of the present invention clearer, the technical details of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments. It should be noted that the specific examples are only used to explain the present invention, not to limit the present invention.

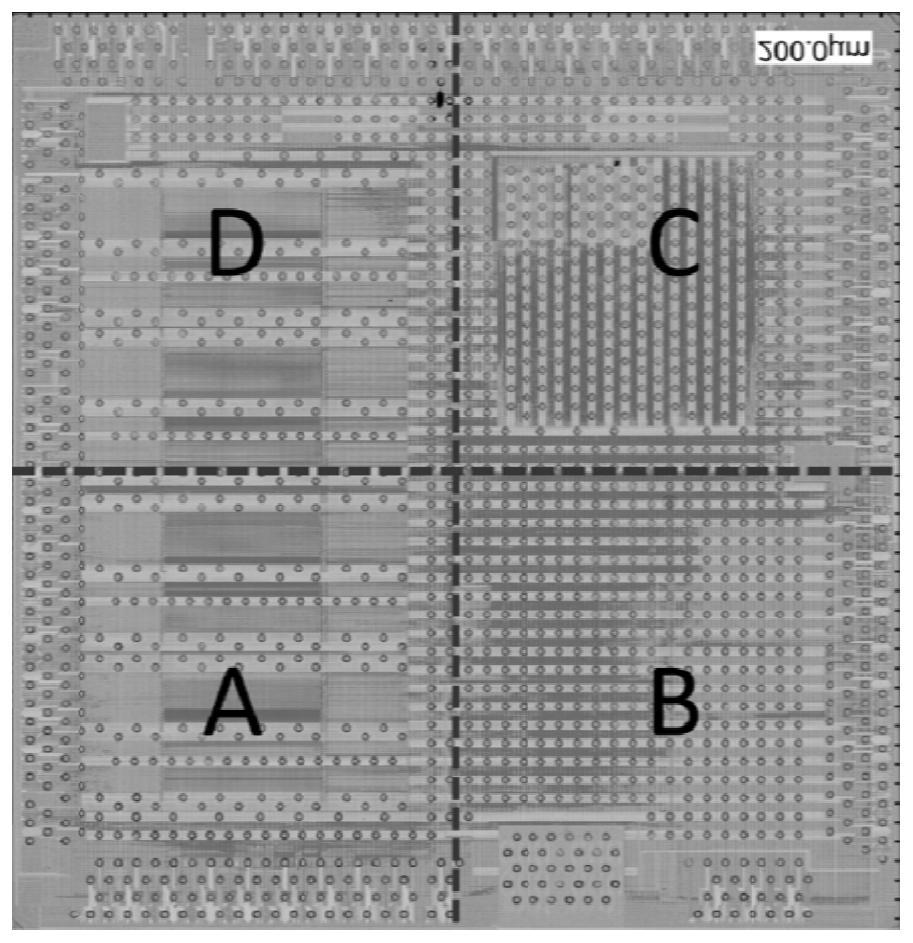

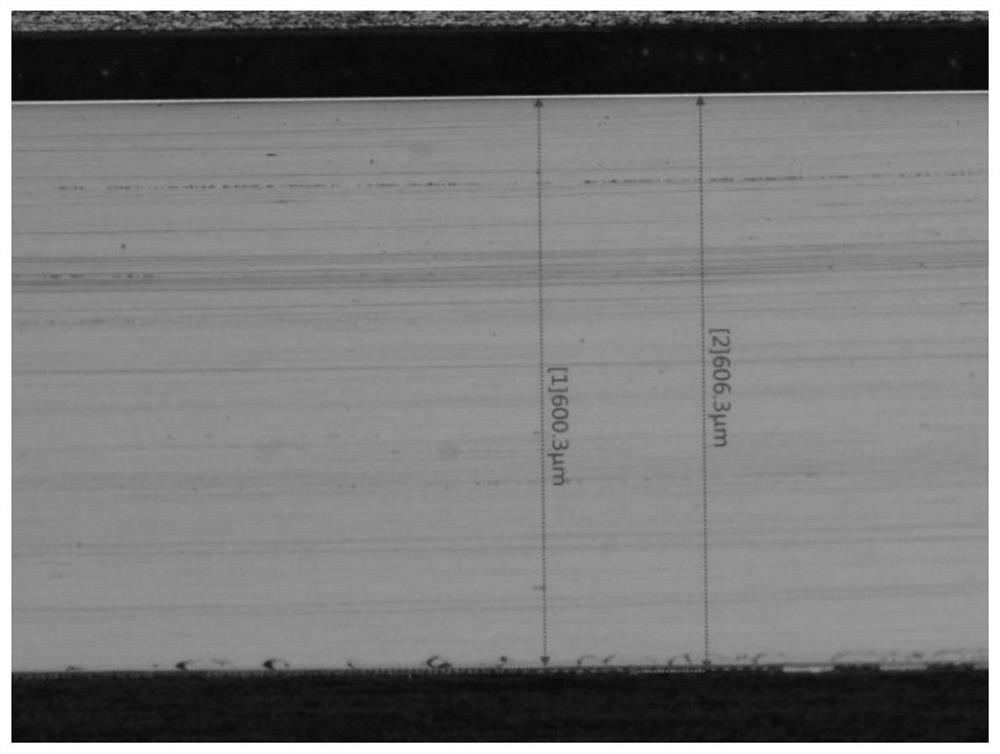

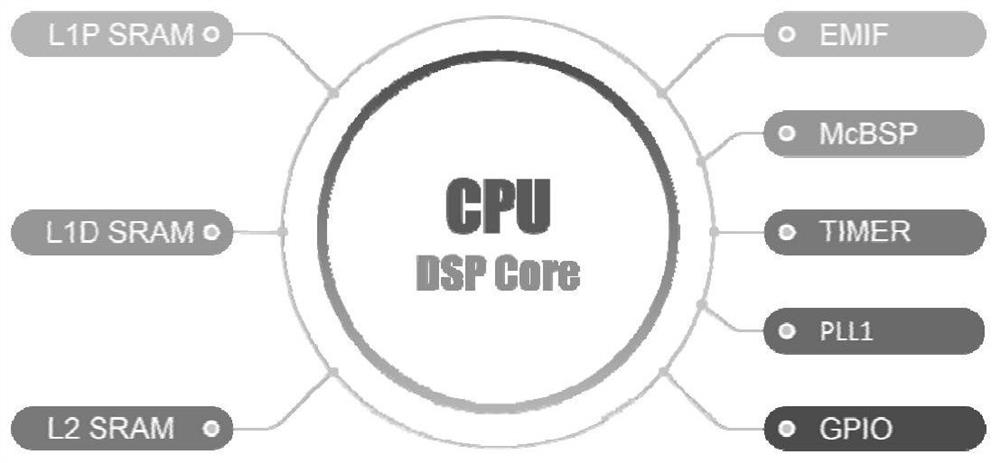

[0033] For ultra-large-scale integrated circuits, especially digital signal processors, the present invention proposes a method for locating the layout distribution of digital signal processors based on the experimental results of heavy ion micro-beams or laser micro-beams combined with chip pin distribution. The method of the present invention is combined with a DSP test system, by carrying out heavy ion micro-beam or laser micro-beam experiments, scanning the layout of the unpackaged DSP chip, and marking the sensitive points where Single Event Effect (SEE) occurs in different modules and effect type....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More