Modeling method of MOS device

A technology of MOS devices and modeling methods, applied in special data processing applications, CAD circuit design, etc., can solve problems such as no longer applicable, parasitic inductance can not be ignored, etc., and achieve the effect of wide application range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0034] A kind of modeling method of MOS device provided by the invention comprises the following steps:

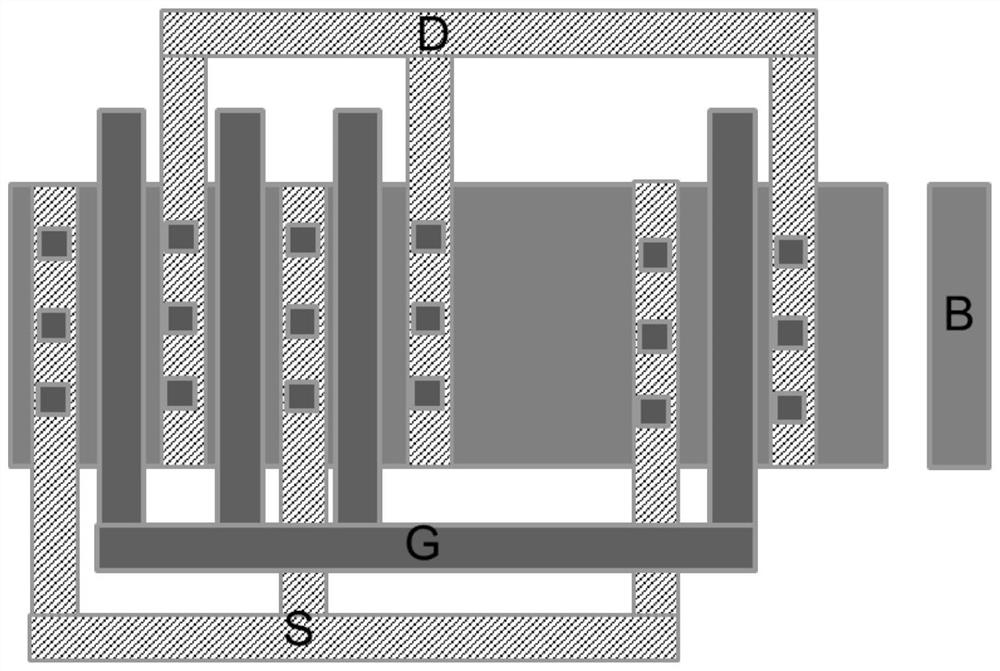

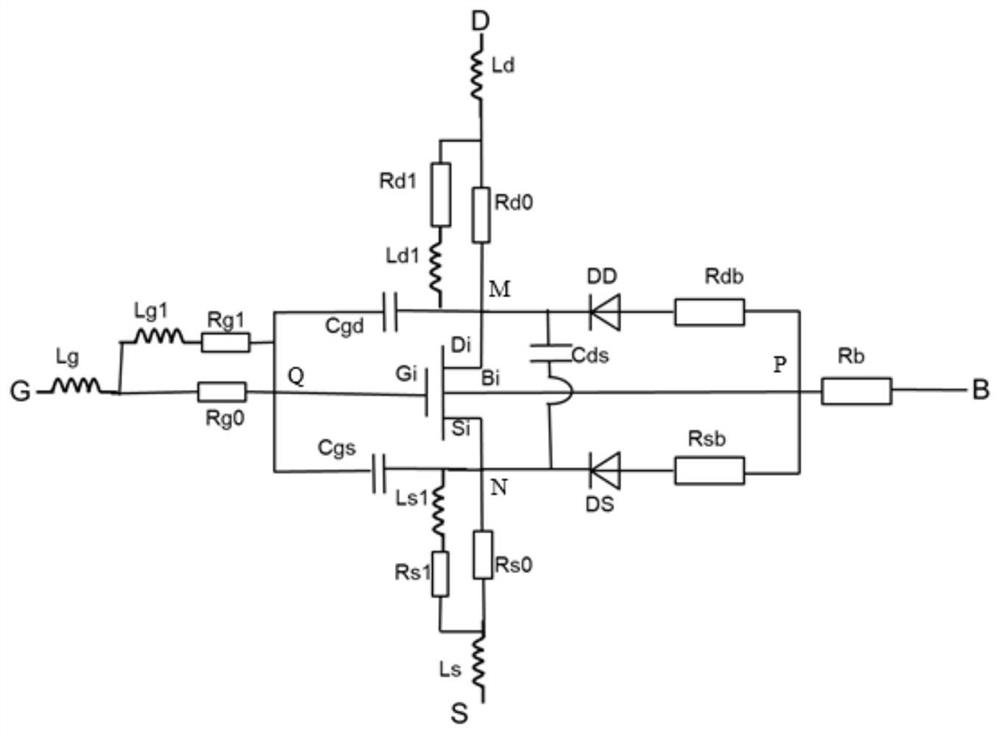

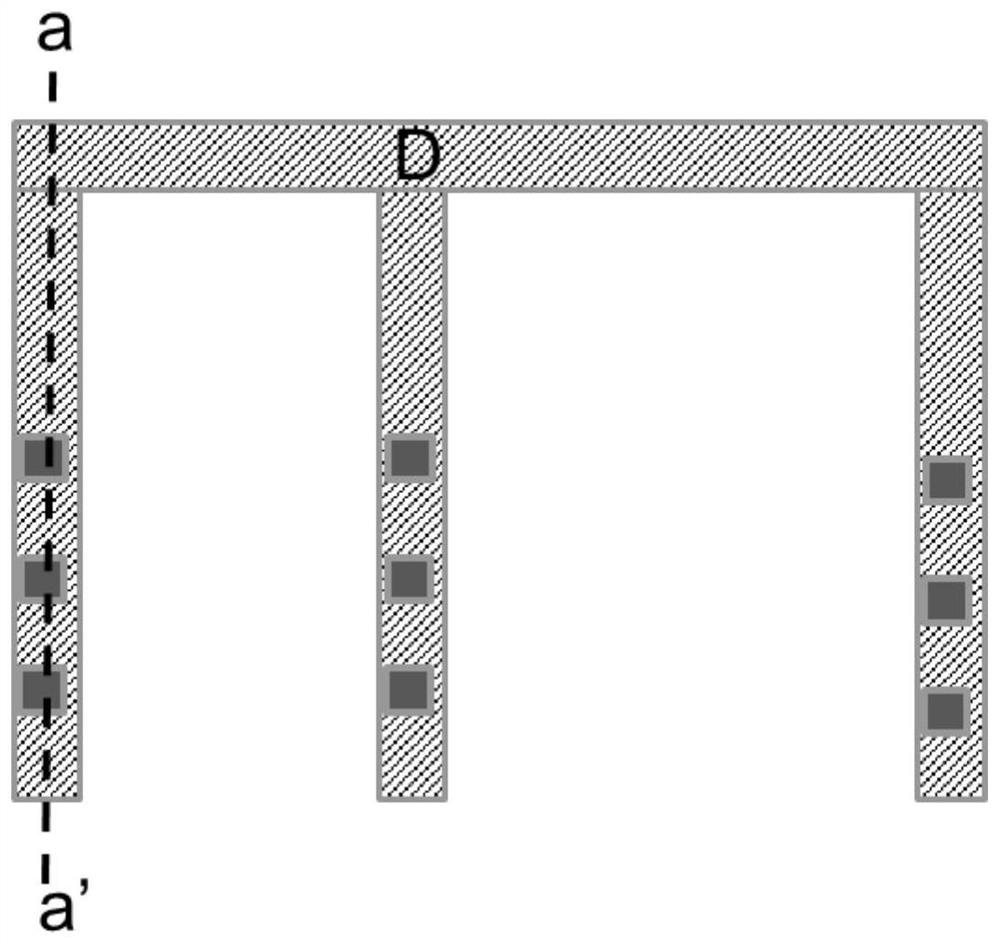

[0035] S01: Construct the model circuit of the MOS device, where the layout structure of the MOS device is as attached figure 1 As shown, including source S, gate G, drain D and substrate B, the corresponding model circuit includes intrinsic transistor, substrate parasitic resistance, parasitic capacitance, parasitic diode, gate parasitic resistance inductance network, source pole parasitic resistance inductance network and drain parasitic resistance inductance network. On the basis of the general structure, the present invention adds a new topological connection structure to the parasitic elements of the gate, source ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More