Bit line driving structure and three-dimensional memory structure

A driving structure and driving device technology, which is applied in the direction of electric solid-state devices, semiconductor devices, electrical components, etc., and can solve problems such as the drop of withstand voltage value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

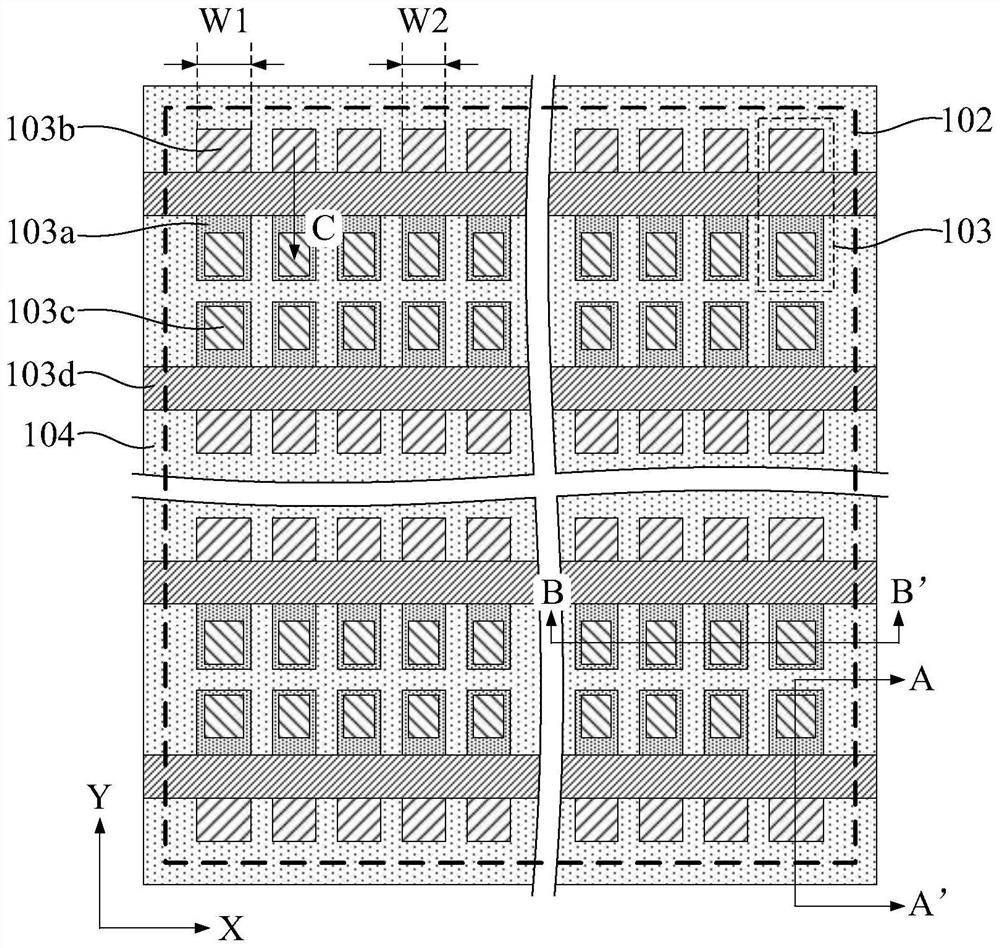

[0067] see Figure 1 to Figure 6 , this embodiment provides a bit line driving structure, characterized in that: comprising:

[0068] The first substrate 101 has a first surface and a second surface opposite to each other;

[0069] A driving device array 102 formed on the first surface side of the first substrate 101, the driving device array 102 is composed of a plurality of driving devices 103 arranged;

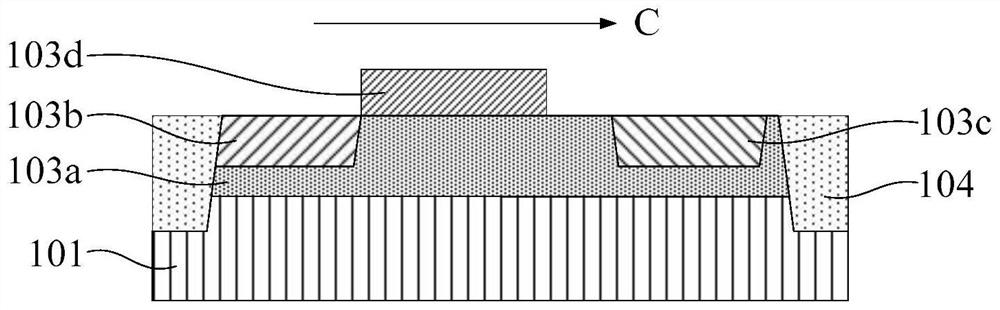

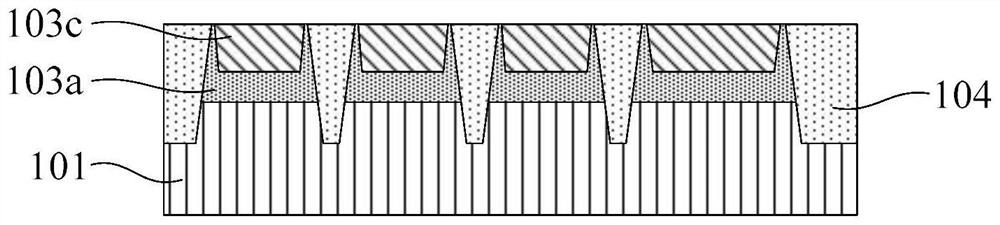

[0070] The driving device 103 includes an active device region 103a formed in the first substrate 101, a source region 103b and a drain region 103c formed in the active device region 103a, and an active device region 103c formed in the active device region 103a. The gate structure 103d above the region 103a; the source region 103b and the drain region 103c are respectively located on both sides of the gate structure 103d; there are intervals between the plurality of active device regions 103a;

[0071] The direction in which the source region 103b points to the drain regi...

Embodiment 2

[0085] see Figure 6 , this embodiment provides a three-dimensional memory structure, characterized in that it includes:

[0086] The driving structure for improving the withstand voltage value of the bit line driving circuit as described in the first embodiment;

[0087] a second substrate 106, which has a third surface and a fourth surface oppositely disposed;

[0088] A memory array structure formed on the third surface of the second substrate 106, the memory array structure comprising a plurality of memory strings 108 and a bit line structure 109 connecting the memory strings 108;

[0089] As in the bit line driving structure described in Embodiment 1, the bit line driving structure is connected to the bit line structure 109 .

[0090] As an example, there are multiple storage strings 108 formed in the stack structure 107 . The stack structure 107 includes alternately stacked gate layers 107a and isolation layers 107b, and a top selection gate 107c at the top and a bott...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com