Three-dimensional memory device and forming method thereof

A three-dimensional storage and device technology, applied in semiconductor devices, electric solid state devices, electrical components, etc., can solve the problems of structural instability, storage capacity and manufacturing cost and structural stability, device size contradiction, cost increase, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

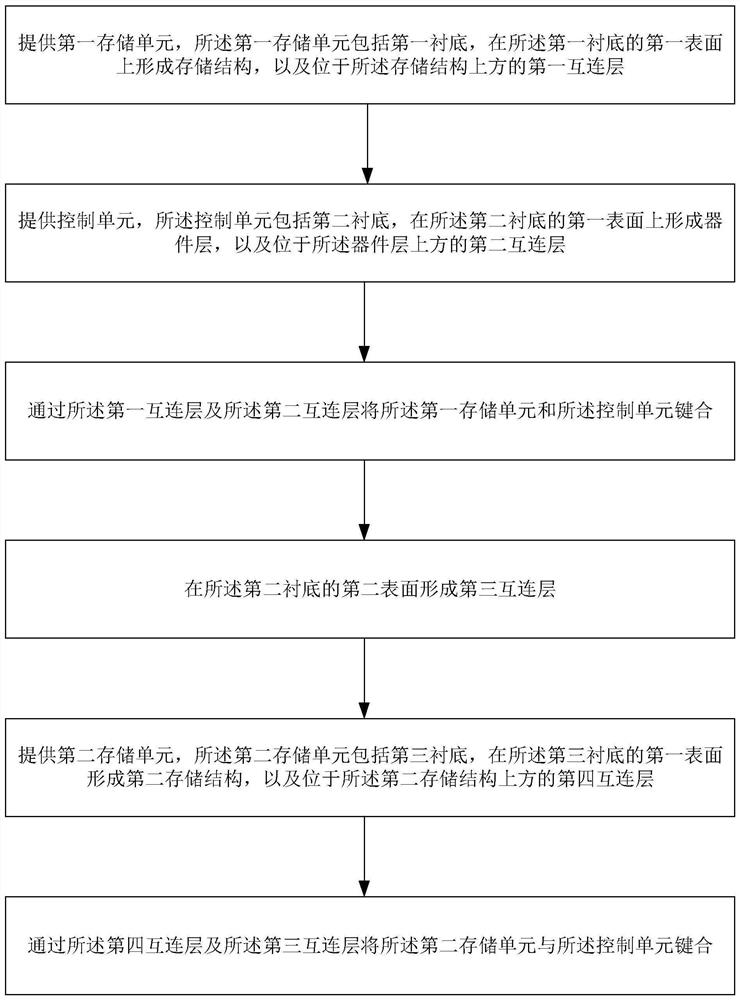

[0151]This embodiment provides a method of forming a three-dimensional memory device, such asfigure 1 As shown, the method includes the following steps:

[0152]Step S101: Provides a first storage unit including a first substrate, forming a storage structure on the first surface of the first substrate, and a first interconnection located above the storage structure. ;

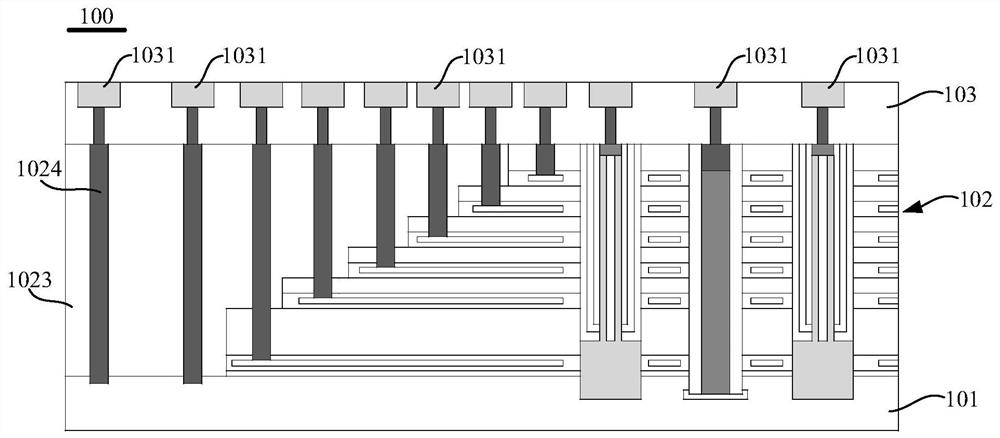

[0153]Referfigure 2 The first storage unit 100 provides a 3D NAND storage unit including a first substrate 101, a storage structure 102 is formed over the first substrate 101, and a first interconnect layer 103 is formed over the storage structure. Specifically, the following method is formed:

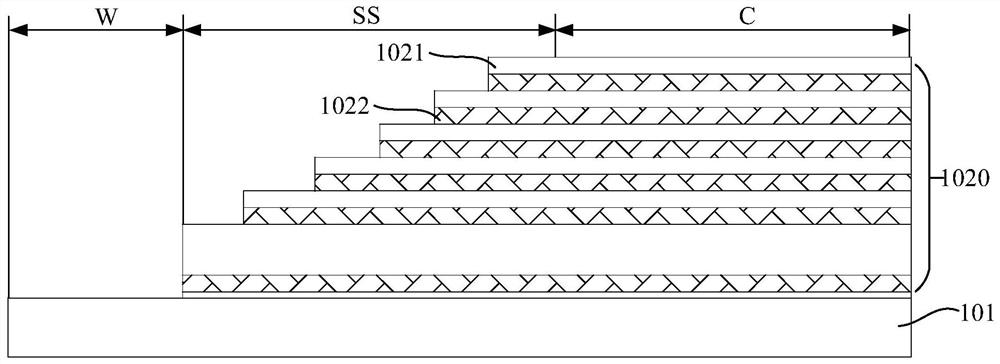

[0154]Such asimage 3 As shown, first, the first substrate 101 is provided, the first substrate having a first surface (e.g., a substrate front) and a second surface (such as a substrate back side), as an example, the first substrate 101 can be based on the actual actual Demand is selected, for example, may include a silicon substrate,...

Embodiment 2

[0185]This embodiment also provides a method of forming a three-dimensional memory device, and is not described in the same manner as the first example, and the difference is:

[0186]ReferFigure 12 In this embodiment, the source layer of the array is stored in the array of arrays.Front connectionTo the control circuit of the control unit, the array co-source contact is not repeated from the second surface of the first substrate and / or the third substrate. In this embodiment, the source layer can achieve a connection between the source layer and the control unit by the peripheral contact 402 formed in the substrate of the first storage unit and the second memory cell. Or in an alternative embodiment, here referencefigure 2 Further, the first contact 1031 formed at the top of the common source line 105 is in contact with the top cycle, and the source layer is connected to the control unit by a common source line, and the front side of the source layer is connected to the control unit ...

Embodiment 3

[0190]This embodiment also provides a method of forming a three-dimensional memory device, and is not described in the same place as in Example 2, and the difference is:

[0191]Such asFigure 13 As shown in the present embodiment, the back surface of the substrate of the first substrate 101 of the first storage unit 100 does not form a contact pad, and a contact pad 502 is formed only on the back surface of the third substrate 301. The array source layer of the memory cell and the leader of the control unit are realized by contact pad 502.

[0192]This embodiment is also providedFigure 13 The three-dimensional memory device shown. The memory device implements the storage unit and the leader of the control unit at a lower number of pads, which facilitates the integration of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More