FPGA stream data verification method and device

A technology for data verification and verification methods, which is applied in electrical digital data processing, data representation error detection/correction, error detection coding, etc. error, ensuring completeness and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

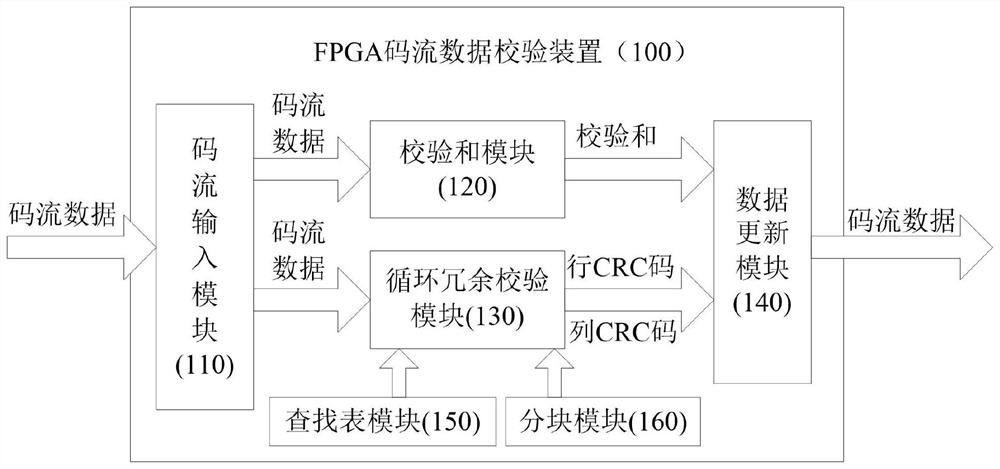

[0036] This embodiment relates to a method for verifying FPGA code stream data and a device for verifying FPGA code stream data. Both the FPGA code stream data verification method and the FPGA code stream data verification device are used to process the code stream data to be downloaded to the FPGA chip, which is hereinafter referred to as the verification process at the sending end.

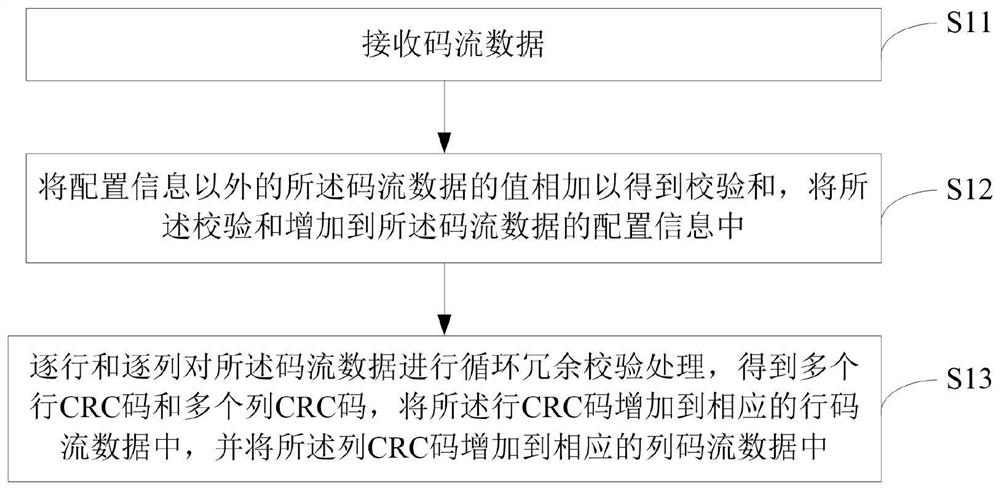

[0037] figure 1 It is a schematic flowchart of an FPGA code stream data verification method for processing code stream data at a sending end in an embodiment of the present invention. see figure 1 , the FPGA code stream data checking method of the present embodiment comprises the following steps:

[0038] Step S11, receiving code stream data;

[0039] Step S12, adding the values of the code stream data other than the configuration information to obtain a checksum, and adding the checksum to the configuration information of the code stream data;

[0040] Step S13, performing cyclic redundan...

Embodiment 2

[0058] This embodiment relates to a method for verifying FPGA code stream data. The method for verifying the FPGA code stream data is used to process the code stream data at the receiving end. Here the FPGA chip can be used as the receiving end. After the code stream data is downloaded to the FPGA chip, it is first stored in the random access memory (RAM) configured on the FPGA chip. In order to check whether the code stream data is wrong in the storage and transmission process of the sending end, the FPGA chip carries out the receiving end verification to the code stream data stored in the RAM, and the verification process of the receiving end can be passed through the control module (such as MCU) of the FPGA chip. , microcontroller) is implemented using software programs and / or programmable logic resources of FPGA chips.

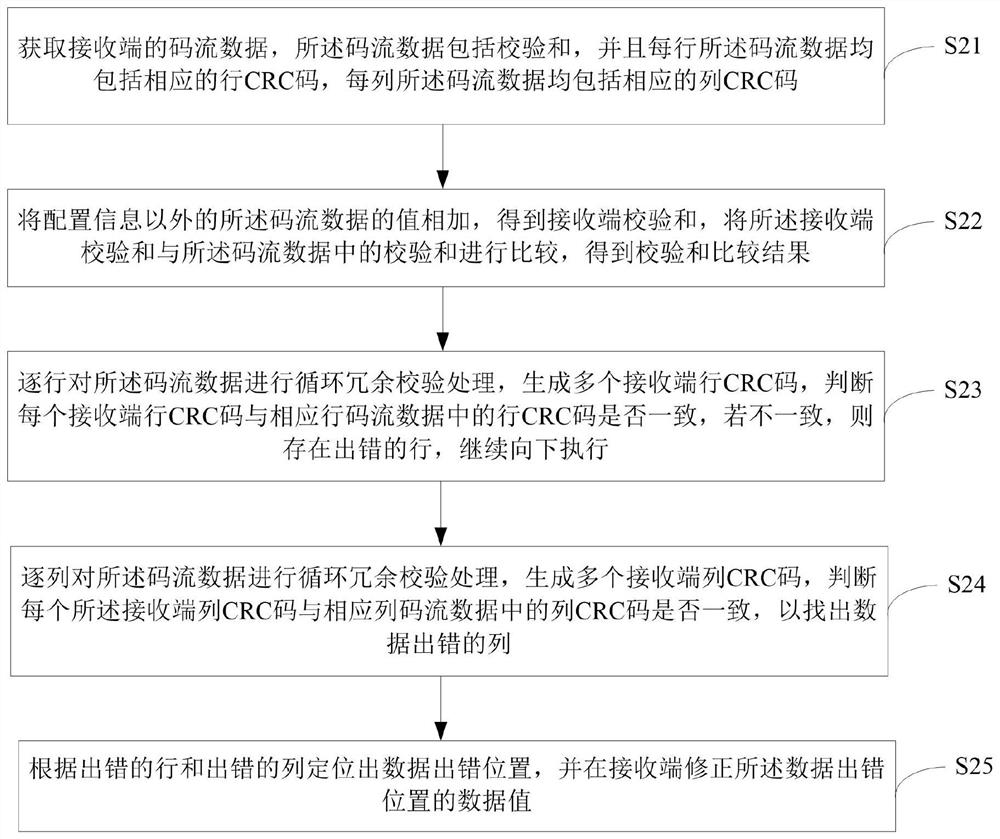

[0059] image 3 It is a schematic flowchart of an FPGA code stream data verification method for processing code stream data at a receiving end in an em...

Embodiment 3

[0072] This embodiment relates to a method for verifying FPGA code stream data. The method for verifying the FPGA code stream data is used to process the code stream data at the receiving end.

[0073] Figure 4 It is a schematic flowchart of an FPGA code stream data verification method for processing code stream data at a receiving end in an embodiment of the present invention. see Figure 4 , the FPGA code stream data checking method of the present embodiment comprises the following steps:

[0074] Step S31: Obtain the code stream data at the receiving end, the code stream data includes a checksum, and each row of the code stream data includes a corresponding row CRC code, and each column of the code stream data includes a corresponding column CRC code ;

[0075] Step S32: Add the values of the code stream data other than the configuration information to obtain the checksum at the receiving end, compare the checksum at the receiving end with the checksum in the code st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More