Method for suppressing neutral-point potential balance and common-mode voltage of three-phase three-level inverter

A three-level inverter and common-mode voltage technology, which is applied in the direction of electrical components, output power conversion devices, and conversion of AC power input to DC power output, can solve the problem of high switching loss, reduce switching loss, reduce The effect of harmonics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0177] The method of the present invention will be clearly and completely described below in conjunction with the accompanying drawings.

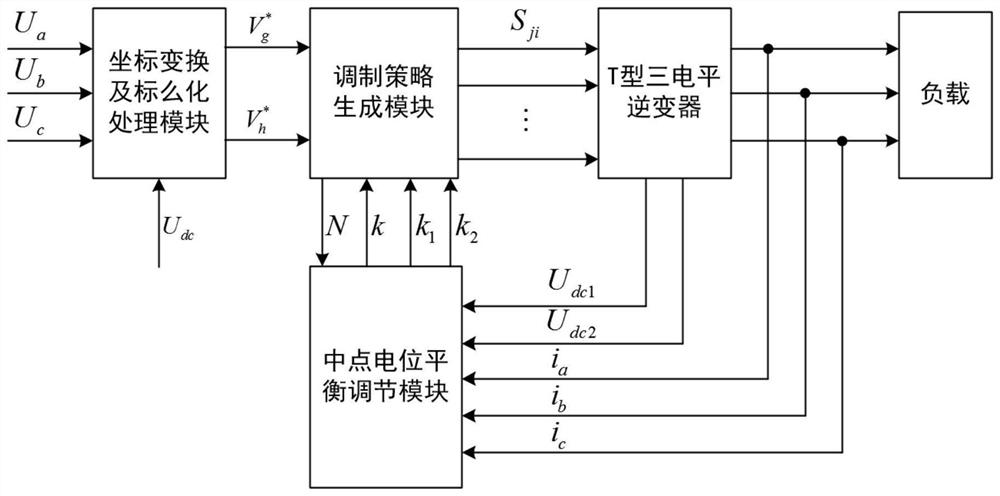

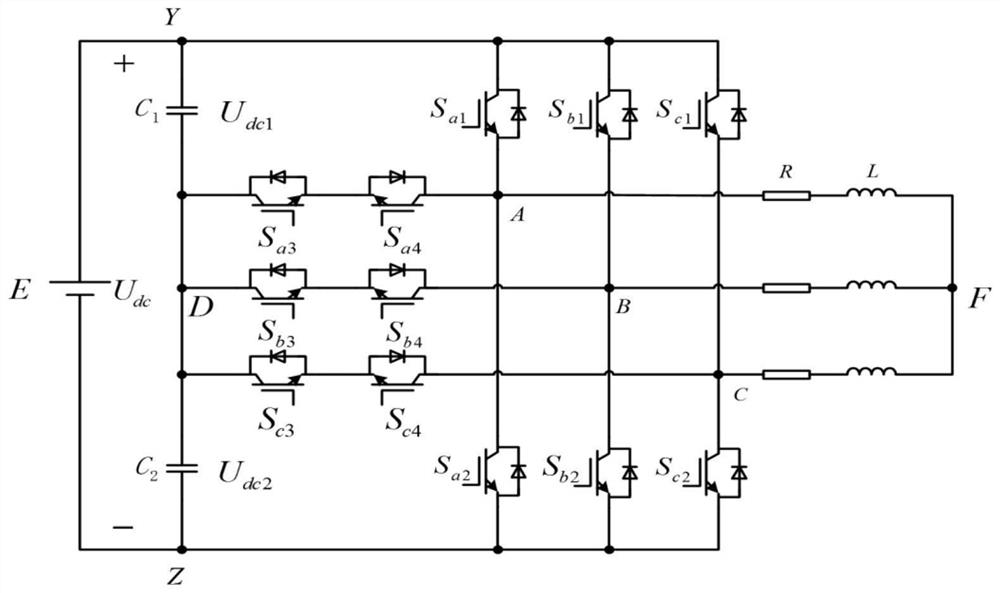

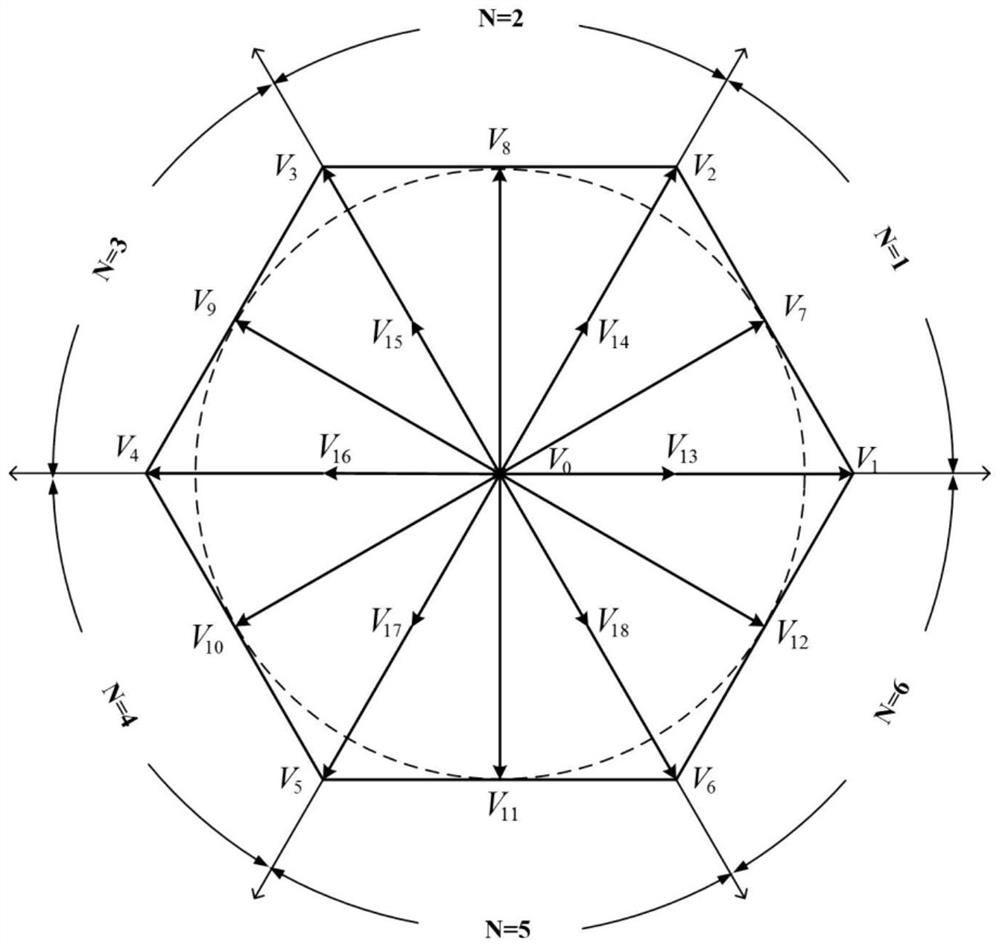

[0178] Figure 5 It is a hardware schematic diagram of an embodiment of a T-type three-level inverter midpoint potential balance and common-mode voltage suppression method. The embodiment selects DSP+FPGA platform to realize. Among them, the DSP model is TMS320F28335, and the FPGA model is EP2C20F48418N. The reference voltage vector V is generated by DSP ref The g-axis component of h axis component Pass the g-axis component with address XA=0 Pass the h-axis component with address XA=1 Send to FPGA through 16-bit data bus XD[15:0], and write signal by external interface or external interface area strobe signal Trigger the FPGA to acquire data. Then, the acquisition of the sector number N, the small area number n, and the number r of the sector basic voltage vector in the sequence G is completed in the FPGA, and the sampling ci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com