Segmentation and verification method, device, electronic device, storage medium

A technology to be divided and divided and processed, applied in the fields of electrical digital data processing, computer-aided design, instruments, etc., can solve the problems of division, time-consuming verification, increasing algorithm complexity, and low efficiency of chip design division and verification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

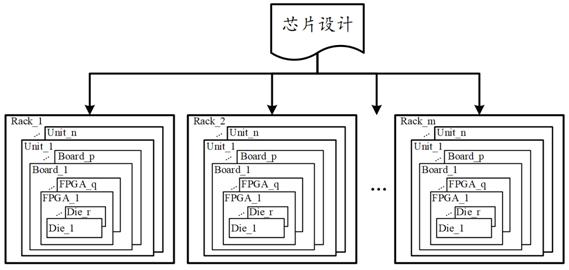

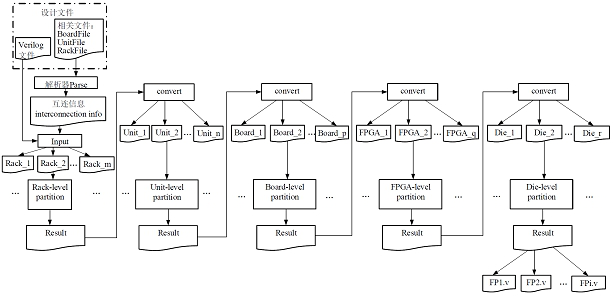

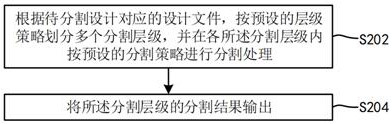

[0099] Example 1: Rack hierarchical segmentation.

[0100] The basic unit of the Rack level is each Rack, which can be read into the file RackFile describing the Rack unit resources, port information, and interconnection information; then, the corresponding hypergraph data is designed, and the hypergraph data includes the resources required by each circuit node and the network. Connection relationship, node constraints and other information; Next, allocate the nodes with larger resource requirements among the nodes to different Racks as fixed nodes (fix nodes) in the Rack, and then consider the interconnection constraints between Racks, Carry out Rack level segmentation according to the minimum cut optimization objective, and obtain the segmentation results.

[0101] When interconnection constraints need to be considered during segmentation, it is necessary to consider the bit width characteristics of the interconnection interface between Racks, for example, a bidirectional tr...

example 2

[0108] Example 2: Unit level division.

[0109] The basic unit of the Unit level is each Unit, which can be read into the file UnitFile describing Unit unit resources, port information, and interconnection information, and the fixed node allocation information in each Unit obtained by Rack level segmentation; then, considering the interconnection constraints between Units, According to the minimum cut optimization objective, the Unit level segmentation is carried out to obtain the segmentation results. Similarly, when considering interconnection constraints, it is necessary to consider the bit width characteristics of the interconnection interface between Units.

[0110] After the division is completed, cross-Unit nets can be determined according to the obtained division results, so that the drive nodes in these nets can be fixed in specific Board units at the level below the Unit, that is, the Board level. The specific allocation method can be as follows: sort the cross-Unit...

example 3

[0116] Example 3: Board level division.

[0117] The basic unit of the Board level is each Board, which can first be read into the file BoardFile describing the Board unit resources, port information, and interconnection information, and the fixed node allocation information in each Board obtained by the division of the Unit level; then, considering the interconnection constraints between the Boards, According to the minimum cut optimization objective, the Board level segmentation is carried out to obtain the segmentation results. Similarly, when considering interconnection constraints, it is necessary to consider the bit width characteristics of the interconnection interface between boards.

[0118] After the segmentation is completed, cross-Board nets can be determined according to the obtained segmentation results, so as to fix the driving nodes in these nets in specific FPGA units at the next level of the Board, that is, the FPGA level. The specific allocation method can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More