Wafer cutting method

A cutting method and wafer technology, applied in manufacturing tools, laser welding equipment, welding equipment, etc., can solve the problems of large lateral width of cutting lines, accumulation around notches, and difficulty in selecting etchants, so as to ensure cleanliness. smoothness and flatness, and the effect of improving the bonding effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

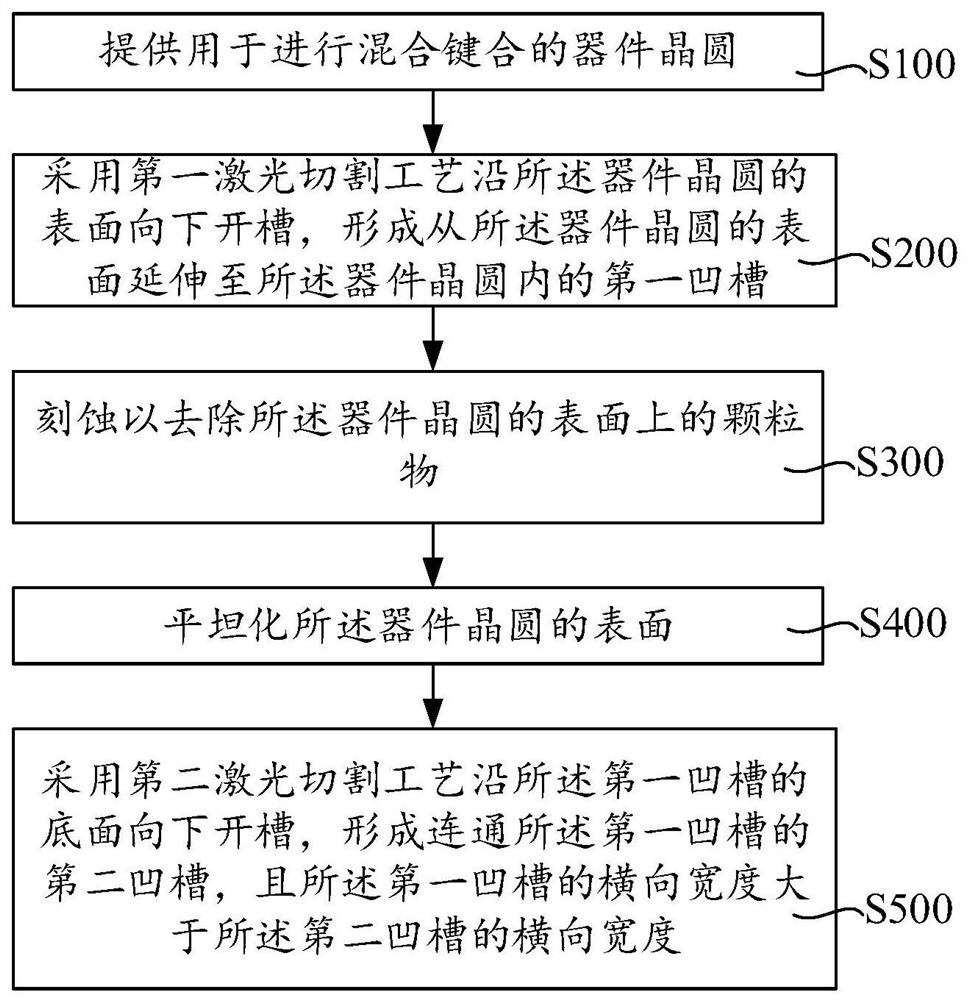

[0039] figure 1 A flow chart of the wafer cutting method provided in this embodiment. like figure 1 As shown, the wafer cutting method includes:

[0040] Step S100: providing a device wafer for hybrid bonding;

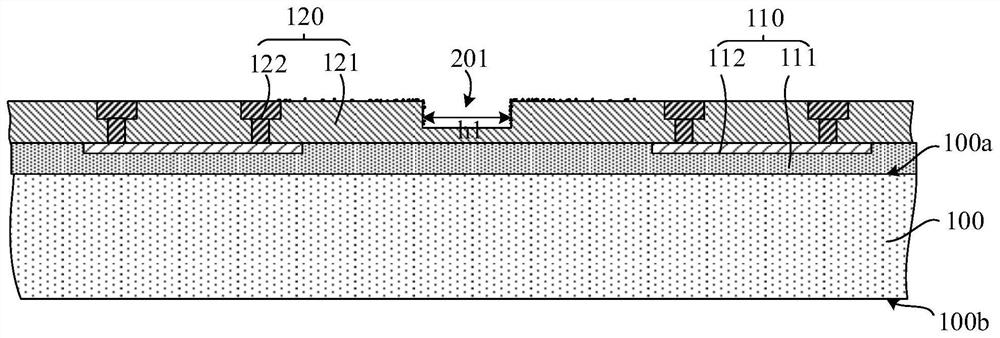

[0041] Step S200: using a first laser cutting process to grove downwards along the surface of the device wafer to form a first groove extending from the surface of the device wafer into the device wafer;

[0042] Step S300: etching to remove particles on the surface of the device wafer;

[0043] Step S400: planarizing the surface of the device wafer; and,

[0044] Step S500: Using a second laser cutting process to make grooves downward along the bottom surface of the first groove to form a second groove communicating with the first groove, and the transverse width of the first groove is larger than the first groove Lateral width of the second groove.

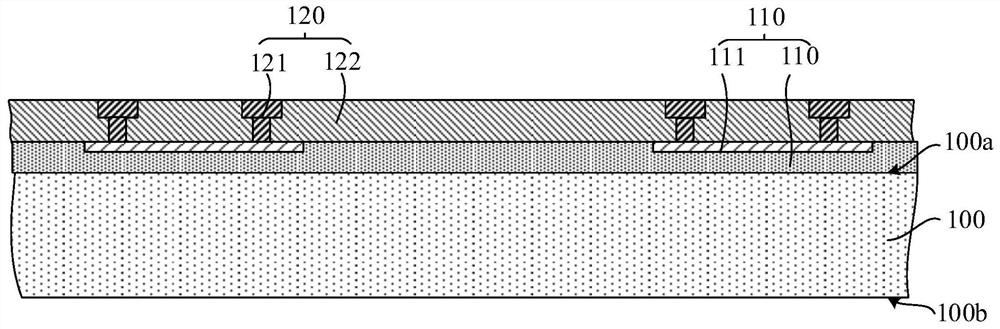

[0045] Figure 2a ~ Figure 2f A schematic structural diagram corresponding to corresponding steps of the wafer ...

Embodiment 2

[0070] image 3 A schematic diagram of the cutting lane 200 provided in this embodiment. like image 3 As shown, the difference from Embodiment 1 is that in this embodiment, when the second groove 202 is formed, the second groove 202 penetrates the mixing chamber downward along the bottom of the first groove 201 The bonding layer 120 , the interconnect structure layer 110 and the substrate 100 . In this way, the first groove 201 and the second groove 202 jointly penetrate the device wafer and form the dicing line 200, the step of forming the third groove 203 can be omitted, simplifying the process process.

Embodiment 3

[0072] Figure 4a Schematic diagram of the device wafer provided for this example. like Figure 4a As shown, the difference from Embodiment 1 is that in this embodiment, the device wafer is a device wafer for back-to-face hybrid bonding, and the interconnect structure layer 110 covers the front surface 100a of the substrate 100 , the hybrid bonding layer 120 covers the back surface 100b of the substrate 100 , and the interconnect structure layer 110 has a fourth groove 204 therein.

[0073] Optionally, the fourth groove 204 may be prepared before the hybrid bonding layer 120 of the device wafer is formed, thus, the preparation of the fourth groove 204 will not affect the hybrid bonding The cleanliness and flatness of layer 120 are adversely affected.

[0074] in particular, Figure 4b A schematic diagram of the cutting lane 200 provided in this embodiment. like Figure 4b As shown, the first groove 201 is located in the hybrid bonding layer 120, the second groove 202 ext...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Horizontal width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More