Read-write system and method compatible with two-dimensional structure data

A two-dimensional structure, data reading and writing technology, applied in the field of data processing, can solve problems such as slowing down the actual operation of the system, processing efficiency, etc., to achieve the effect of improving hit rate, improving operation efficiency, and accelerating throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

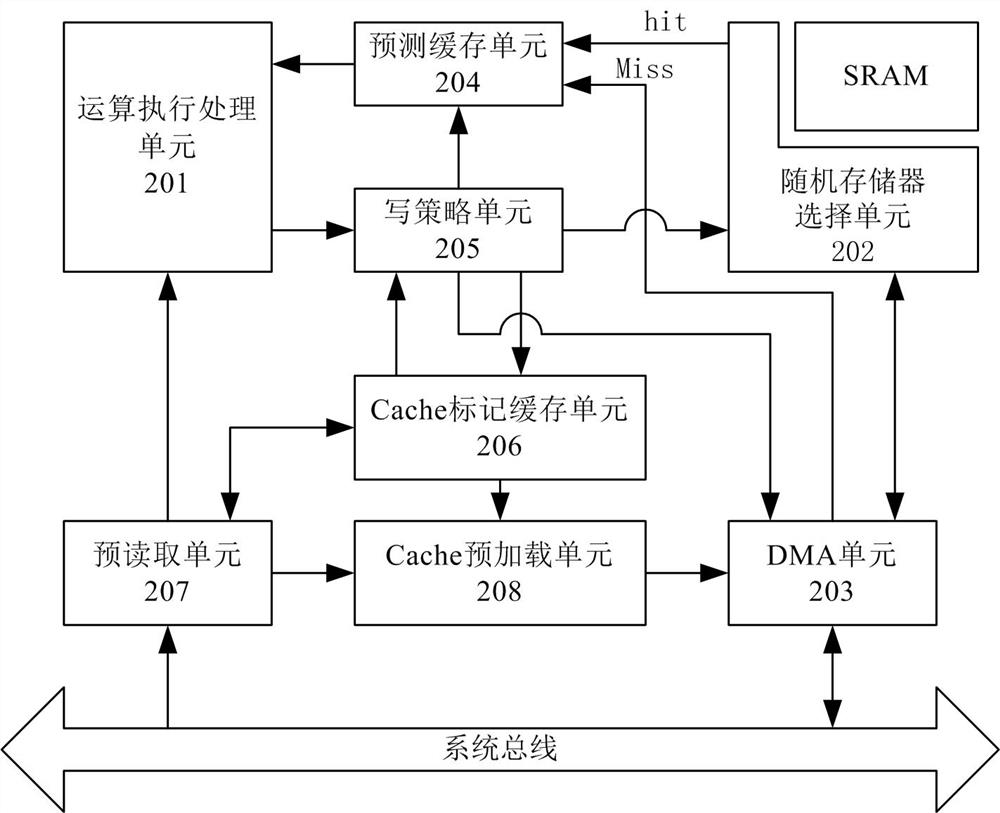

[0055] figure 2 It is a schematic diagram of a compatible two-dimensional structure data reading and writing system according to the present invention, such as figure 2 As shown, the compatible two-dimensional structured data reading and writing system of the present invention includes arithmetic execution processing unit (arithmetic execution unit) 201, random access memory selection unit (SRAM RW arbiter) 202, DMA unit 203, and prediction buffer unit (Prediction buffer) 204 , write strategy unit (write strategy) 205, Cache tag cache unit (Cache TAG buffer) 206, Cache preload unit (Cache preload) 207, and prefetch unit (prefetch) 208, wherein,

[0056] An arithmetic execution unit (arithmetic execution unit) 201 executes arithmetic instructions to read two-dimensional structure data from the predictive cache unit 204 to perform calculations, and sends the calculation results to the write strategy unit 205 .

[0057] The random memory selection unit (SRAM RW arbiter) 202 es...

Embodiment 2

[0066] Figure 4 For the flow chart of the method for reading and writing compatible two-dimensional structured data according to the present invention, reference will be made below Figure 4 , the method for reading and writing compatible two-dimensional structured data of the present invention is described in detail.

[0067] First, in step 401, the mapping structure of the Cache is determined, and the two-dimensional data is cache-mapped.

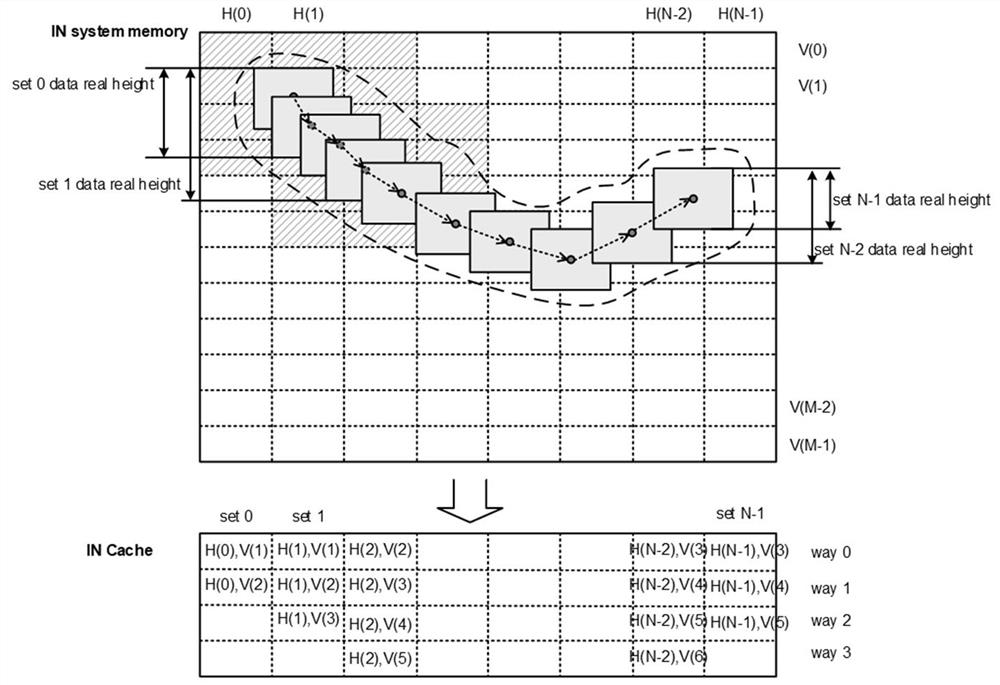

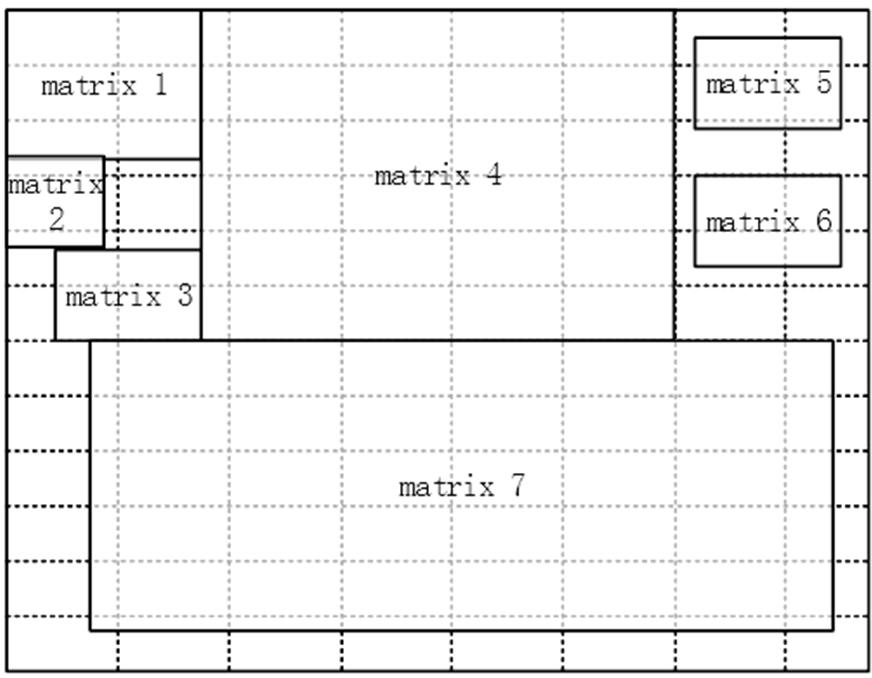

[0068] Such as figure 1 As shown, a data file in the system memory can be divided in a two-dimensional manner. Each line occupies a fixed number of bytes (bytes), which is recorded as stride, and the number of lines is recorded as lines. The dotted line is divided into squares, squares The width and height are tile_hsize and tile_vsize respectively. The physical address of the data file is file_addr, and the file size is file_size. The above parameters can be set as Cache registers. Register configurable values can be as follows: ...

Embodiment 3

[0097] The present invention also provides a compatible two-dimensional structure data reading and writing chip, including the above-mentioned compatible two-dimensional structure data reading and writing system, which efficiently loads the operation data into the cache, maximizes the use of the bandwidth for accessing external memory, and improves the access of the operation unit. The hit rate of the cache speeds up the throughput of the computing unit to obtain data, thereby making full use of the computing resources in the digital logic system of the chip, and at the same time making full use of the actual physical device SRAM resources of the Cache, which is compatible with the general n-way combination mapping (n-way set-associative mapping) way. .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com