Low-thickness current-withstanding SiC PIN diode and manufacturing method thereof

A current-resistant, low-thickness technology, used in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., to solve problems such as limited improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

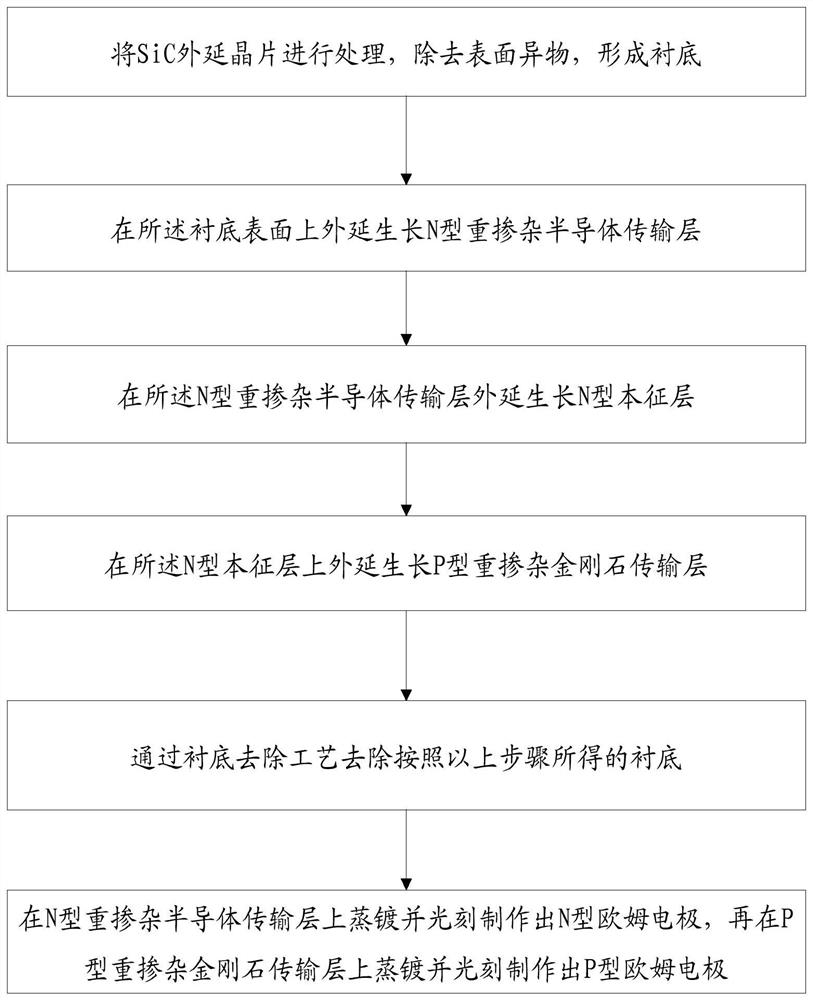

[0035] Such as Figure 1 to Figure 7 As shown, a method for manufacturing a low-thickness current-resistant SiC PIN diode of the present invention includes:

[0036] Step 1. Rinse the surface of the SiC epitaxial wafer with deionized water, and then soak it in a heated mixed washing solution for 1 minute to further remove foreign matter on the surface of the SiC epitaxial wafer to form a substrate; the mixed washing solution includes ammonia water, hydrogen peroxide, and deionized Ionized water;

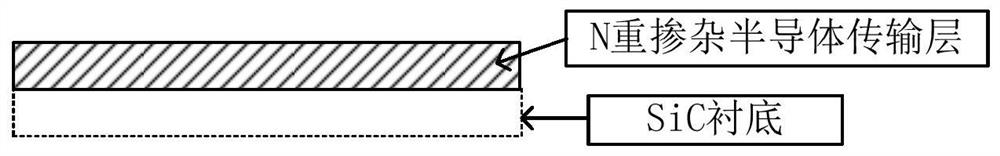

[0037] Step 2, epitaxially growing an N-type heavily doped semiconductor transport layer on the surface of the substrate;

[0038] Step 3, epitaxially growing an N-type intrinsic layer on the N-type heavily doped semiconductor transport layer;

[0039] Step 4. Epitaxially grow a P-type heavily doped diamond transport layer on the N-type intrinsic layer, and the doping concentration of the P-type heavily doped diamond transport layer is 2*10 19 cm -3 , the thickness of the P-type ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More