GPU batch matrix multiplication accelerator and processing method thereof

A technology of matrix multiplication and processing method, which is applied in the direction of processing input data, electrical digital data processing, digital data processing components, etc. Versatility and scope of application, improving efficiency and speed, and accelerating the effect of execution efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

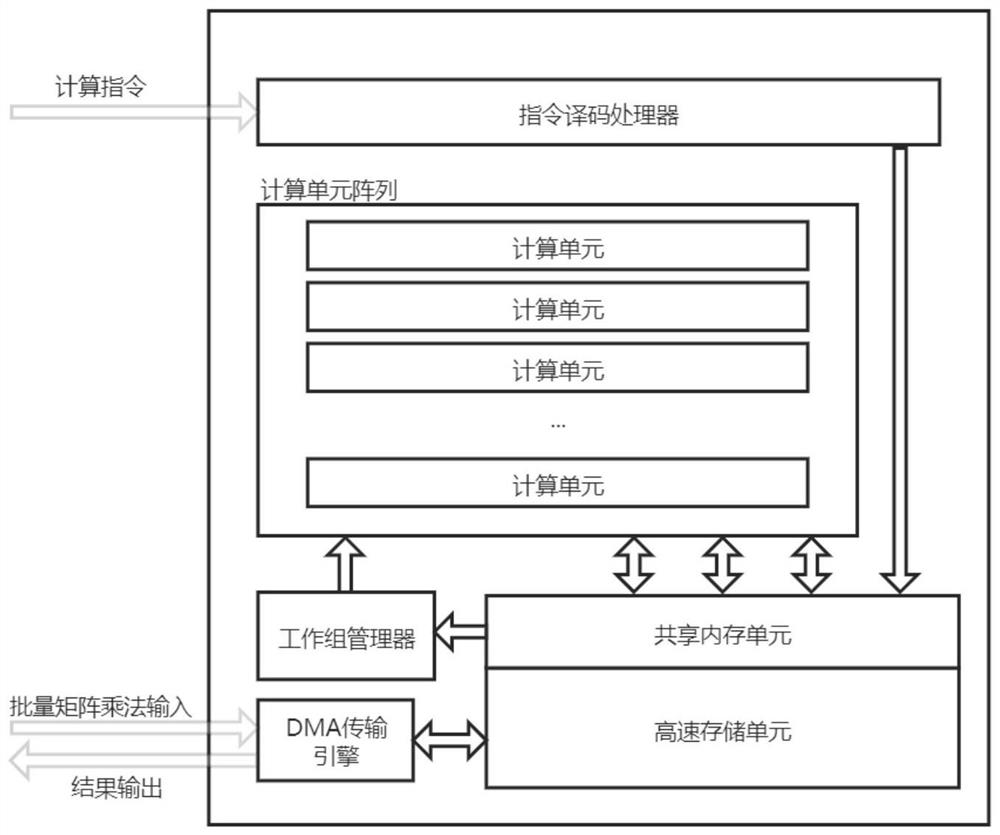

[0053] A GPU batch matrix multiplication accelerator such as figure 1 shown, including:

[0054] The instruction decoding processor reads and decodes the DMA transmission packet submitted by the CPU side to the instruction queue, and transmits the decoded result to the DMA engine to load the matrix data from the CPU side;

[0055] The computing unit is used to perform parallel execution calculation on the loaded matrix shards, and calculate the sharding calculation results in the matrix sharding in parallel through the kernel function;

[0056] Shared memory unit, used to store the matrix part of the intermediate calculation process of matrix sharding;

[0057] High-speed storage unit for storing related data;

[0058] Workgroup manager for work management between units;

[0059] The main branch circuit is composed of a work group manager, an instruction decoding processor, a high-speed storage unit, a shared memory unit, a computing unit, and a DMA, which is used to optimi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More