Semiconductor integrated circuit having connection down-lead for bit line interconnection

A technology for connecting wires and semiconductors, which is applied in the field of reliable reading data, and can solve problems such as yield decline, manufacturing cost increase, and read margin reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Specific embodiments of the present invention will be described below with reference to the accompanying drawings.

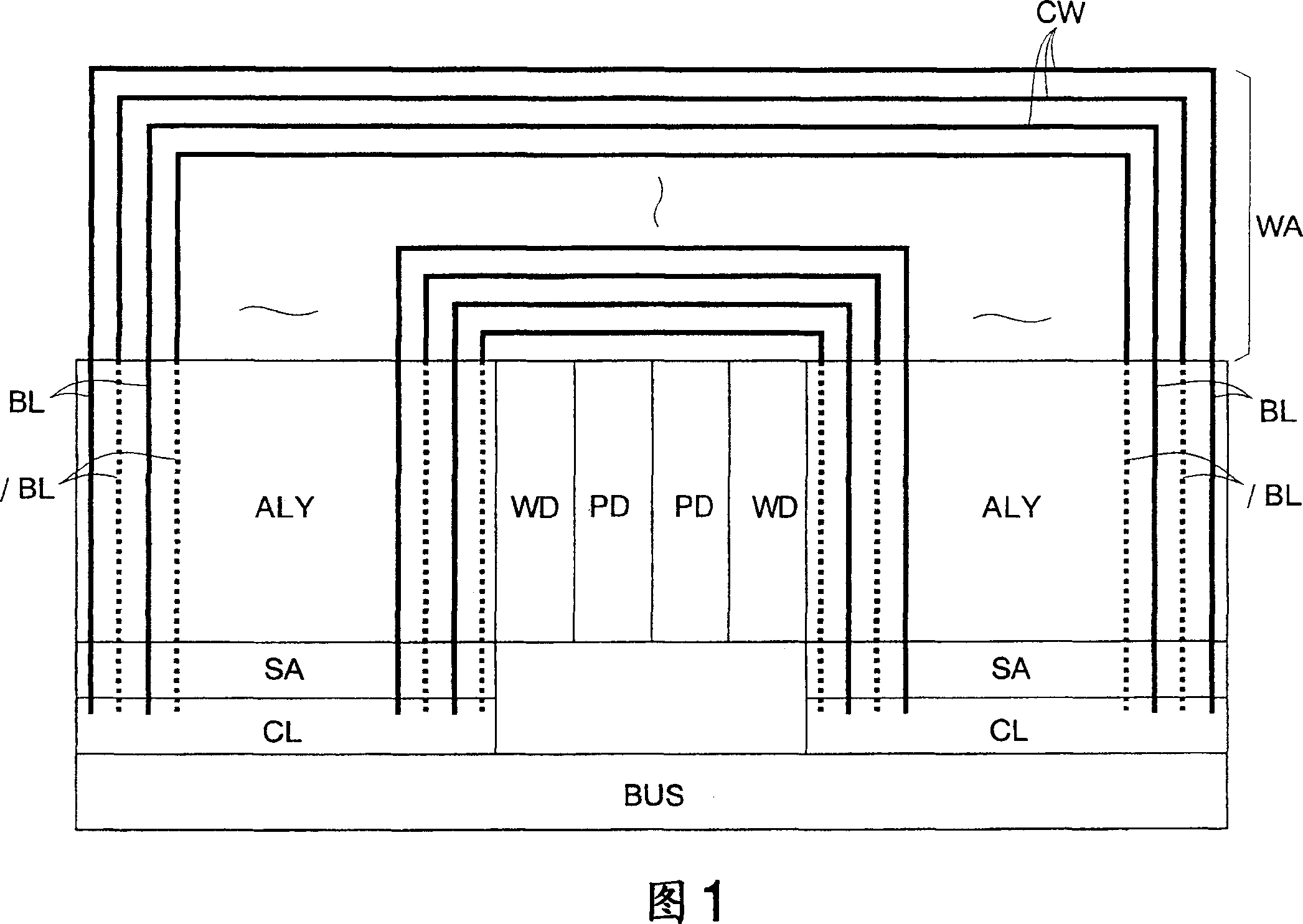

[0040] FIG. 1 shows a first embodiment of a semiconductor memory according to the present invention. This semiconductor memory is formed as a ferroelectric memory on a silicon substrate using a CMOS process. This ferroelectric memory has a storage capacity of 2k bits and can be used as, for example, an authentication chip mounted on an IC card.

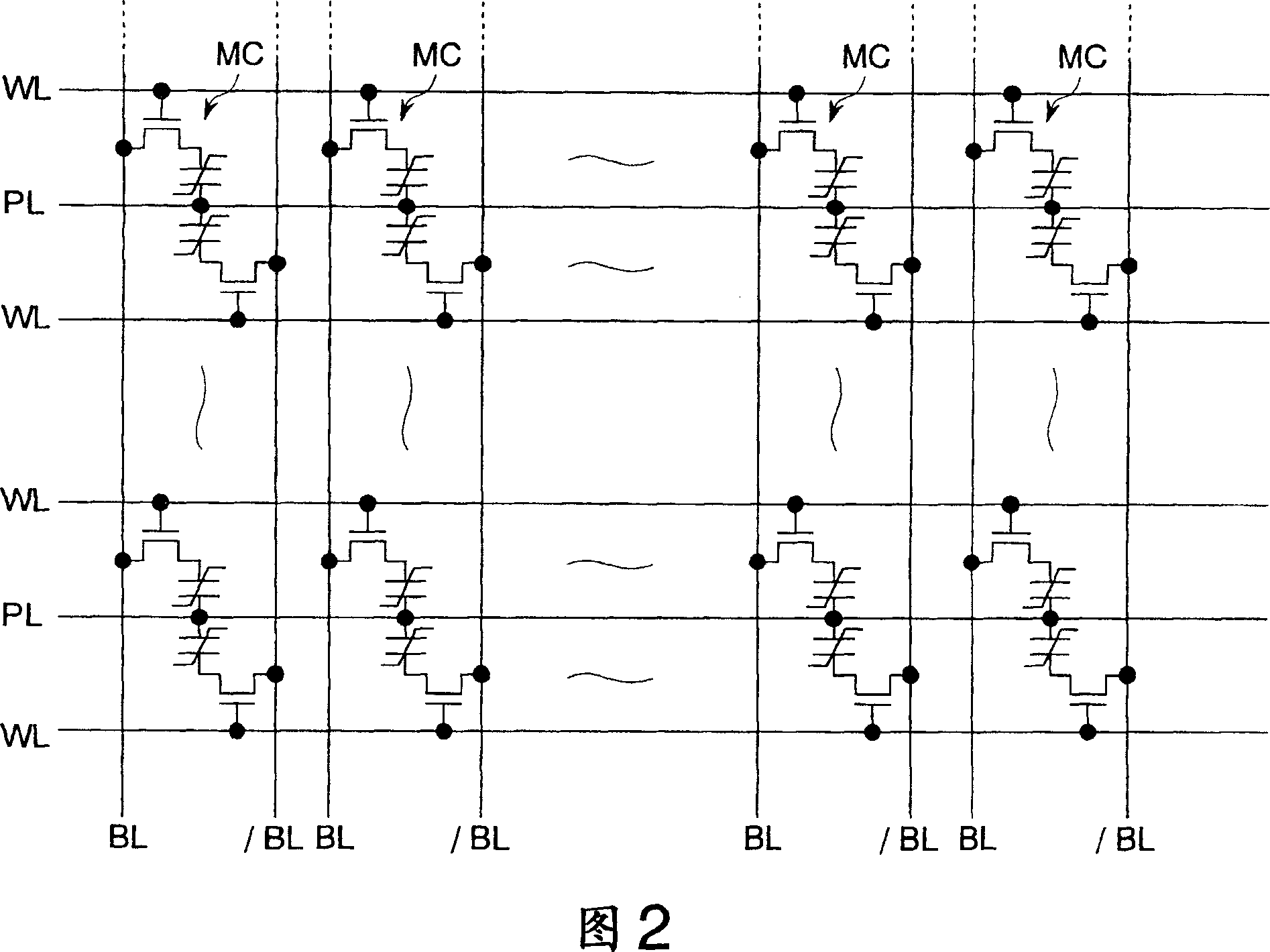

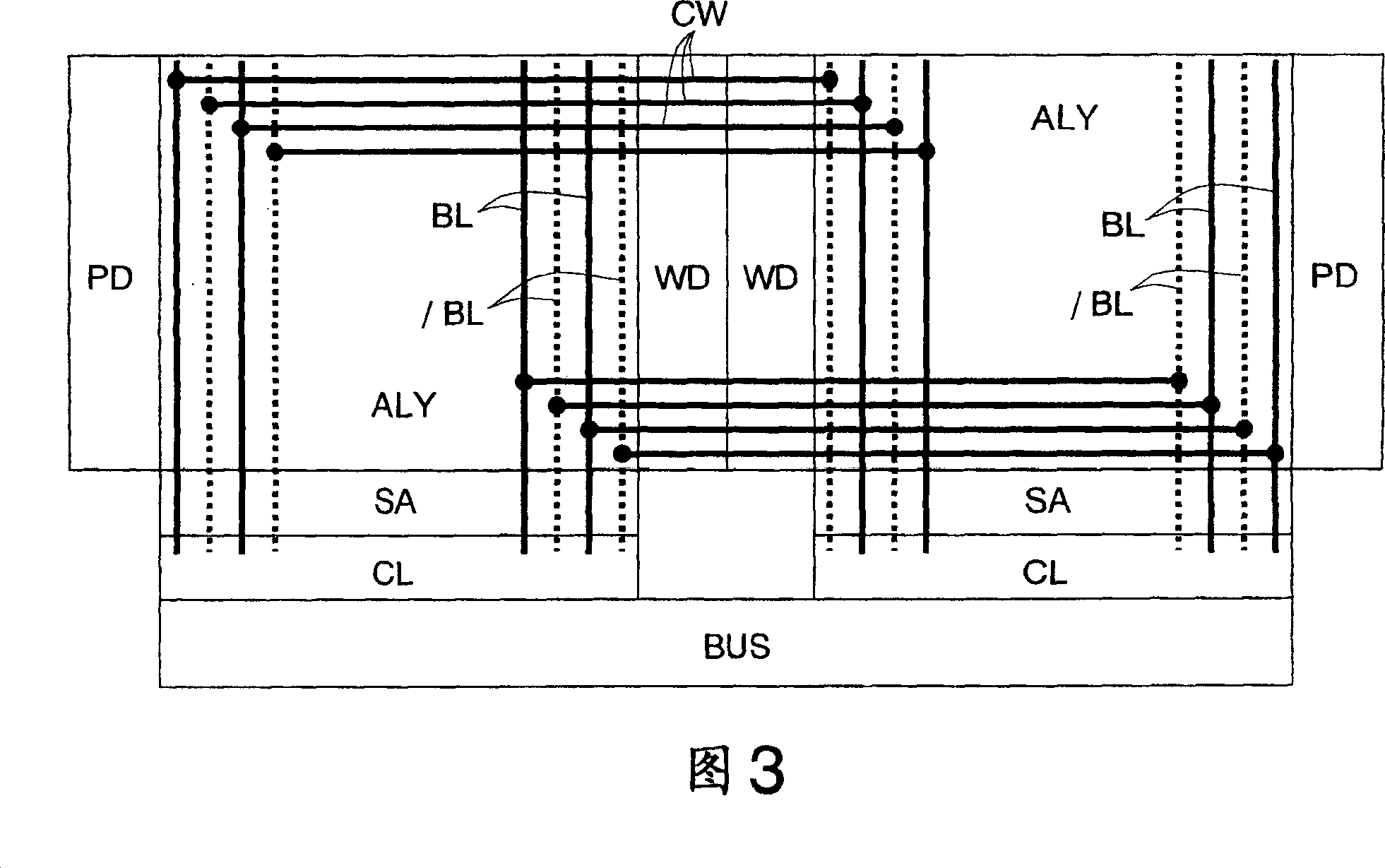

[0041] The ferroelectric memory has two memory cell arrays ALY; the connection leads CW that connect the bit lines BL and / BL of one memory cell array ALY to the respective bit lines of the other memory cell array ALY; Word drive lines WD; plate drive lines PD also associated with respective memory cell arrays ALY; sense amplifiers SA also associated with respective memory cell arrays ALY; column switches CL also associated with respective memory cell arrays ALY; and data Bus BUS.

[0042] The wiring area WA c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More