Monocrystalline silicon wafer crystal orientation calibrating method

A silicon wafer and crystal orientation technology, which is applied in the field of calibration of single crystal silicon wafer crystal orientation, can solve problems such as product performance degradation, device failure, and failure to meet the processing requirements of silicon micro devices, etc., to reduce processing errors, improve accuracy, The effect of eliminating machining errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0021] Embodiment 1: see accompanying drawing.

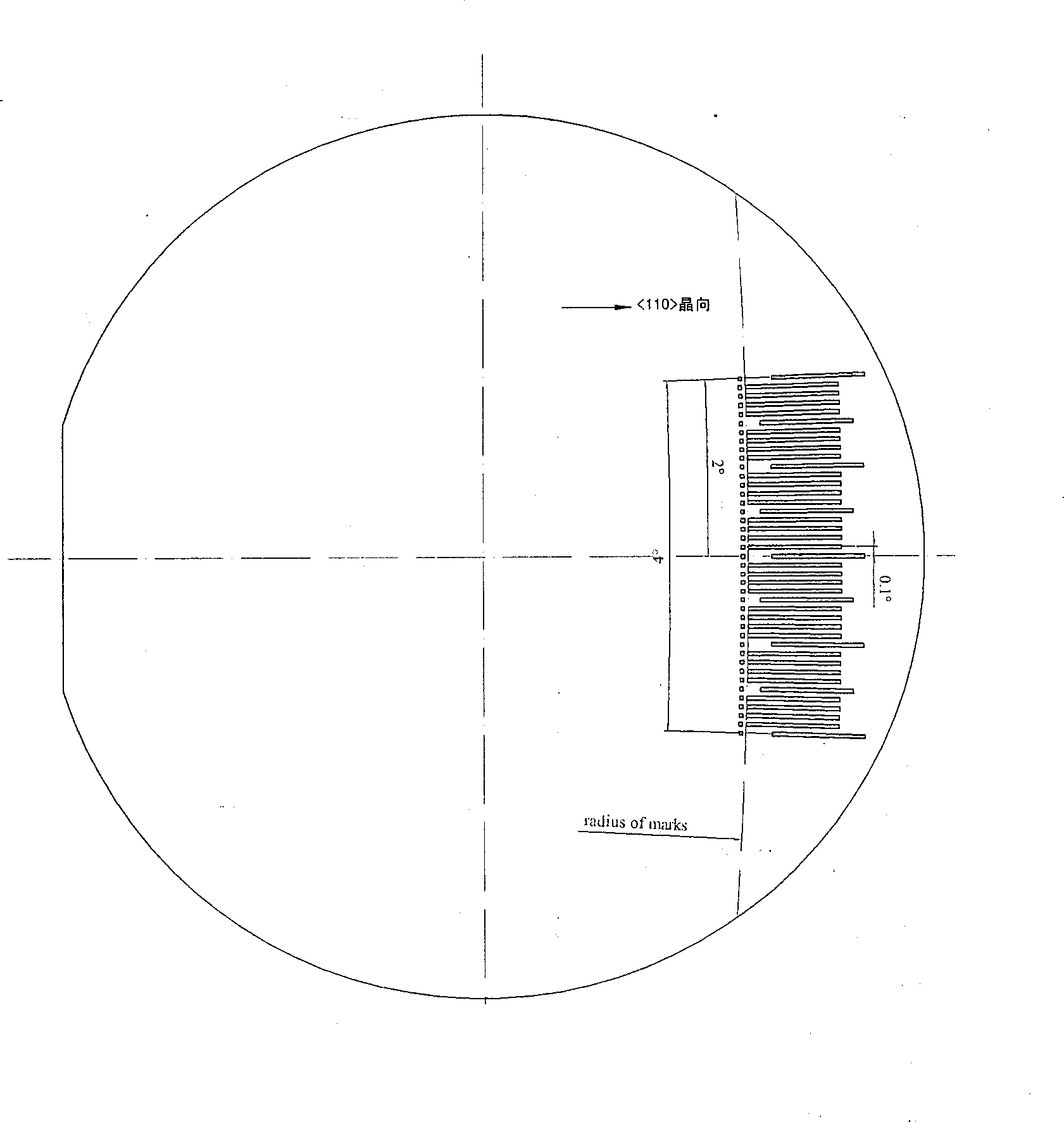

[0022] According to the size of the wafer and the requirements of processing accuracy, the layout for crystal orientation calibration is designed, and the corresponding mask is processed by conventional technology. The layout design of the mask is shown in the attached drawing. The comparison pattern of the layout consists of a A group of rectangular strips distributed in a fan shape, the centers of these rectangular strips are located on the center of a great circle, the angle between two adjacent rectangular strips is 0.05°, and all these rectangular strips are distributed at an angle of 2 ° and within the fan-shaped area with the large crystal direction of the wafer as the angle bisector, and with the large crystal direction of the silicon wafer as the axis of symmetry, these rectangular strips are symmetrically distributed; then a masking layer is processed on the silicon wafer, using the mask Plate, transfer the comparison ...

Embodiment 2

[0024] According to the size of the wafer and the requirements of processing accuracy, the layout used for crystal orientation calibration is designed, and the corresponding mask plate is processed by conventional technology. The layout design of the mask plate refers to the attached drawing. A group of rectangular strips distributed in a fan shape. The centers of these rectangular strips are located on the center of a great circle, and their long sides are parallel to the radial direction of the great circle. The angle between two adjacent rectangular strips is 0.1°. All These rectangular strips are distributed in a fan-shaped area with an included angle of 4° and the major crystal orientation of the wafer as the bisector of the angle. Taking the major crystal orientation of the silicon wafer as the axis of symmetry, these rectangular strips are symmetrically distributed. Then a masking layer is processed on the silicon wafer, and the comparison pattern is transferred to the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More