Method of raising quantizing precision of pulse width modulation

A technology of pulse width modulation and quantization accuracy, which is applied to amplifiers with semiconductor devices/discharge tubes, amplifiers, electrical components, etc., and can solve problems such as reduced amplifier efficiency, harsh power devices, and increased noise shaping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

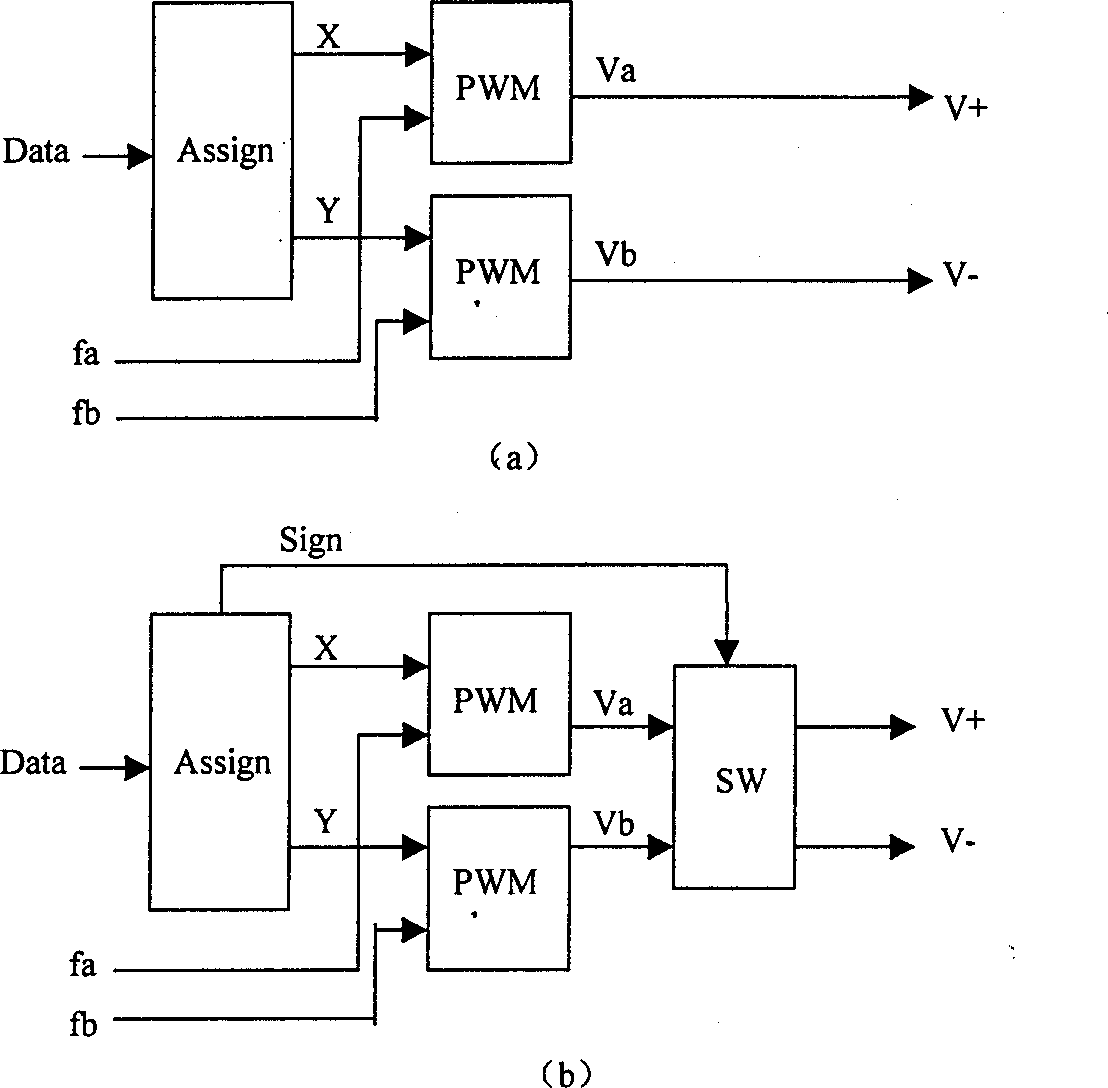

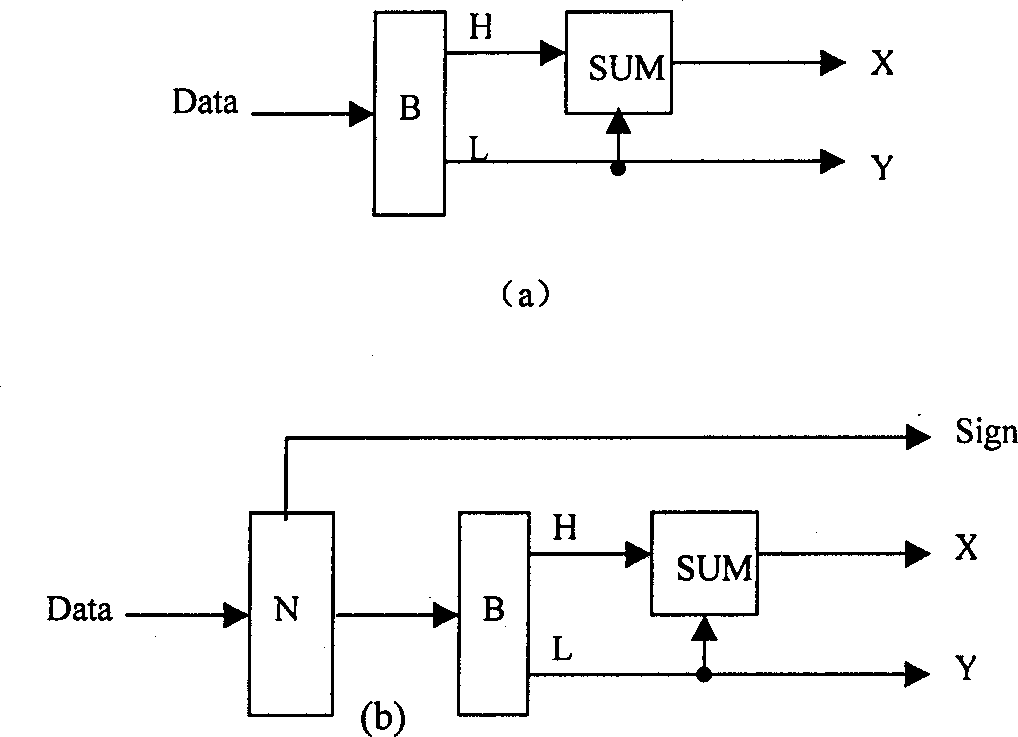

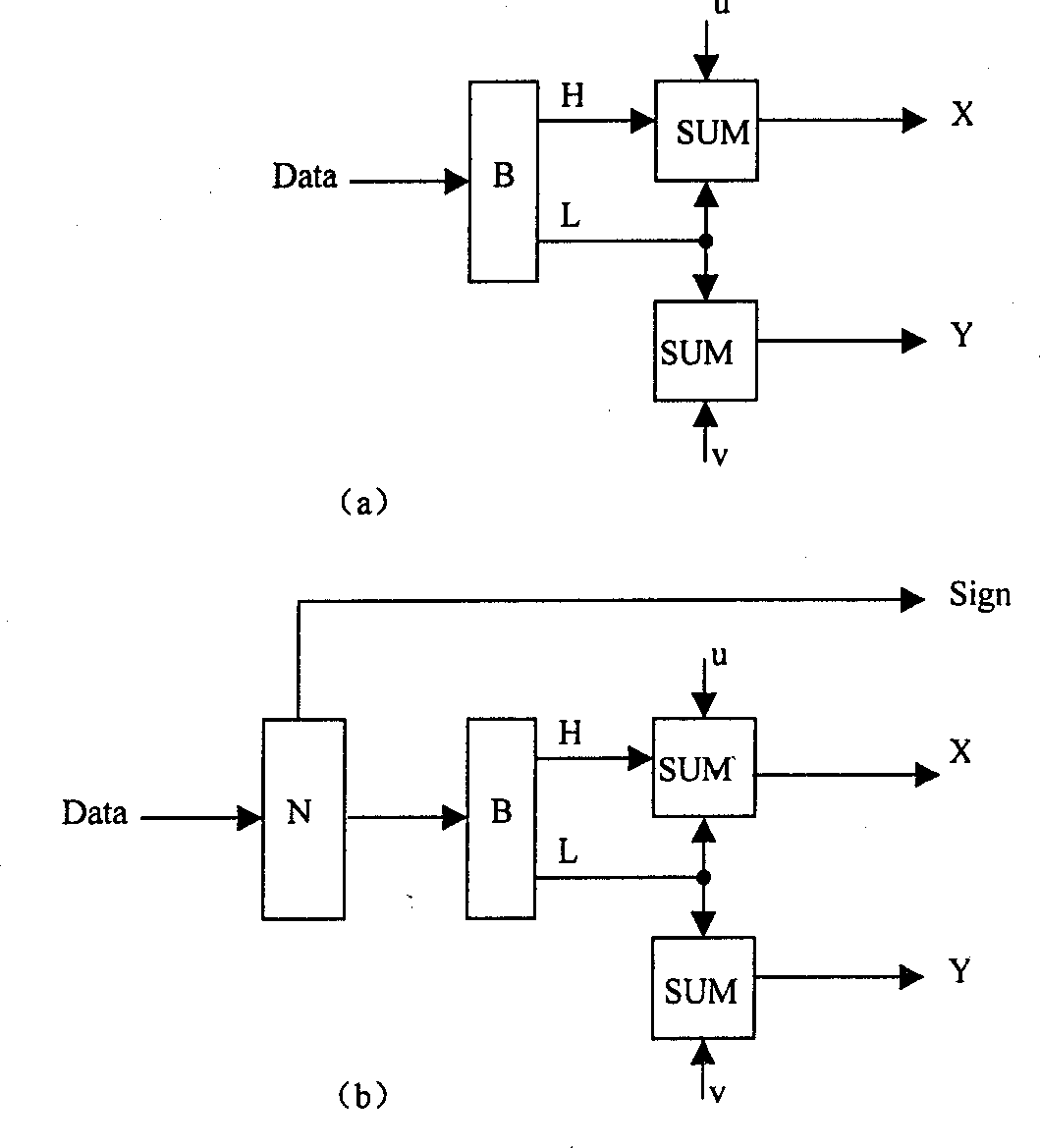

[0111] Embodiment 1, such as Figure 7 Shown:

[0112] This embodiment applies the linear compensation method (the principle block diagram is shown in the appendix Figure 5 (c)) Application to realize 16-bit audio digital / analog conversion.

[0113] The dual-mode PWM quantizer involved in the present invention can be realized by a large-scale programmable gate array FPGA and peripheral analog circuits in this embodiment. The gate array model is EP20K100, and its interior is composed of 13 circuit units. P1 is a 16-bit subtractor, which performs the subtraction operation of the input 16-bit audio data Data and the error data e, where the error data e comes from the bus interface and is preset by the system according to the deviation caused by linear compensation. If there is no error in linear compensation, the error e is set to 0. P1 outputs 17-bit data, the highest bit is the sign bit. P2 is a complementary code circuit. When the sign bit is negative, the 16-bit data is...

Embodiment approach 2

[0114] Embodiment 2, such as Figure 8 Shown:

[0115] This embodiment applies the nonlinear compensation method (the principle block diagram is shown in the appendix Image 6 ) to realize the application of an all-digital audio power amplifier.

[0116] The dual-mode PWM quantizer involved in the present invention can be realized by a large-scale programmable gate array FPGA and peripheral analog circuits in this embodiment. The gate array model is EP20K100, and its interior is composed of 15 circuit units. P1 is a 16-bit subtractor, which performs the subtraction operation of the input 16-bit audio data Data and the error data, where the error data comes from the feedback branch and is dynamically generated by the nonlinear compensation algorithm. P1 outputs 17-bit data, the highest bit is the sign bit. P2 is a complementary code circuit. When the sign bit is negative, the 16-bit data is reversed and one is added, and then output, completing the absolute value circuit fu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More