Method for eliminating stress and damage while forming isolation component

A technology for eliminating stress and components, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as stress damage in the active area of semiconductor components and reduction in reliability of semiconductor components

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The method of the present invention can be widely applied to many semiconductor designs, and can be made using many different semiconductor materials. When the present invention describes the method of the present invention with a preferred embodiment, those who are familiar with this field should recognize Many steps can be changed, and materials and impurities can also be replaced, and these general replacements undoubtedly do not depart from the spirit and scope of the present invention.

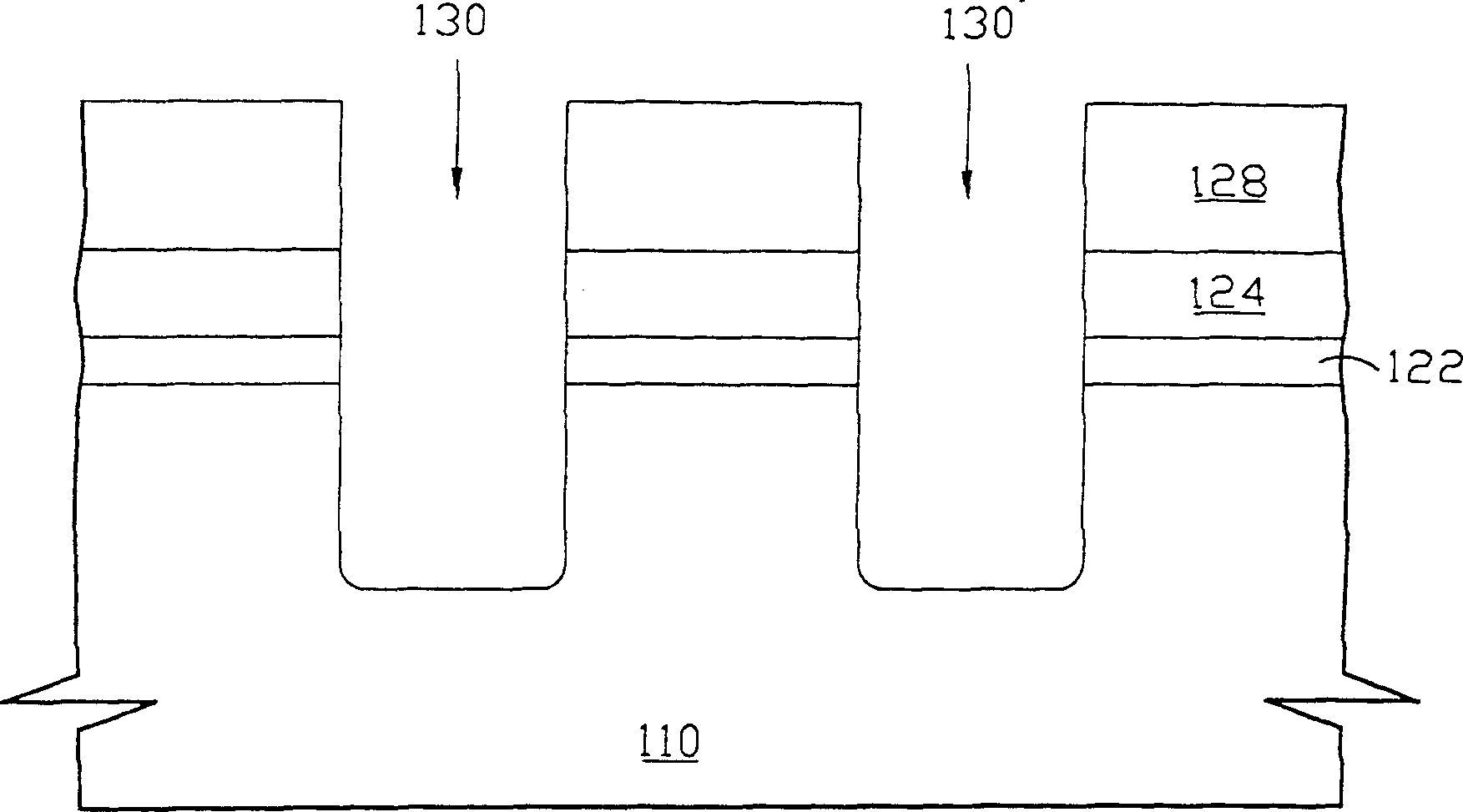

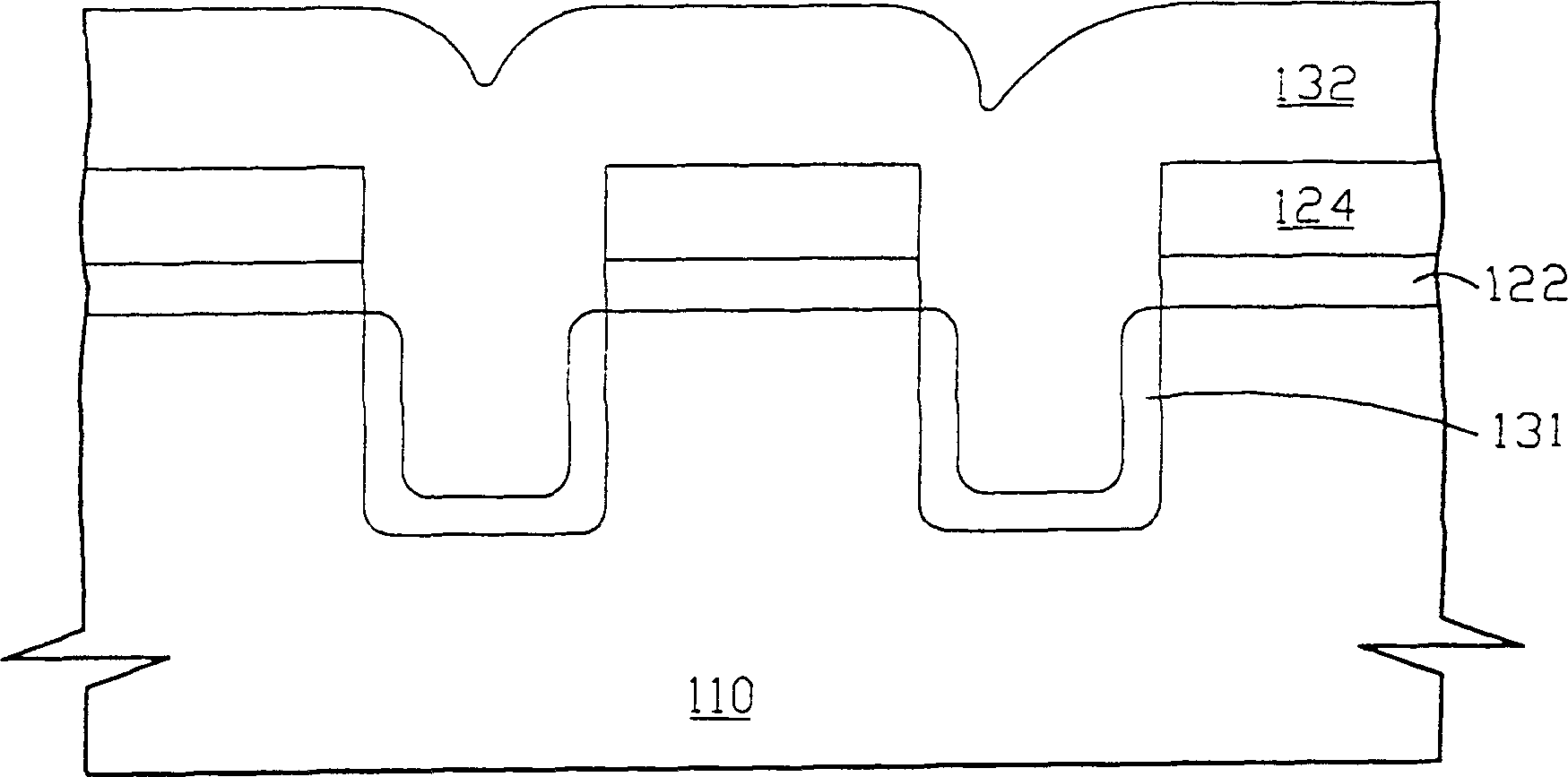

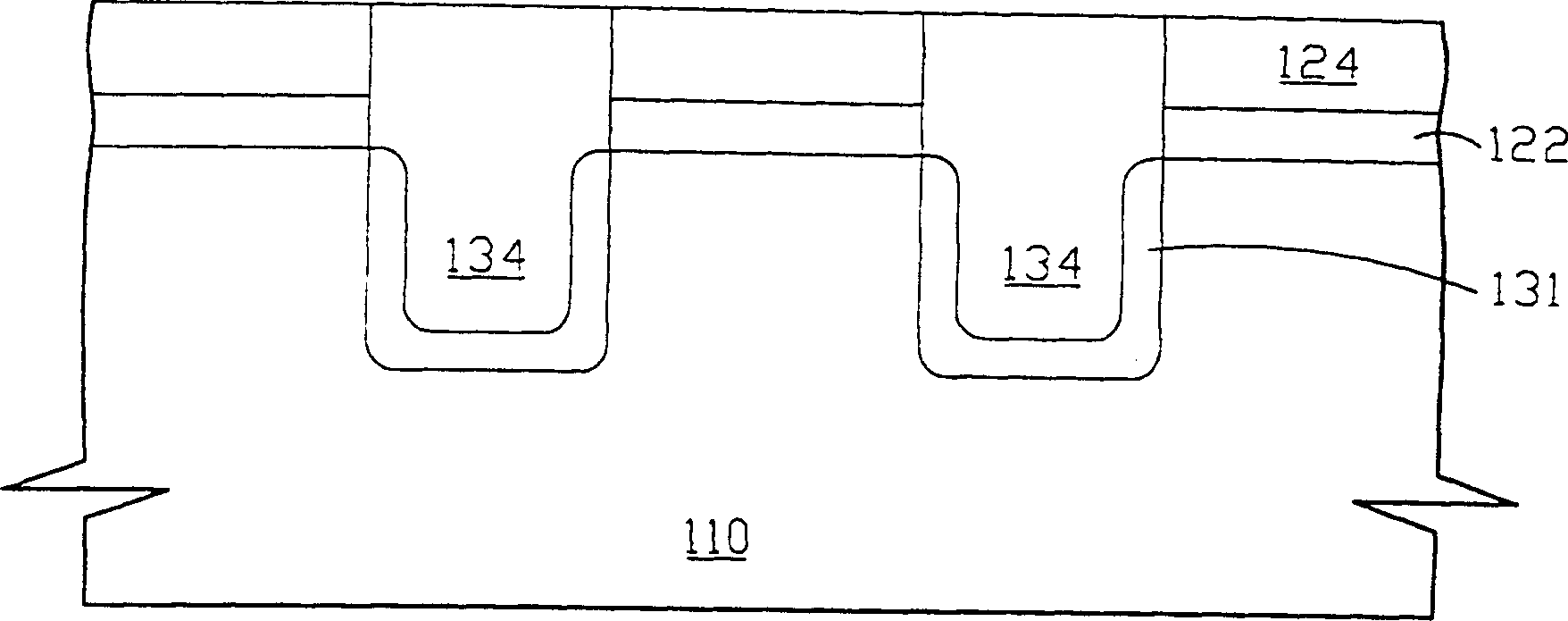

[0016] Secondly, the present invention is described in detail as follows with schematic diagrams. When describing the embodiments of the present invention in detail, the cross-sectional view showing the semiconductor structure will not be partially enlarged according to the general scale in the semiconductor manufacturing process for the convenience of explanation, but it should not be used as a limitation. In addition, in actual production, the three-dimensional space dimensions of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More