Semiconductor device and capacitance measuring method

A capacitance measurement and semiconductor technology, which is applied in semiconductor/solid-state device testing/measurement, semiconductor devices, semiconductor/solid-state device manufacturing, etc., can solve problems such as difficult, difficult separation of wiring capacitance components, inconsistent gate lengths, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

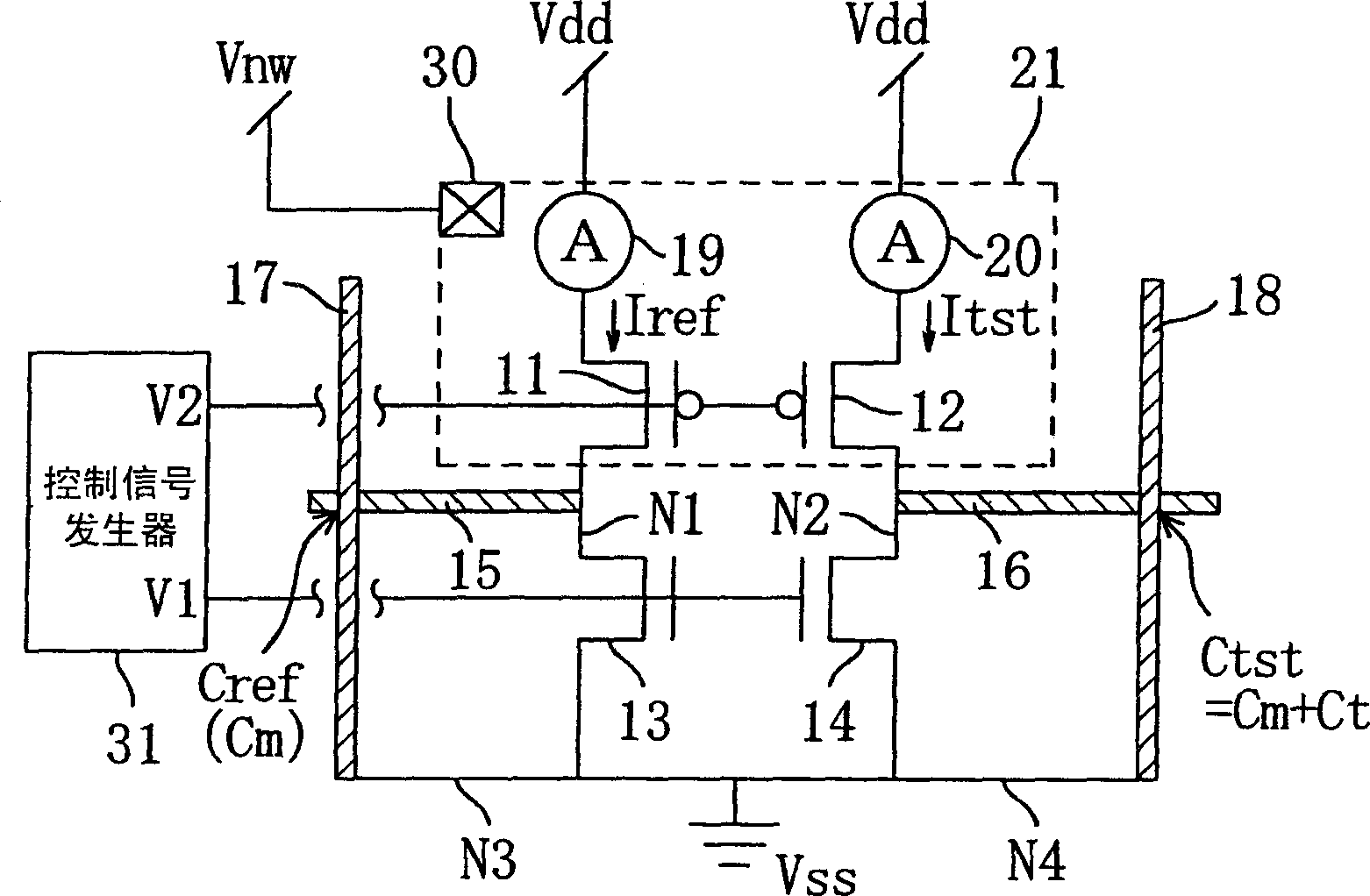

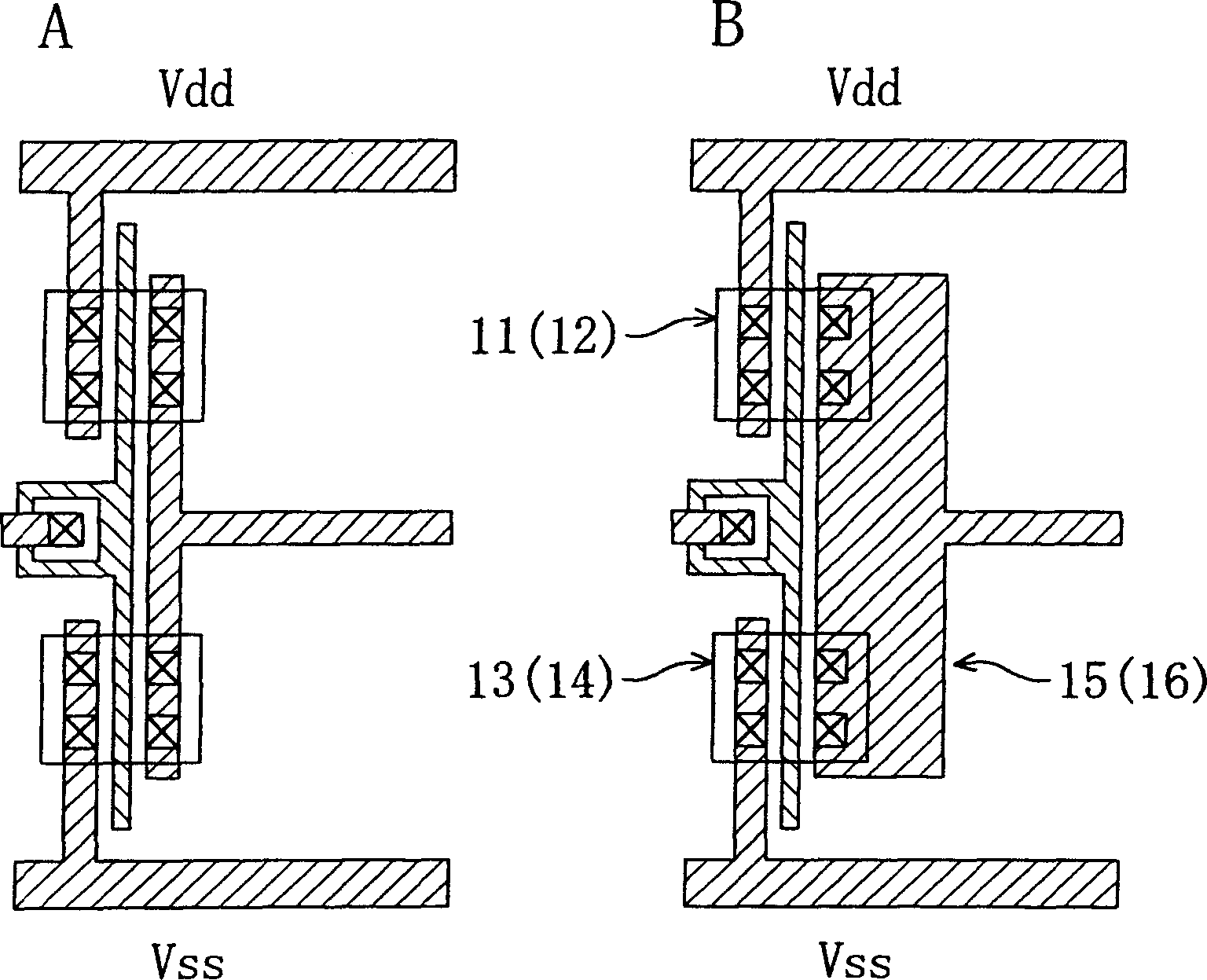

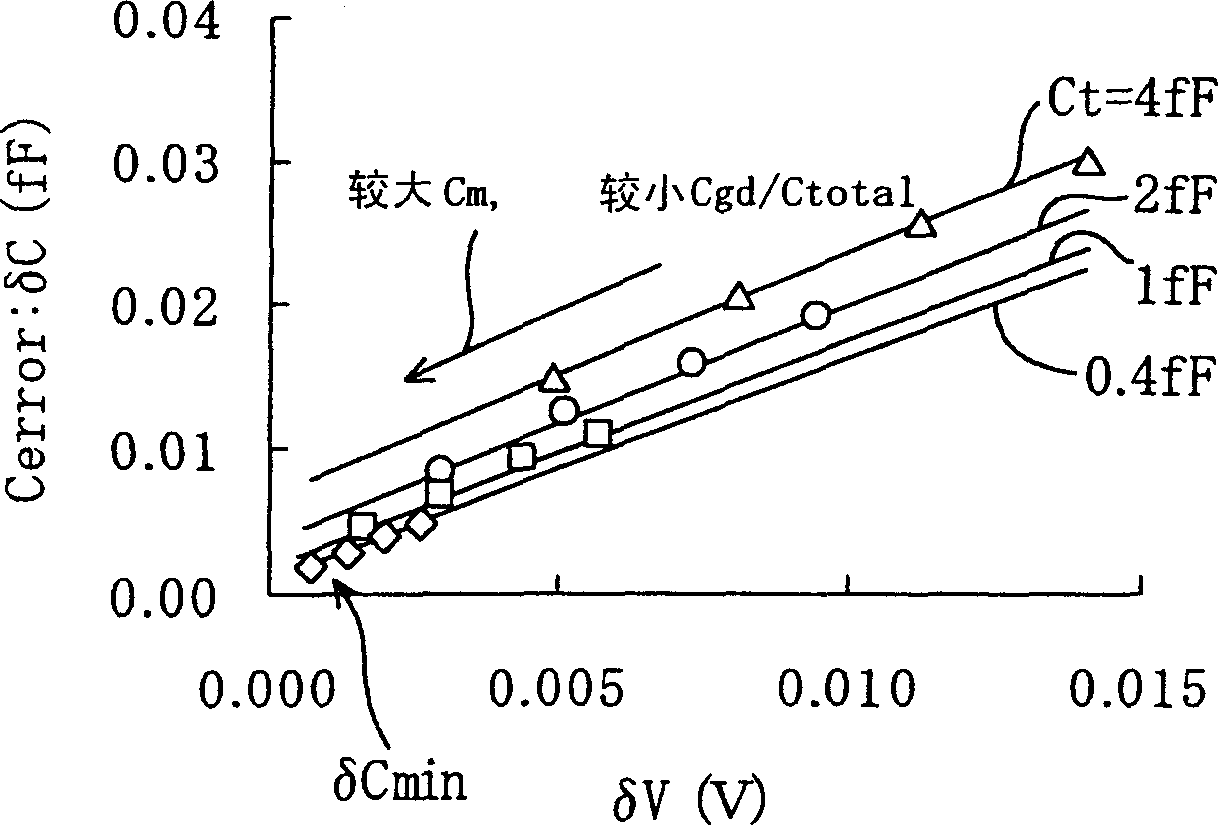

[0133] figure 1 It is a circuit block diagram schematically showing the circuit configuration of the CBCM measurement device (semiconductor device of the present invention) used in Embodiment 1 of the present invention.

[0134] Such as figure 1 As shown, the CBCM measuring device of this embodiment has: a reference PMIS transistor 11 , a test PMIS transistor 12 , a reference NMIS transistor 13 , and a test NMIS transistor 14 . And, the reference PMIS transistor 11 and the test PMIS transistor 12 have a gate length and a gate width equal to each other in the mask size, and the reference NMIS transistor 13 and the test NMIS transistor 14 have a gate length and a gate width equal to each other. mask size. Furthermore, in a semiconductor substrate (wafer), more semiconductor devices according to the present invention are arranged on scribe lines than in chip regions.

[0135] The reference PMIS transistor 11 and the reference NMIS transistor 13 are arranged in series between...

Embodiment 2

[0159] In this example, using the figure 1 The circuit configuration shown is the CBCM measurement setup.

[0160] Figure 5 (a) and (b) are plan views showing the structures of the first and second conductor parts for reference and the structures of the first and second conductor parts for testing in Example 2, respectively. Here, using the same mask of the pattern, a Figure 5 The reference second conductor portion 17A and the test second conductor portion 18A shown in (a) and (b). The first reference conductor portion 15A and the first test conductor portion 16A were formed using a mask having different lengths L1, L2 of one line 15a, 16a in the center and the same size and pattern in other portions. Also, when the basic length corresponding to the target capacitance is Ltar, the shapes of the respective conductor portions 15A, 16A, 17A, 18A are set such that the following expressions (3) to (5) hold:

[0161] L1=4·Ltar...(3)

[0162] L2=5·Ltar...(4)

[0163] L2-L1=L...

Embodiment 3

[0182] Figure 7 It is a circuit block diagram schematically showing the circuit configuration of the CBCM measurement device used in Embodiment 3 of the present invention.

[0183] Such as Figure 7 As shown, the CBCM measuring device of this embodiment has four PMIS transistors 51a-51d and four NMIS transistors 52a-52d. Furthermore, the respective PMIS transistors 51 a to 51 d have a mask size whose gate length and gate width are equal to each other, and the NMIS transistors 52 a to 52 d have a mask size whose gate length and gate width are equal to each other.

[0184] The PMIS transistors 51a to 51d and the NMIS transistors 52a to 52d are arranged in series between the terminal (terminal pad) to which the power supply voltage Vdd is supplied and the terminal (terminal pad) to which the ground voltage Vss is supplied. That is, the power supply voltage Vdd is supplied to the sources of the PMIS transistors 51a to 51d, and the ground voltage Vss is supplied to the sources o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More