Process for making plane floating grid and nonvolatile memory element containing same

A technology for memory components and manufacturing methods, applied in electrical components, semiconductor devices, semiconductor/solid-state device manufacturing, etc., can solve problems such as floating gate charge loss, interference, difficulty in obtaining windows for lithography and etching control gates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

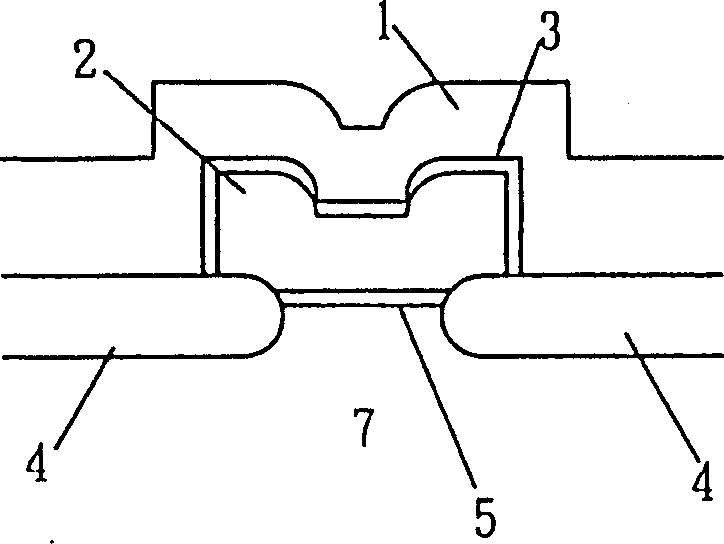

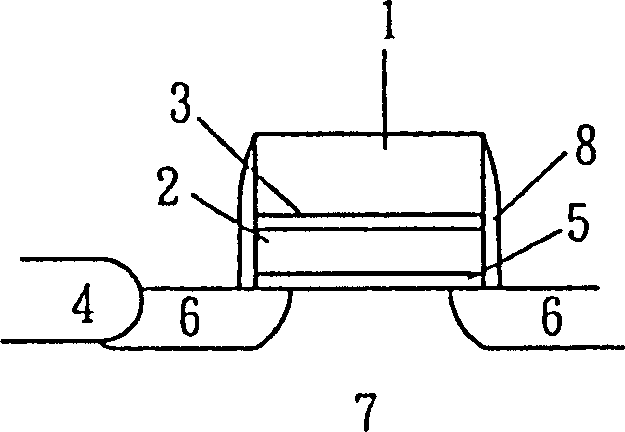

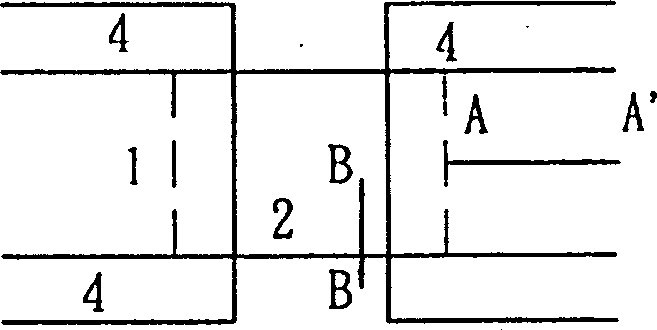

[0031] see Figure 4 , this figure shows a method for manufacturing a planar floating gate of the present invention, the steps of which include: forming an oxide layer SiO 2 After laying a layer of nitride layer Si 3 N 4 on the oxide layer. The developed nitride pattern is produced by lithography and etching, and the nitride residual area is the active area AA used to fabricate the components in the IC. Using residual Si 3 N 4 Nitride pattern as mask to etch away SiO 2 layer and etch the Si substrate to form trenches. An oxide layer is formed on the surface of the trench 14 and deposited to fill the trench. The oxide on the surface of the wafer is polished by using the oxide chemical mechanical polishing (CMP) with the nitride layer as the polishing stop layer. Etch the oxide layer to the height of the active area (AA) Si surface. The remaining nitride pattern and oxide on the silicon surface are then removed. Oxide-filled trench isolation is called STI (Shallow Tren...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More