Manufacturing method of semiconductor device and semiconductor device

A manufacturing method and semiconductor technology, which are applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, and semiconductor/solid-state device components, etc., can solve the problems of many processes and high costs, and achieve simplified manufacturing processes, improved production capacity, and reduced costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0076] In the first embodiment and the second embodiment described later, a capacitor is formed on a semiconductor device having a CSP structure produced by the premise technology.

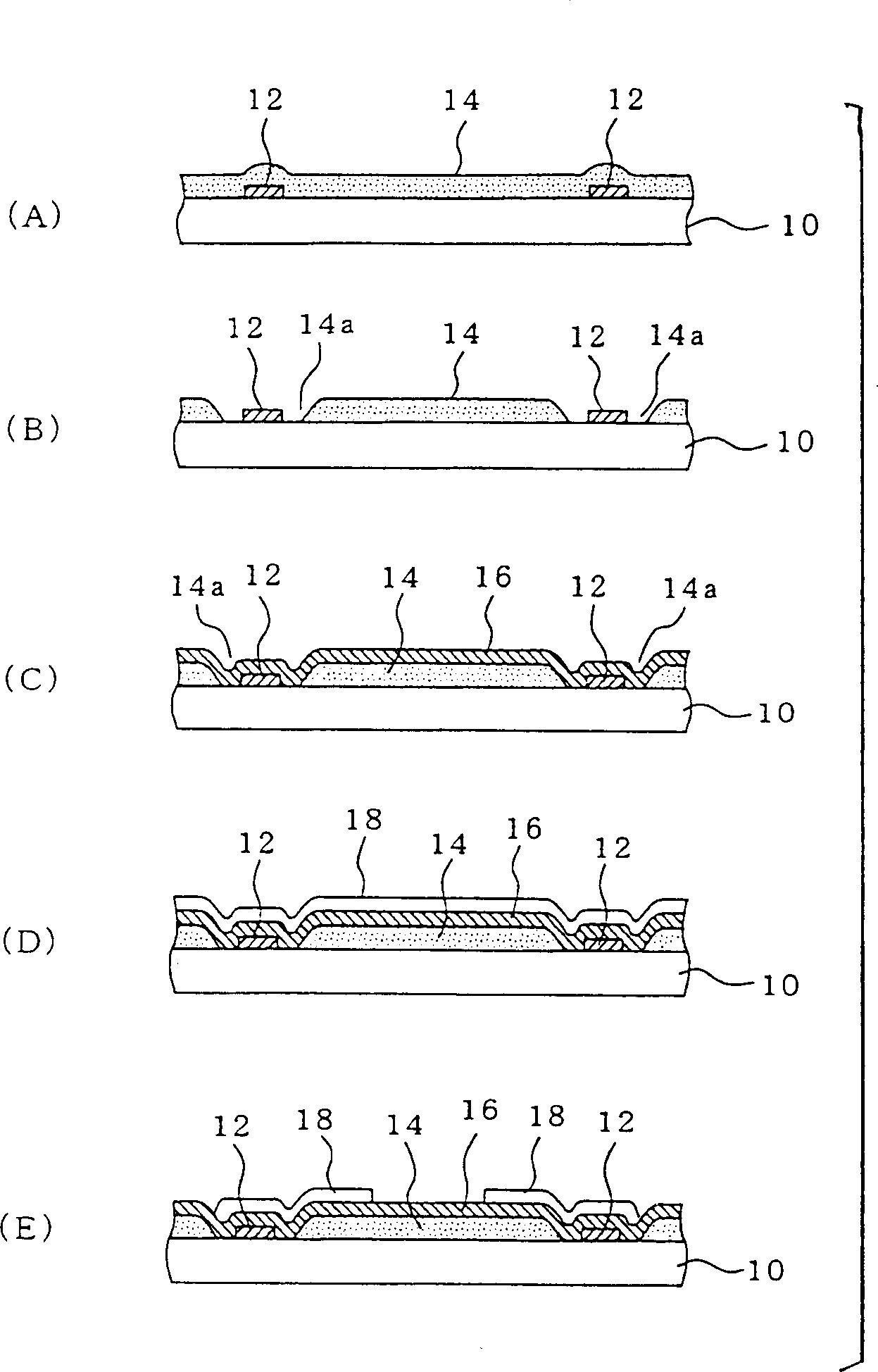

[0077] Figure 5 It is an explanatory diagram of the manufacturing method of the semiconductor device of the first embodiment. In addition, the present embodiment 1 is also carried out in the same manner as the above-mentioned premise technique. figure 1 (A)~(E), figure 2 The process shown in (A). Therefore, below, detailed explanations about the same steps as those of the above-mentioned premise technology will be omitted, and the parts different from the premise technology of the present embodiment 1 will be mainly described hereafter.

[0078] Such as Figure 5 As shown in (A), after forming the wiring 3 as a wiring layer on the chromium (Cr) layer 16 , the insulating layer 102 is formed on the entire surface of the wafer 10 . Here, the insulating layer 102 is made of photosensitive polyi...

Embodiment 2

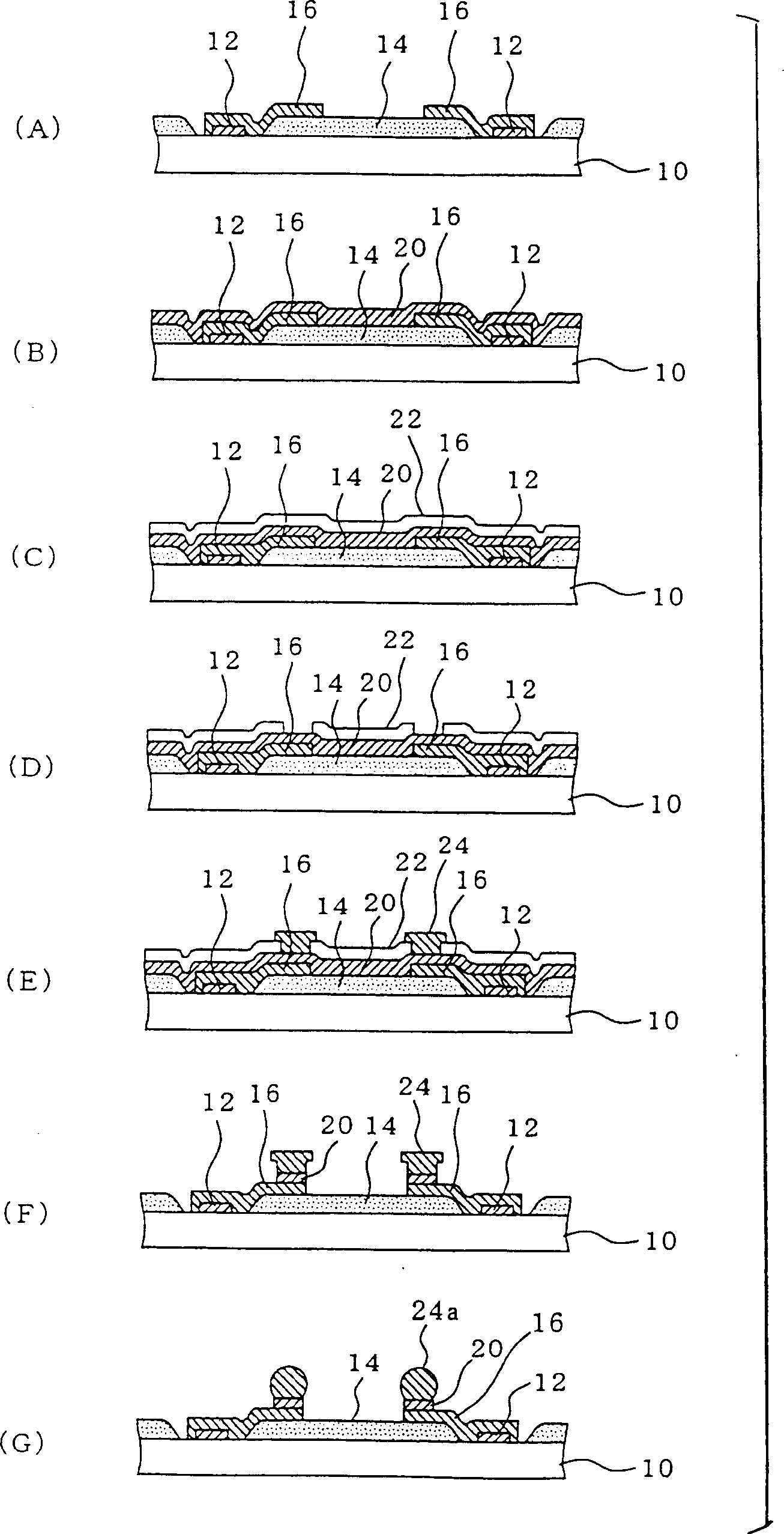

[0093] Figure 7 It is an explanatory drawing of the manufacturing method of the semiconductor device of Example 2. In addition, since the second embodiment and the above-mentioned embodiment 1 Figure 5 The steps after the step shown in (C) to the sintering of the dielectric layer 104 are the same, so the difference between the second embodiment and the first embodiment will be mainly described here.

[0094] Such as Figure 7 As shown in (A), in the second embodiment, the conductive layer 112 is formed on the sintered dielectric layer 104 by applying a conductive liquid from the discharge head 101 . Since the conductive layer 112 corresponds to the copper (Cu) layer 20 of the above-mentioned premise technology, it may be formed of nickel (Ni) in addition to copper (Cu). In addition, support balls 24 a serving as external electrodes are formed on the conductive layer 112 as described in the aforementioned premise technique. After the supporting balls 24 a are formed, they...

Embodiment 3

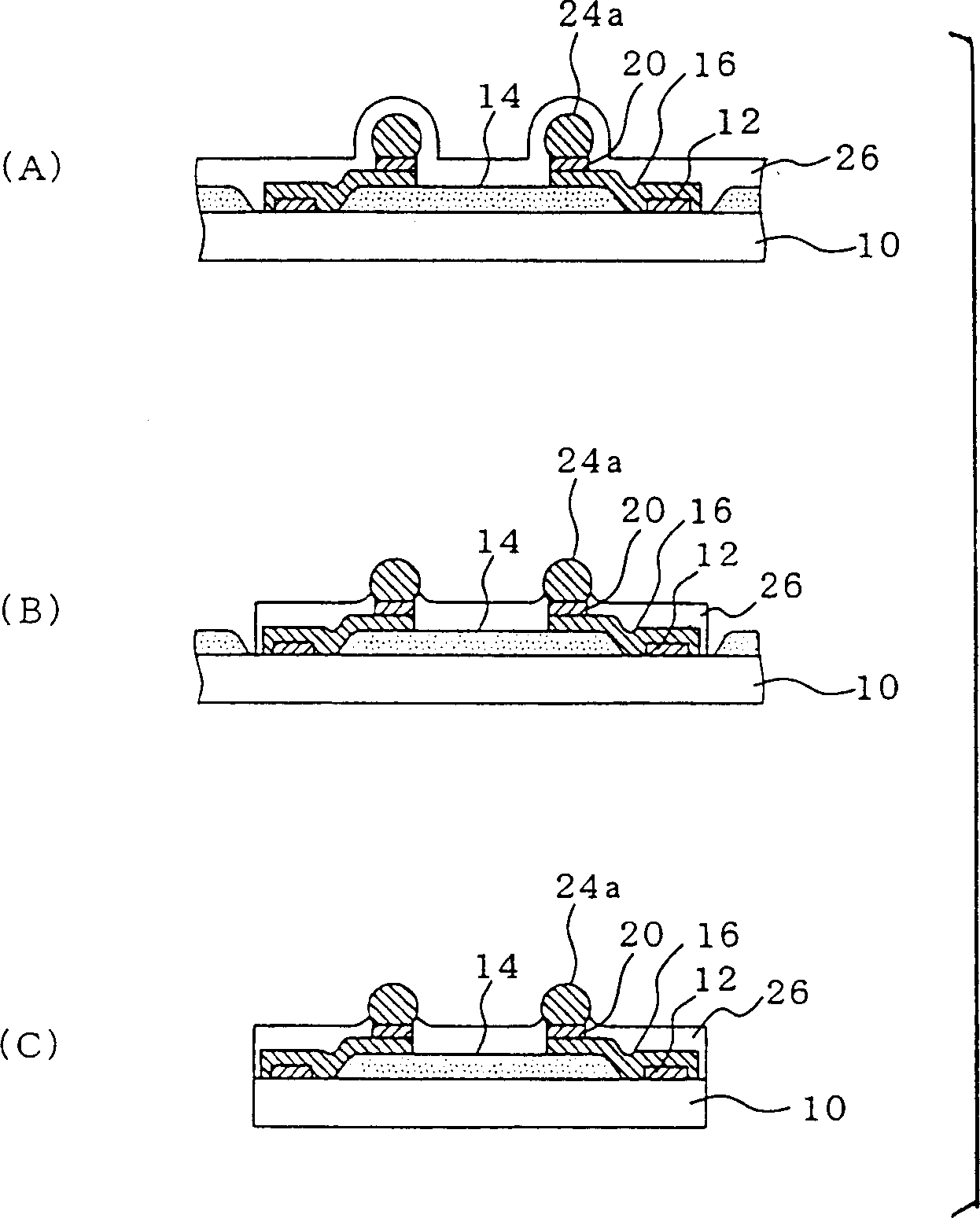

[0100] In the third embodiment, an inductor is formed on a semiconductor device having a CSP structure formed according to the above-mentioned premise technique.

[0101] Figure 9 It is an explanatory drawing of the manufacturing method of the semiconductor device of Example 3. Figure 10 is through Figure 9 A plan view of a semiconductor device formed by the fabrication method shown. Figure 9 The manufacturing process shown is equivalent to Figure 10 The A-A cross-section has been fabricated.

[0102] In this embodiment 3, it is carried out in the same manner as the above-mentioned premise technology figure 1 (A)~(E), figure 2 The process shown in (A). Therefore, below, the detailed description of the same steps as those of the above-mentioned premise technology will be omitted, and the parts different from the premise technology of this embodiment 3 will be mainly described thereafter.

[0103] After forming the wiring 3 as a wiring layer on the chromium (Cr) lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More