Hybrid monolithic integration

a monolithic integration and hybrid technology, applied in the field of semiconductor structure, can solve the problems of limiting circuit integration to much lower levels, lack of established processes, and relatively limited device speed, and achieves the effects of improving device performance, minimizing cross-contamination possibility, and high density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

A FIG. 1

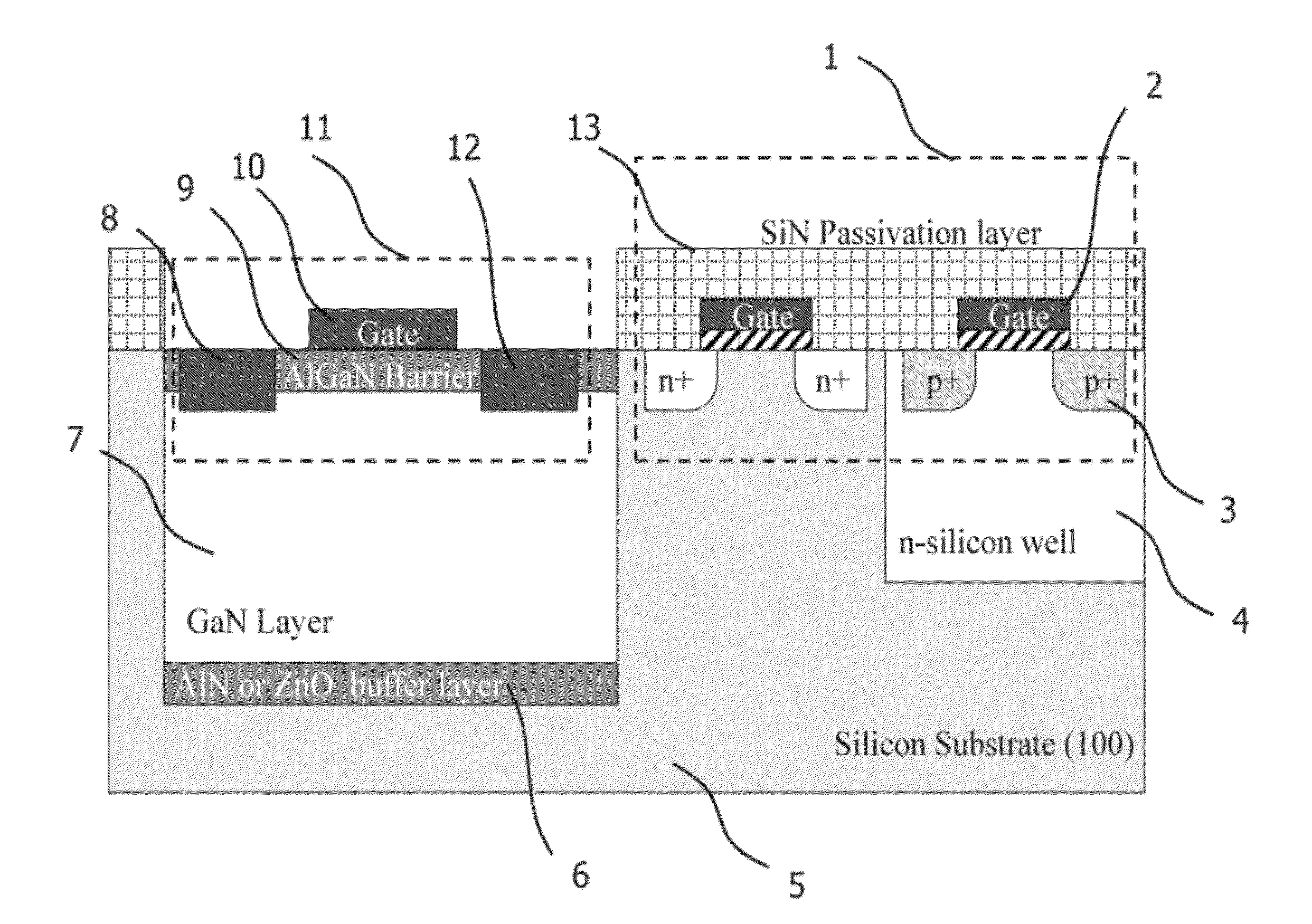

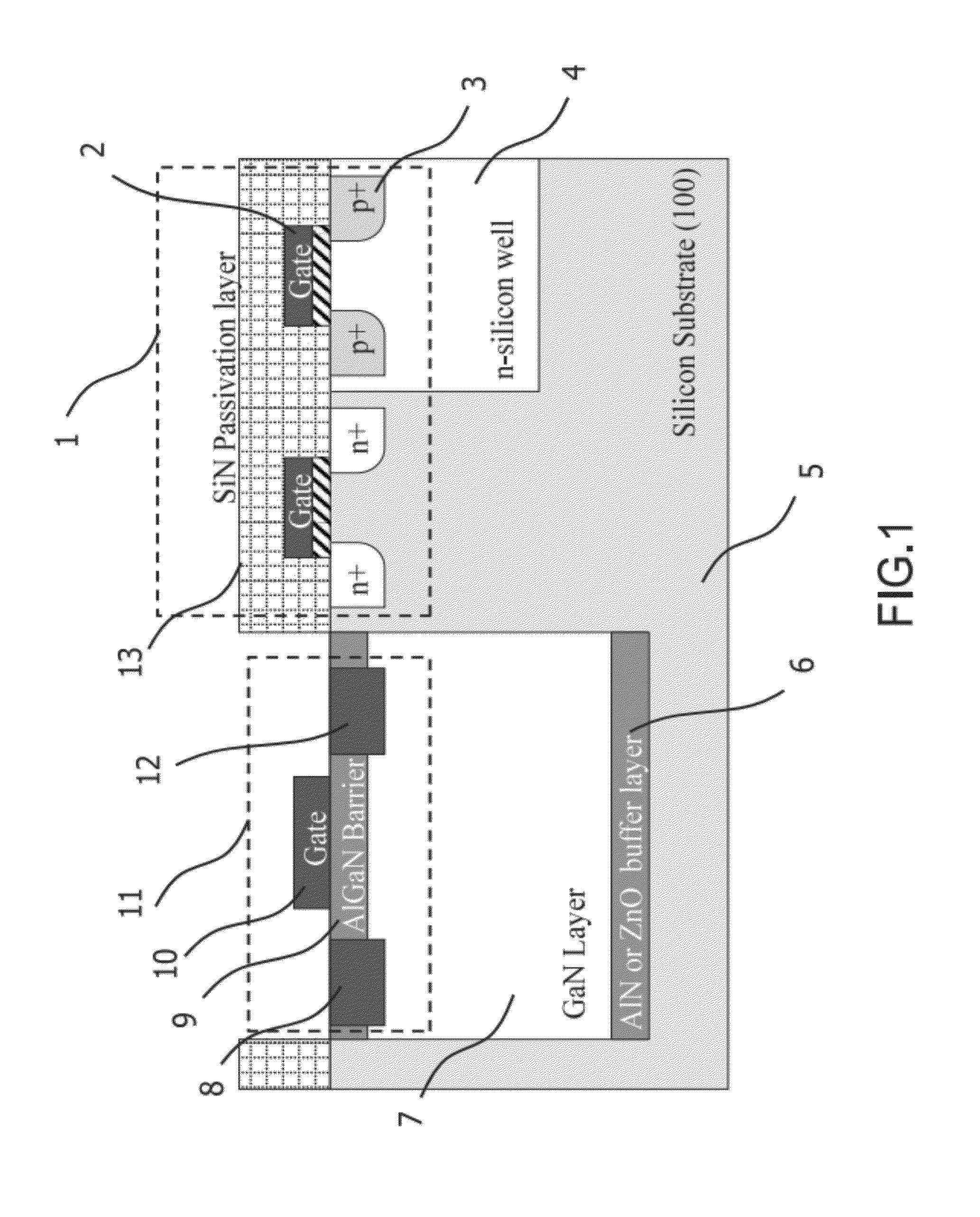

[0047]FIG. 1 is showing a cross section view of a hybrid integrated circuit according to a first embodiment of the invention. In this example a CMOS circuit 1 constituted by a re-channel and a p-channel MOSFET, has been co-integrated with a GaN HEMT device 11. The fabrication process of this embodiment includes the following steps: 1) the CMOS circuitry is manufactured in a first Silicon area until the metallization process step; 2) a passivation layer is grown all over the wafer; 3) a trench is formed in a second semiconductor area, using a selective etch; 3) An AlN or ZnO nucleation or buffer layer is formed on the bottom of the silicon trench; 4) A GaN layer is grown through one or more low temperature growth process steps on the top of the nucleation layer.

[0048]Once the GaN layer has been grown, one or more devices can be formed in the III-V region using one or more of the several well known GaN device structures such as enhancement or depletion HEMTs in single, multich...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More