High-density NROM-FINFET

A memory and storage layer technology, applied in read-only memory, transistor, static memory, etc., can solve problems such as increasing manufacturing cost and reducing integration level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

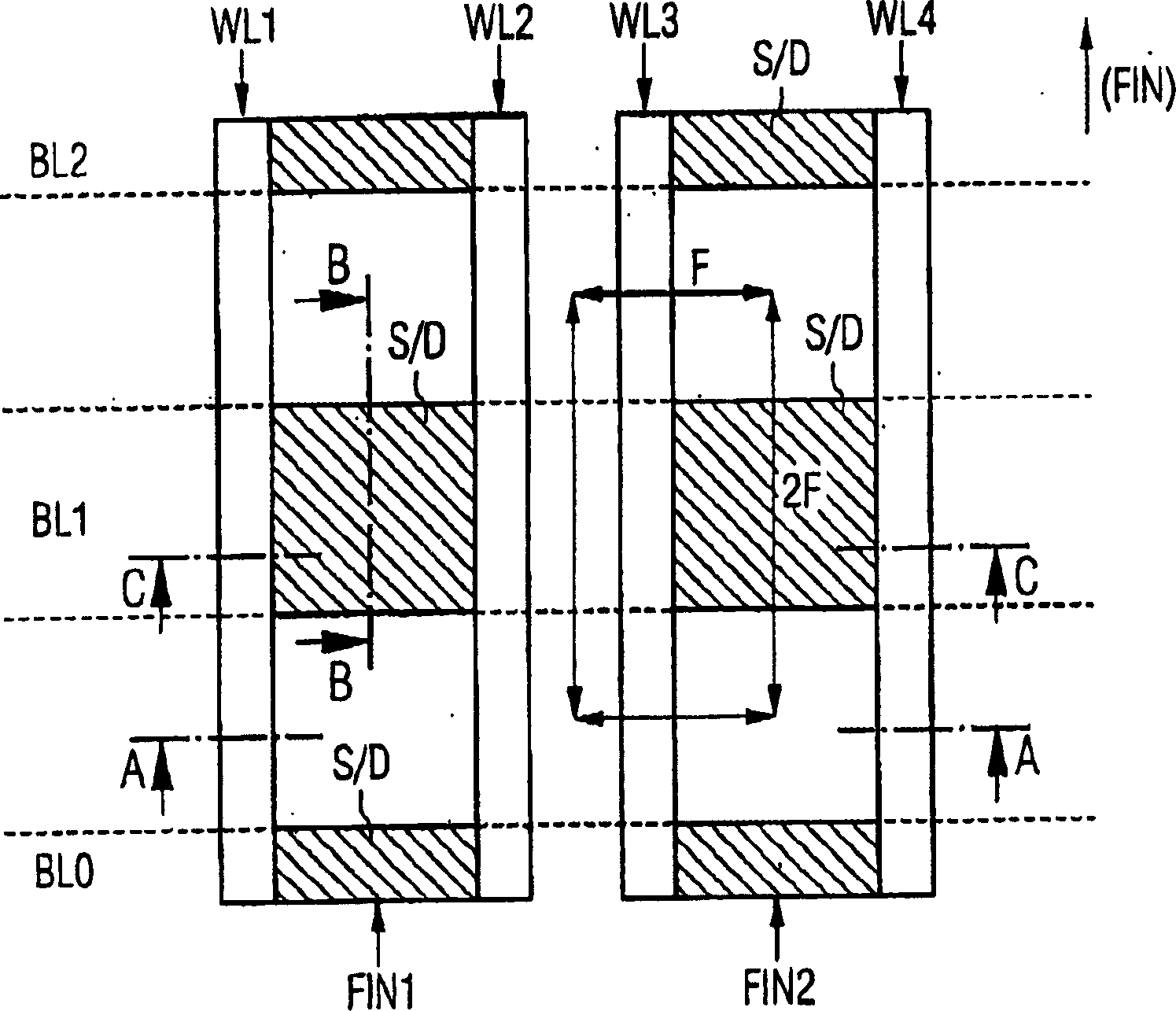

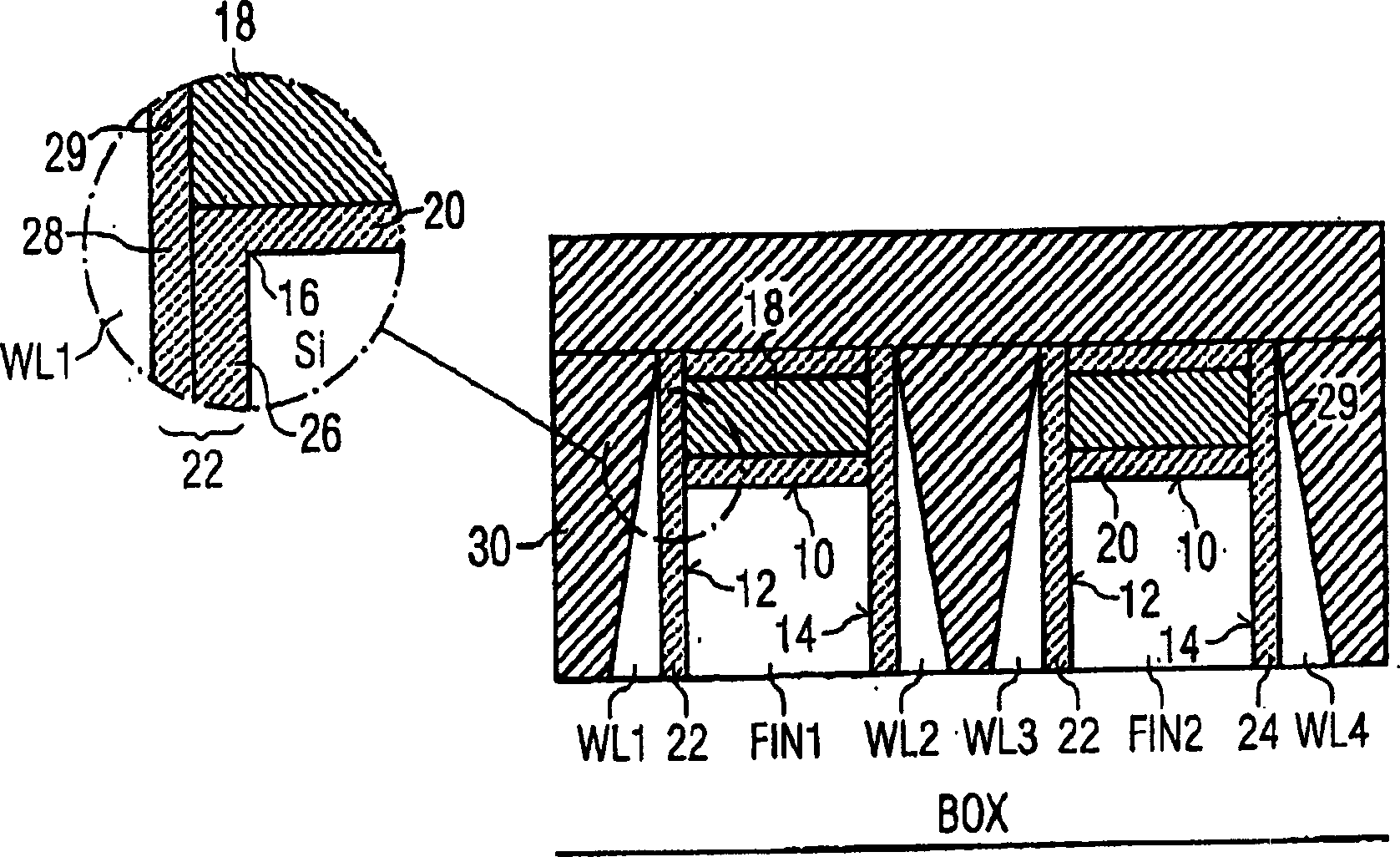

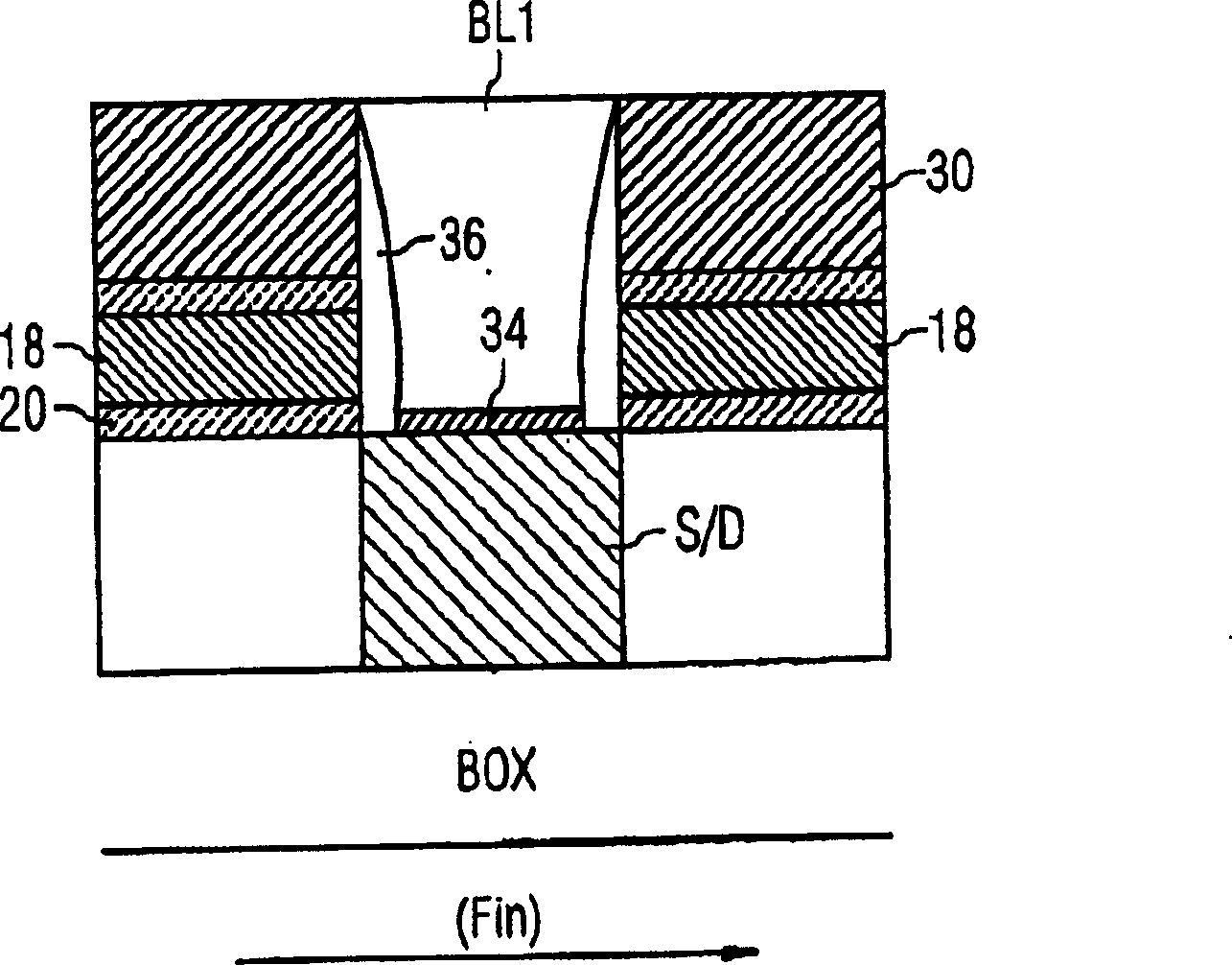

[0056] figure 1 It is a schematic plan view of a memory cell array in a preferred embodiment of a semiconductor memory according to the present invention. The character counties extending along the edges of the two fins made of silicon are labeled WL1, WL2, WL3 and WL4. The first mesh rib extends in the direction indicated by the arrow (FIN) between the word line WL1 and the word line WL2, and is marked as FIN1; the second rib extends between the word line WL3 and the word line WL4 between, and marked as FIN2. Note that, figure 1 Only a small detail of a large array of memory cells is constructed with multiple ribs FIN running parallel to each other and evenly spaced.

[0057] The highly doped contact regions S / D spaced apart from each other by a distance F are located in the ribs FIN and are marked in particular by dotted figures at figure 1 middle. Therefore, the two adjacent contact regions S / D of each rib respectively form the source and drain terminals of a FINFET (F...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More