Semiconductor device manufacturing method

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, transistors, electrical components, etc., can solve problems such as short life span of capacitors, insulation damage of capacitor insulating film 54, unstable film thickness, etc., and achieve the effect of preventing insulation damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0079] Next, a method of manufacturing a semiconductor device according to a first embodiment of the present invention will be described with reference to the drawings.

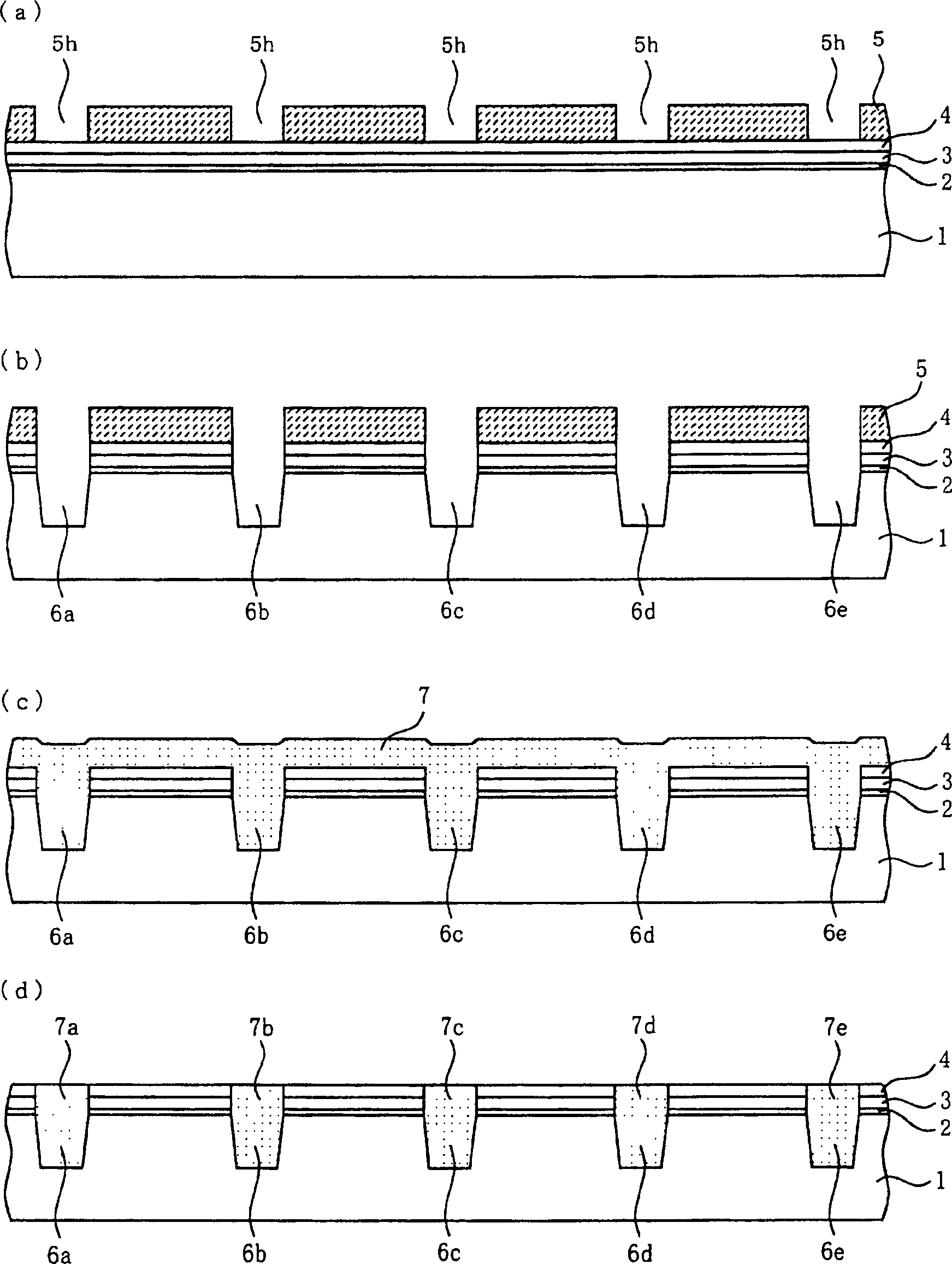

[0080] Such as figure 1 (a), by performing thermal oxidation, SiO is formed on the surface of the P-type silicon substrate 1 2 Membrane 2 (Silicon Dioxide Membrane). Then, using CVD method on SiO 2 On the film 2, a polysilicon film 3 (Poly Silicon film) having a film thickness of about 50 nm, a Si film having a film thickness of 120 nm, and 3 N 4 Film 4 (silicon nitride film). And then in Si 3 N 4 A photoresist layer 5 having a plurality of openings 5h is formed on the film 4 .

[0081] Secondly, if figure 1 As shown in (b), using the photoresist layer 5 having a plurality of openings 5h as a mask, the Si exposed at the openings 5h are sequentially etched. 3 N 4 Film 4, polysilicon film 3, SiO 2 film 2, and then etch the surface of the P-type silicon substrate 1 to form trenches 6a, 6b, 6c, 6d, 6...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More