Method for manufacturing ic-embedded substrate

一种制造方法、内置基板的技术,应用在印刷电路制造、多层电路制造、半导体/固态器件制造等方向,能够解决成品率恶化、困难、无法露出衬垫电极等问题,达到防止数量增加、防止损伤的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

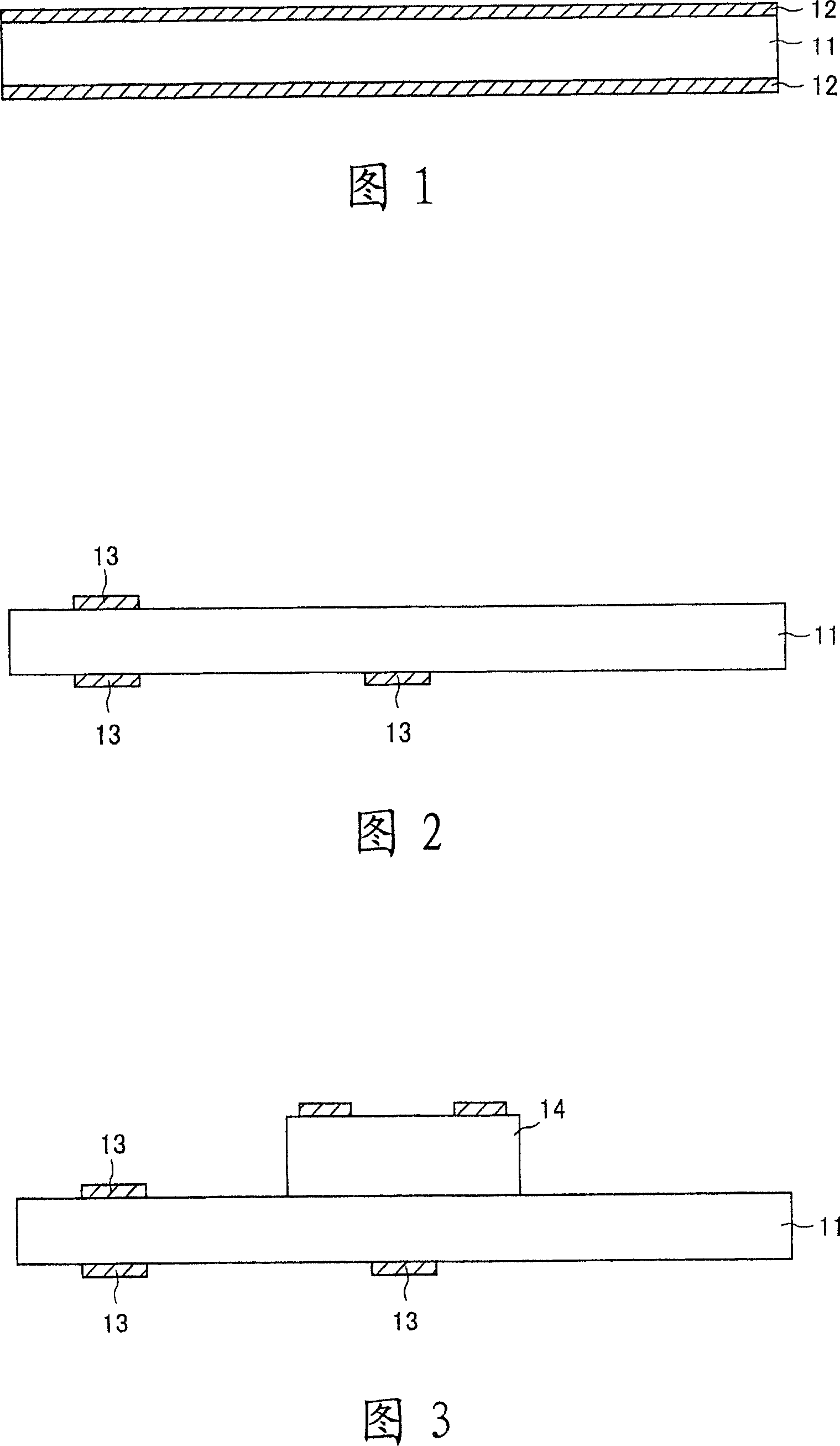

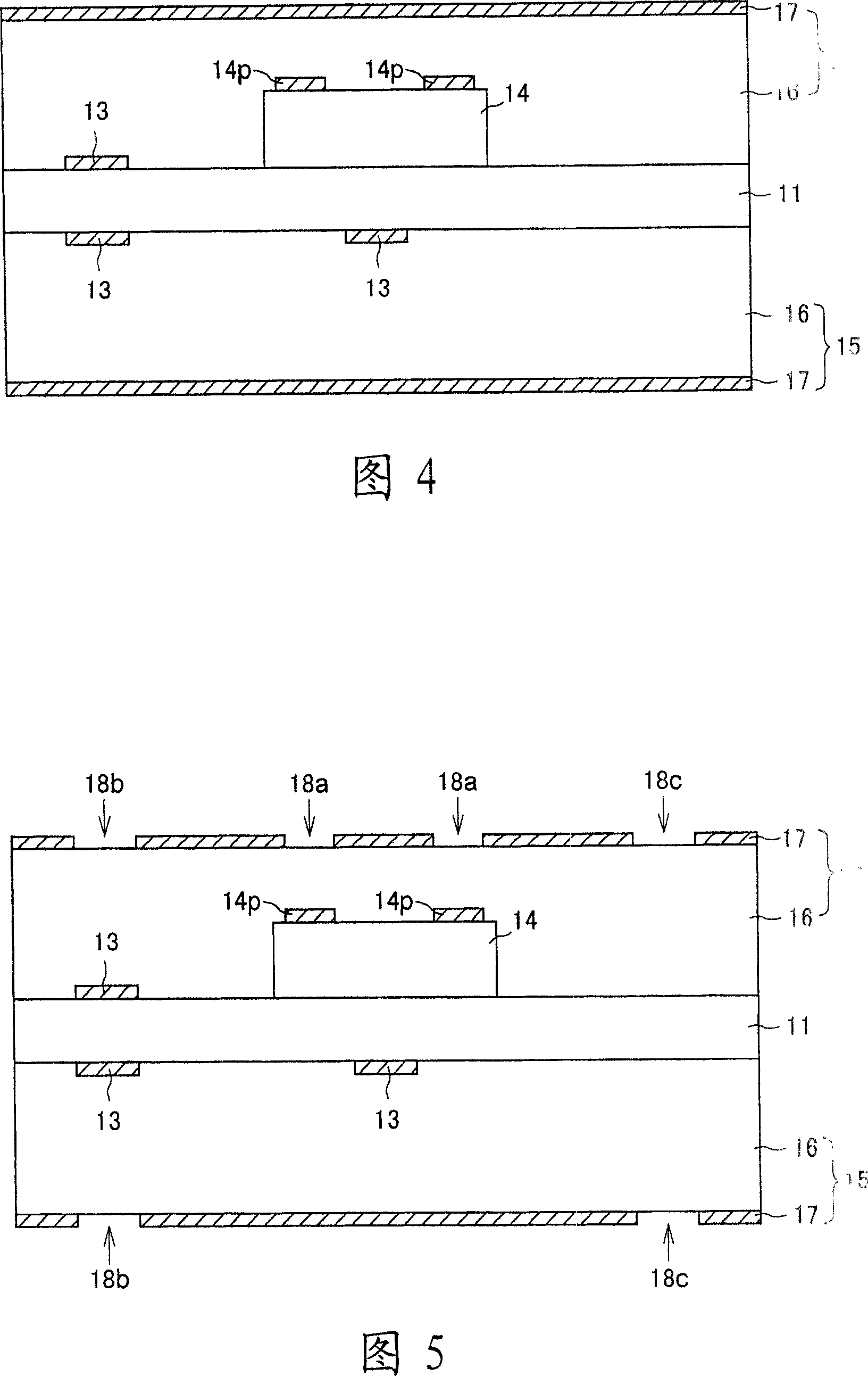

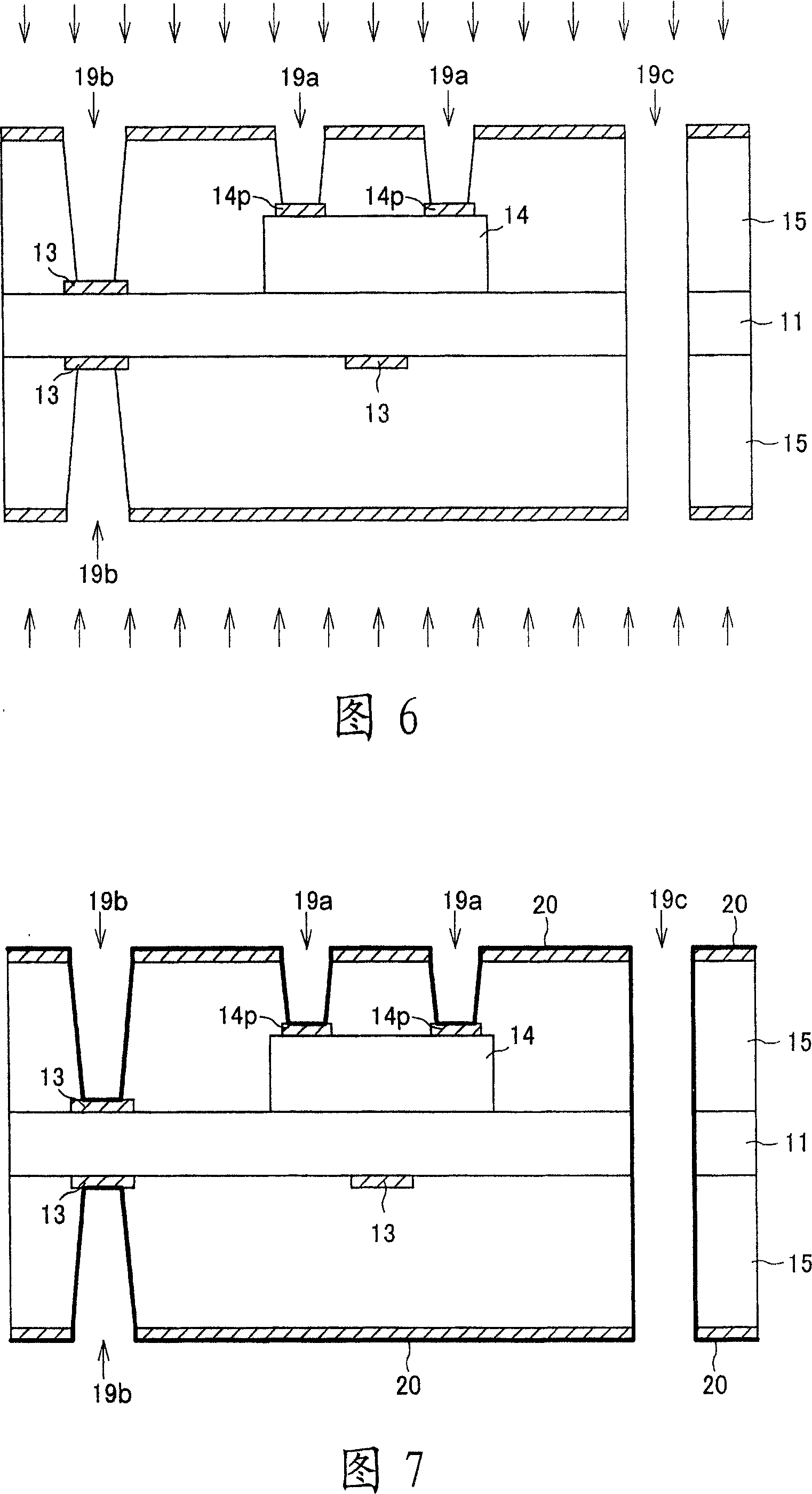

[0033] Preferred embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0034] The method of manufacturing an IC-embedded substrate according to this embodiment can be applied to both the case of mounting a semiconductor IC chip on a "core substrate" constituting an IC-embedded substrate and the case of mounting a semiconductor IC chip on a "buildup layer" formed on a core substrate. Two situations. First, a first embodiment in which a semiconductor IC chip is mounted on a core substrate will be described in detail with reference to FIGS. 1 to 9 .

[0035]In the manufacture of the IC-embedded substrate of this embodiment, first, the core substrate 11 ( FIG. 1 ) is prepared. The core substrate 11 functions to secure the mechanical strength of the entire IC-embedded substrate and is not particularly limited, but for example, a resin substrate with copper foil on both sides can be used. As the material of the resin ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More