Liquid crystal display device and fabrication method thereof

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

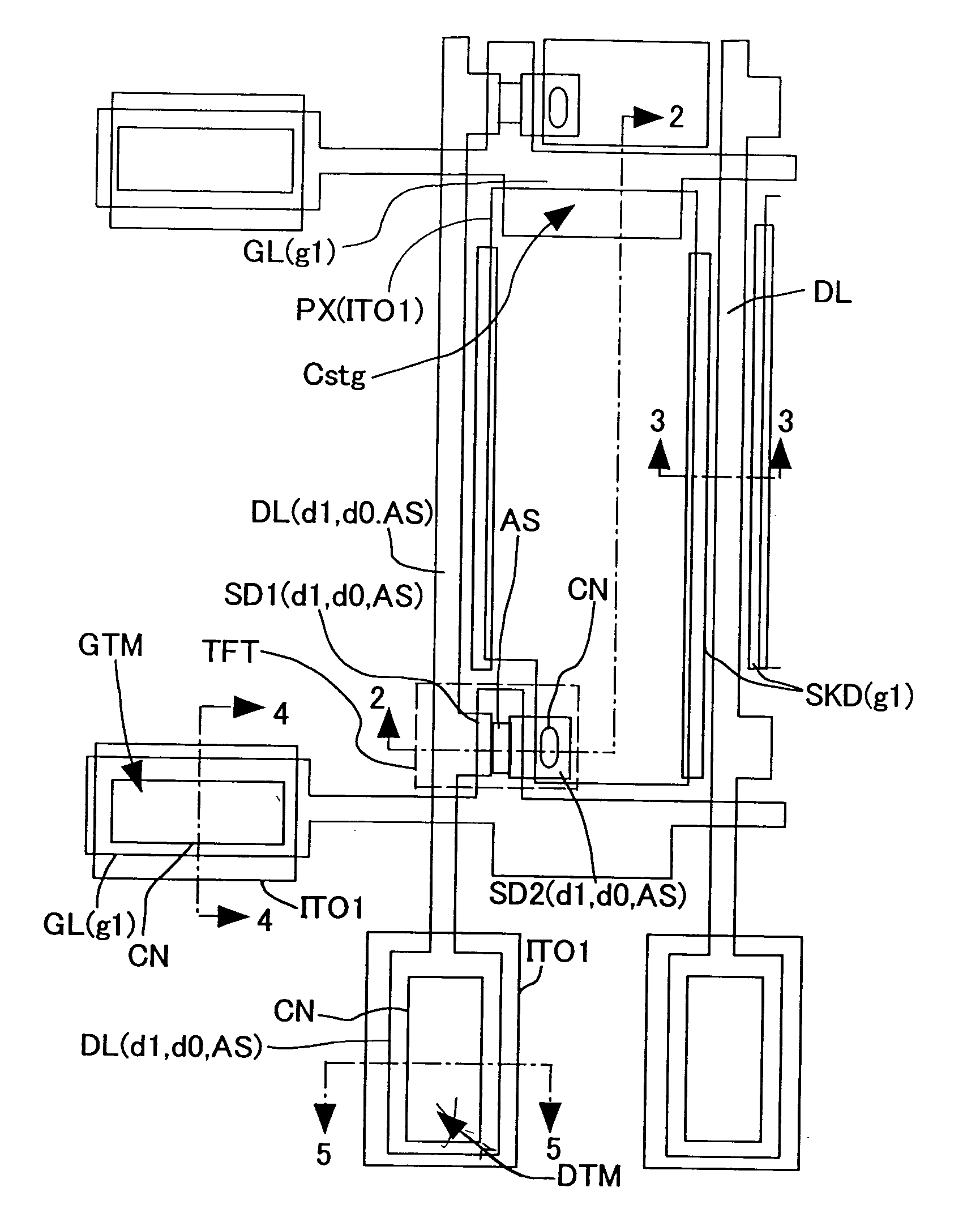

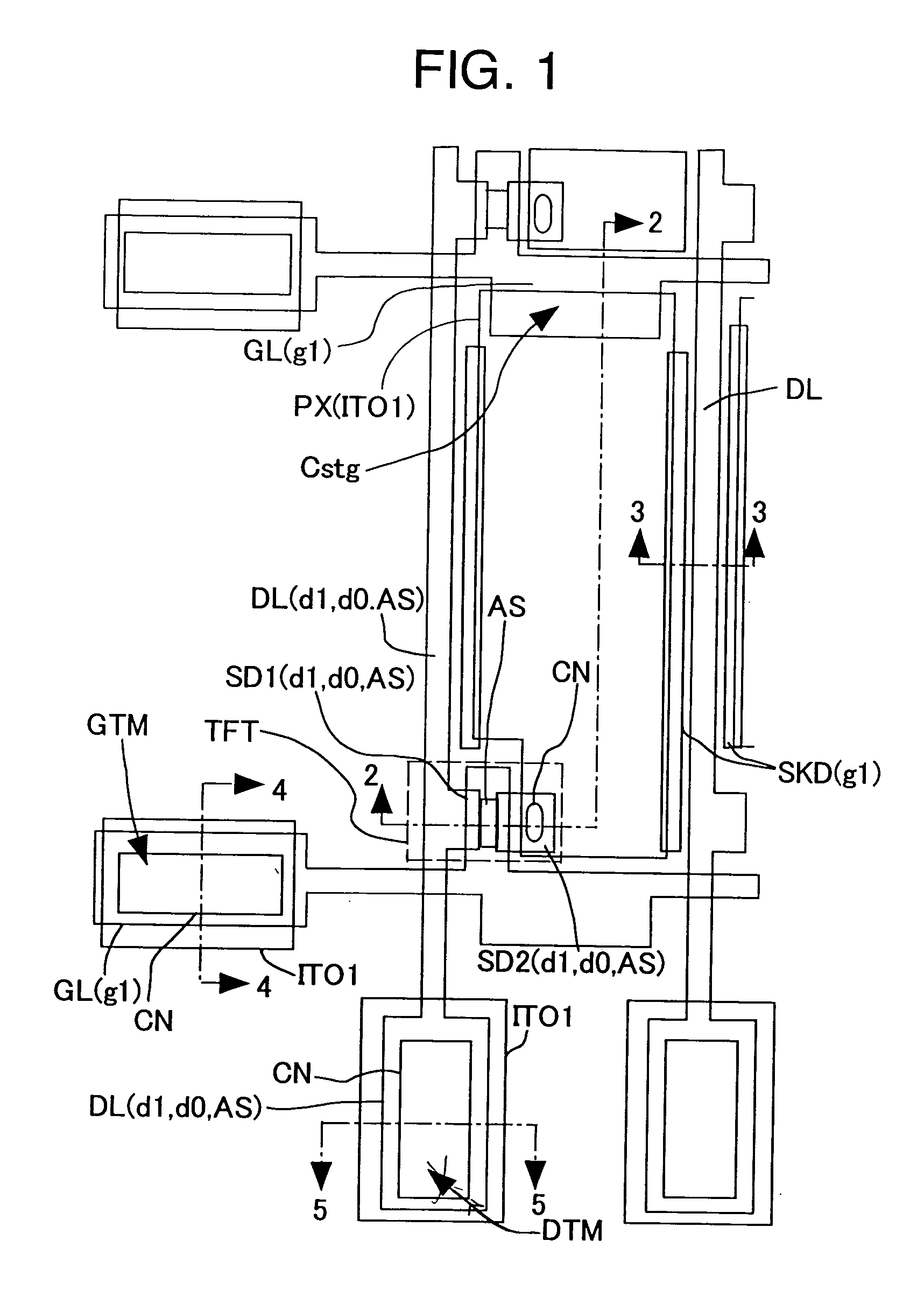

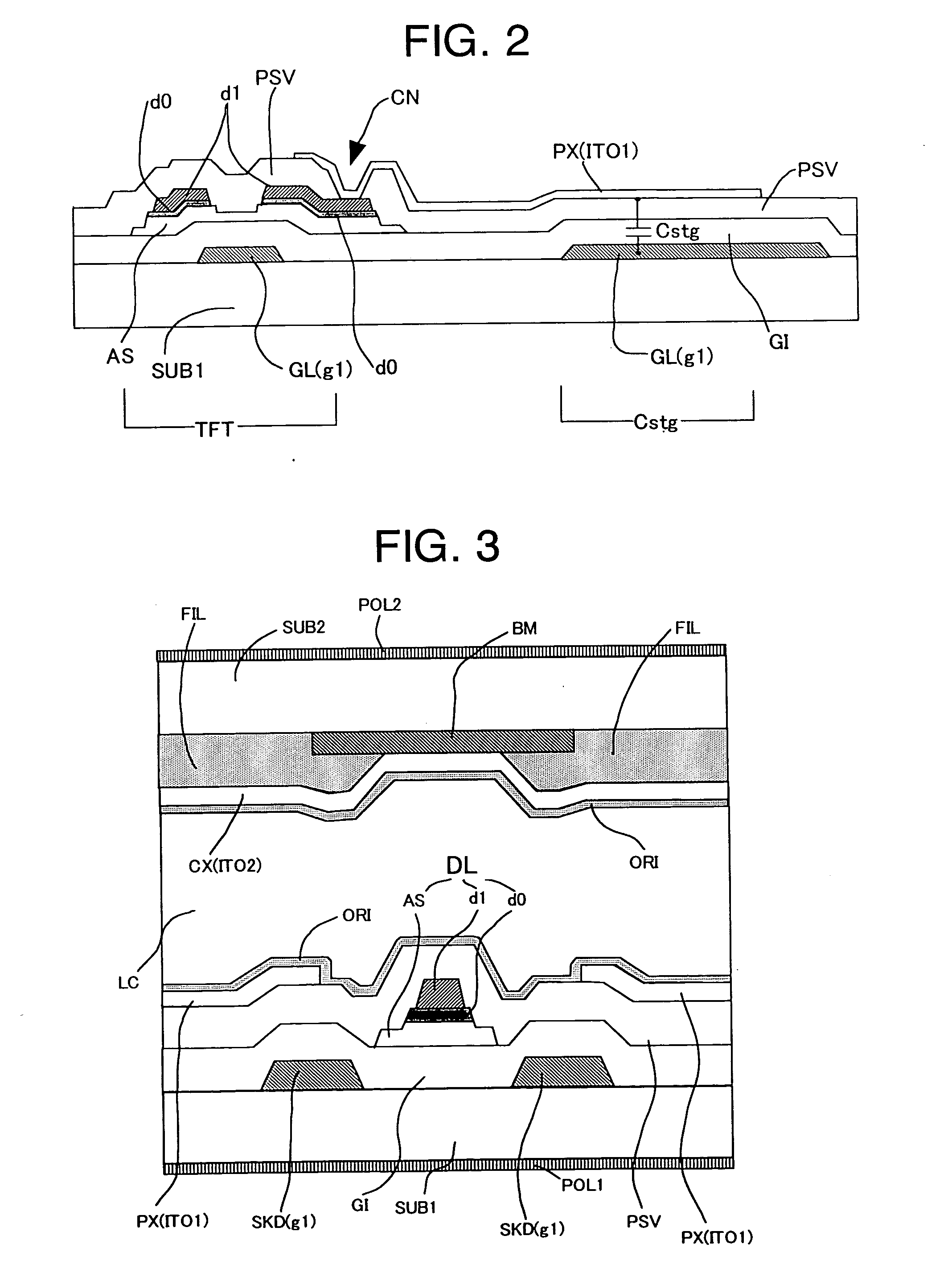

embodiment 1

[0106] In the construction of this TFT section, one problem to be solved in terms of manufacturing yield factor is that the material of the transparent conductive film ITO1 which constitutes the pixel electrode PX, for example, ITO, does not have sufficient adhesion to the stepped undersurface, so that the transparent conductive film ITO1 may be easily disconnected during etching processing. Particularly in the cross-sectional structure shown in FIG. 2, the source electrode SD2 that lies near the contact hole CN has a large stepped interval because the a-Si films AS and d0 and the metal electrode d0 are stacked. In Embodiment 1, the a-Si contact film d0 projects from an overlying metal material d1 which constitutes the drain electrode SD1, and the a-Si channel film AS projects from the overlying a-Si contact film d0. The resultant steps constitute a staircase-like structure which is formed by the metal material d1, a semiconductor film including the a-Si contact film d0, and the por...

embodiment 2

[0133] Cross-sectional views of the fabrication process of the second photo-process of Embodiment 2 are shown in FIGS. 12A to 12C. The gate wiring line GL is formed on the TFT glass substrate SUB1, and an SiN film which becomes the gate insulating film GI, an i-type a-Si film which becomes the a-Si channel film AS and an n+-type a-Si film which becomes the a-Si contact film d0 are continuously deposited in this order on the TFT substrate SUB1 by a CVD method. Then, the metal film d1 for the source and drain electrodes SD1 and SD2 as well as the video signal line DL is deposited by a sputtering method without going through the photo-process (FIG. 12A).

[0134] Then, a photoresist is applied to the metal film d1, and is exposed and developed by using a photomask having a nontransparent area, a semitransparent area and a transparent area as shown in FIG. 7A of Embodiment 1, thereby forming a resist pattern PRES1 which is a thick portion corresponding to the nontransparent mask area and a...

embodiment 3

[0144] Cross-sectional views of the fabrication process of the third photo-process of Embodiment 3 are shown in FIGS. 15A to 15C. The gate wiring line GL is formed on the TFT glass substrate SUB1, and an SiN film which becomes the gate insulating film GI, an i-type a-Si film which becomes the a-Si channel film AS and an n+-type a-Si film which becomes the a-Si contact film d0 are continuously deposited in this order on the TFT substrate SUB1 by a CVD method. Then, the metal film d1 for the source and drain electrodes SD1 and SD2 as well as the drain wiring line DL is deposited by a sputtering method without passing through the photo-process. Then, the source and drain electrodes SD1 and SD2 are processed by a halftone exposure and development method, and a half-etched island-shaped a-Si channel film AS is formed in the section of the charge-holding capacitance Cstg section. Moreover, photo processing is done up to the TFT substrate SUB1 coated with the SiN protective film PSV by a C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More