Semiconductor memory device with ability to adjust impedance of data output driver

a memory device and data output technology, applied in the field of semiconductor memory devices, can solve the problem that the calibration control operation of ocds has not developed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0072] Hereinafter, a semiconductor memory device in accordance with the present invention will be described in detail referring to the accompanying drawings.

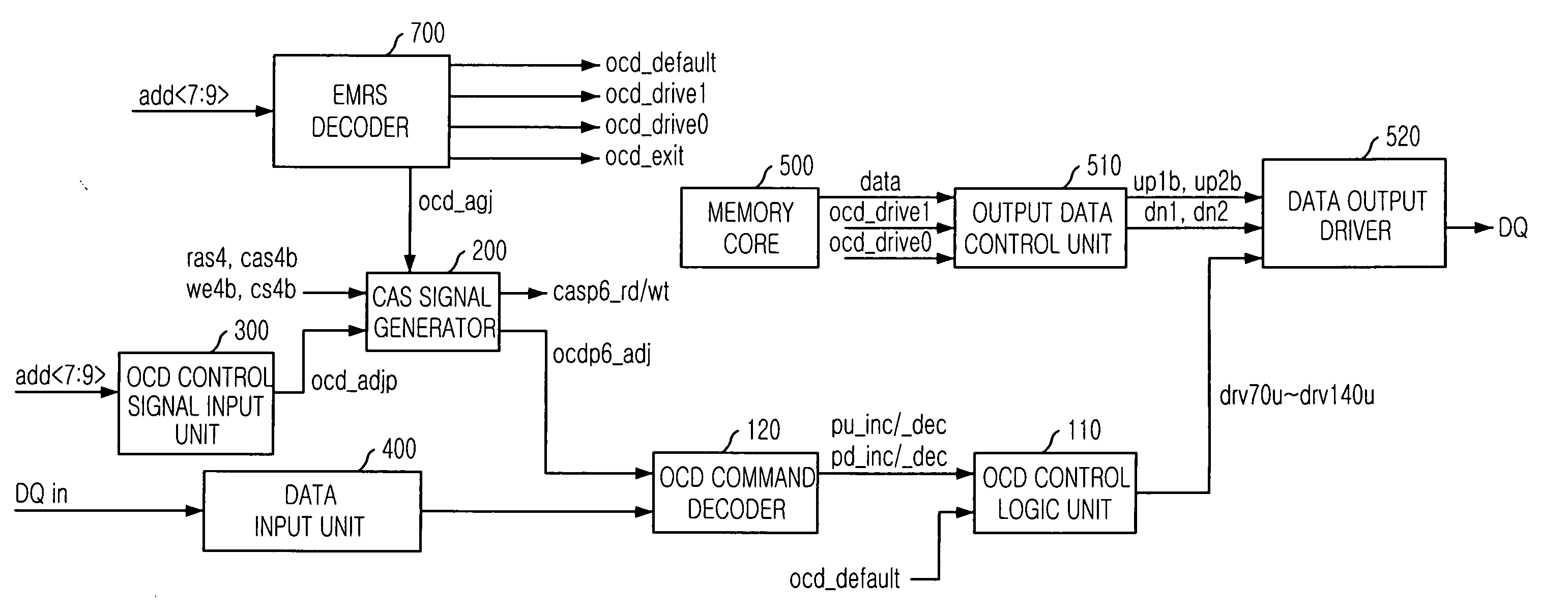

[0073]FIG. 5 is a block diagram showing a semiconductor memory device in accordance with the present invention.

[0074] As shown, the synchronous semiconductor memory device includes an extended mode register set (EMRS) decoder 700, a column address strobe (CAS) signal generator 200, an off chip driver (OCD) control signal input unit 300, a data input unit 400, an OCD command decoder 120, an OCD control logic unit 110, a memory core block 500, an output data control unit 510 and a data output driver unit 520.

[0075] The data input unit 400 latches and aligns plural data inputted through a data input / output pad during a data access operation and the data input unit 400 latches and aligns an OCD control code inputted through the data input / output pad during an OCD calibration control operation. The data output driver 520 outputs ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com