Body-contacted semiconductor structures and methods of fabricating such body-contacted semiconductor structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

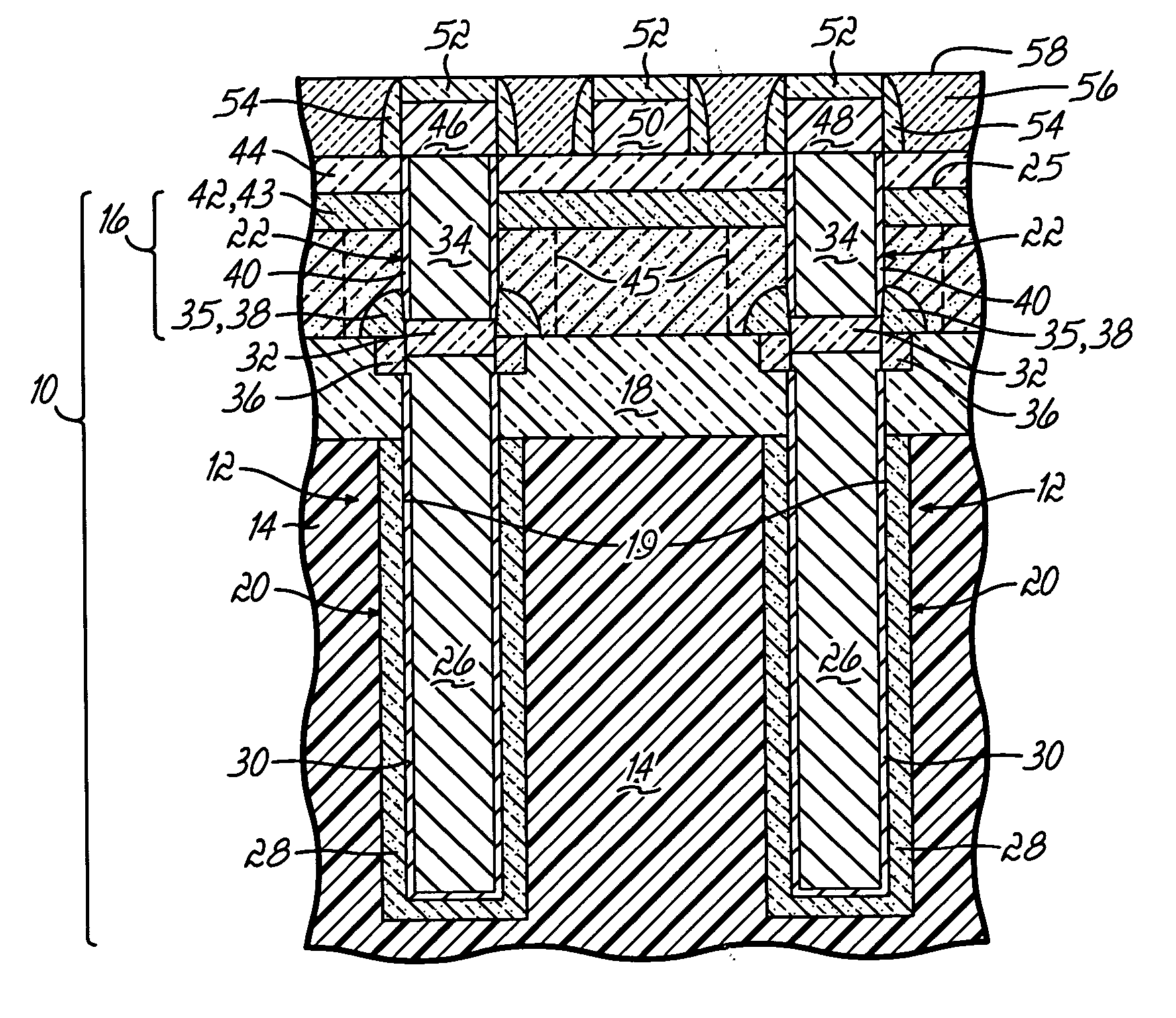

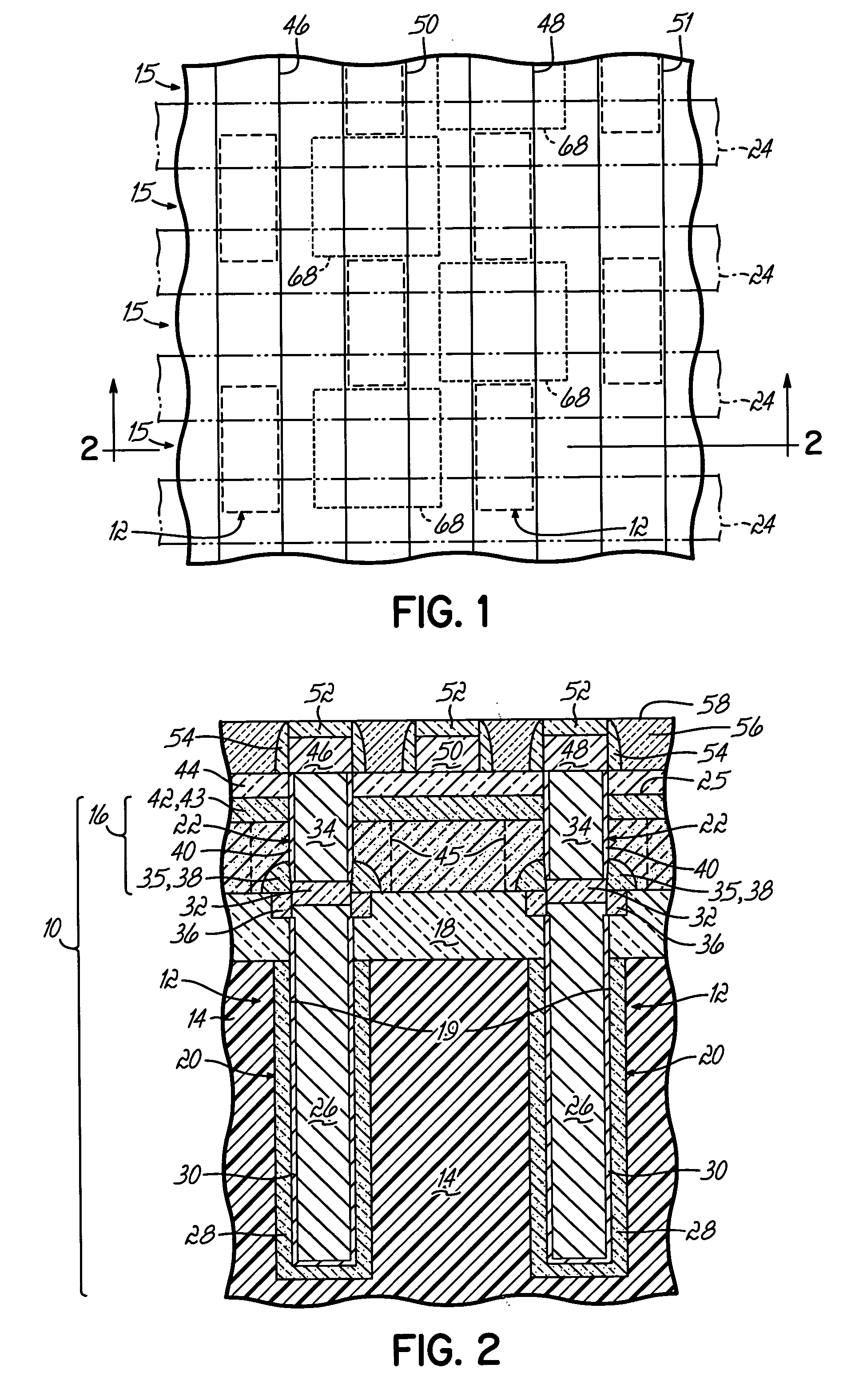

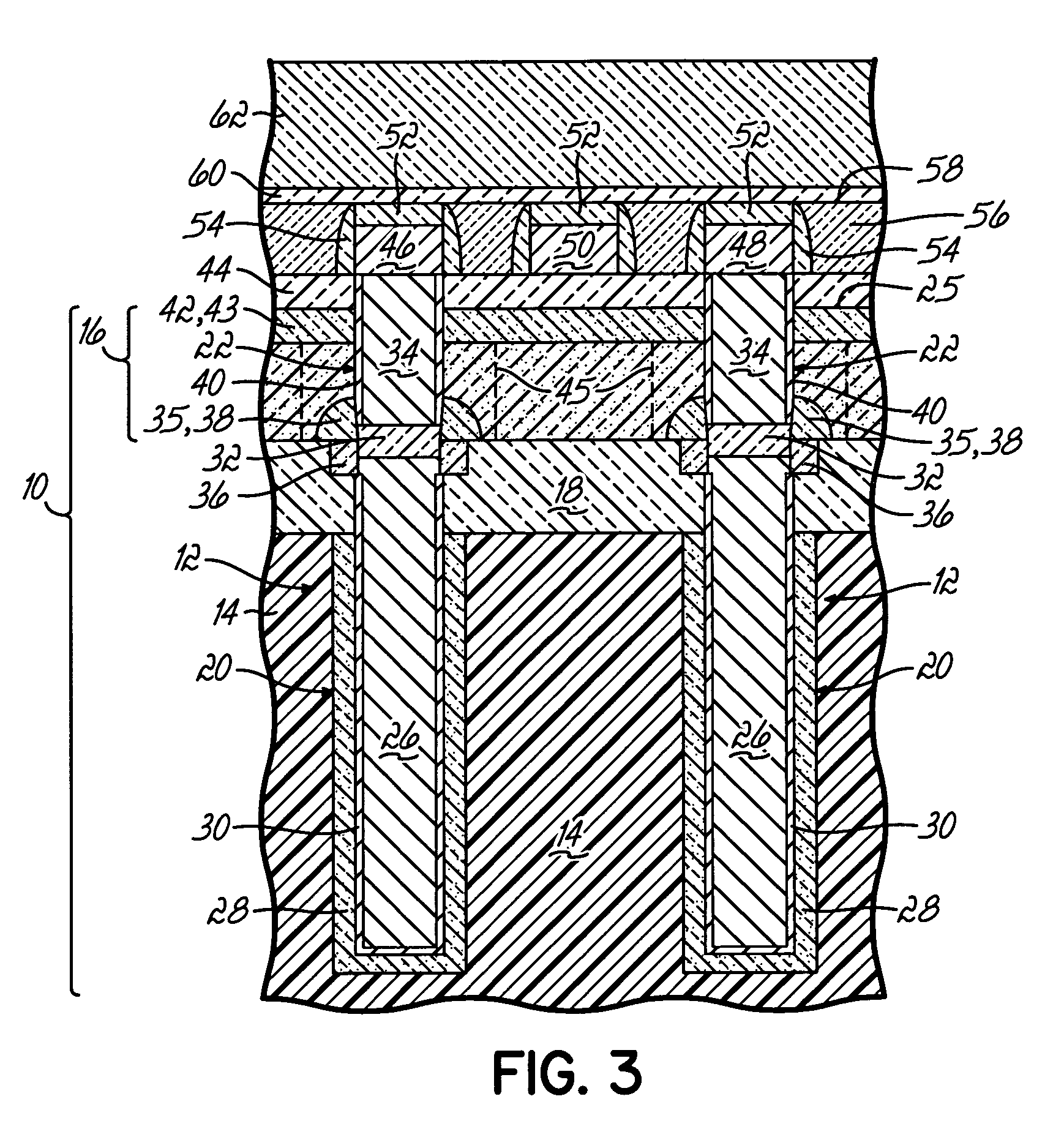

[0021] The present invention provides a semiconductor structure including an array of vertical memory cells built using semiconductor-on-insulator (SOI) technology, as well as methods of making such semiconductor structures. Specifically, the access device for at least one vertical memory cell and, typically, every vertical memory cell in the memory cell array has an associated relatively high-resistance body contact established through the buried insulating or dielectric layer separating the floating SOI body of an SOI wafer, in which the access device is built, from the underlying semiconductor substrate. The present invention may be particularly applicable and beneficial for merged isolation and node trench (MINT) memory cells, although the invention is not so limited. The requisite high resistance for the body contact may be achieved by creating a localized silicon rich oxide (SRO) region of relatively high resistance in the buried dielectric layer. The present invention will no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More