Fabrication Method of Semiconductor Integrated Circuit Device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

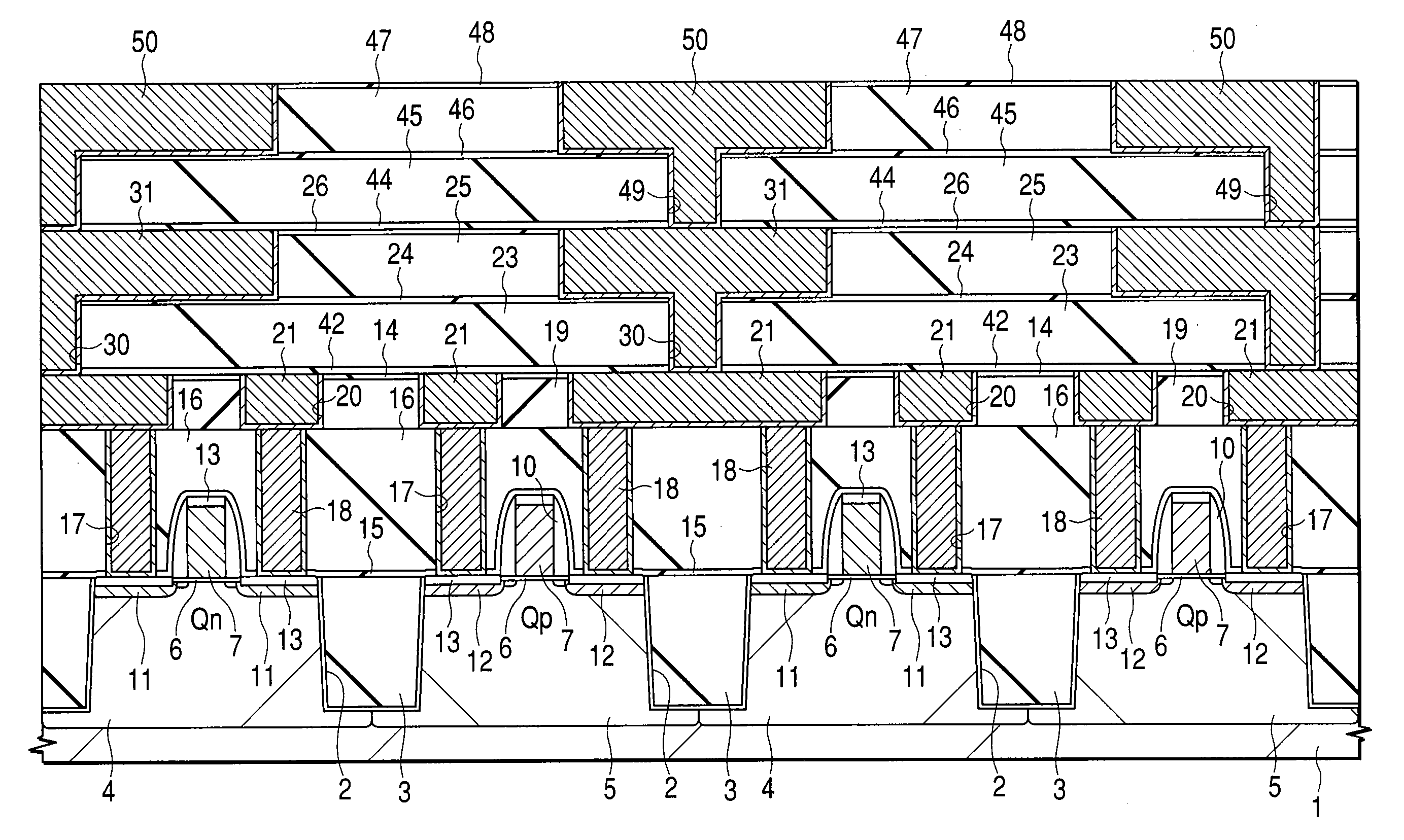

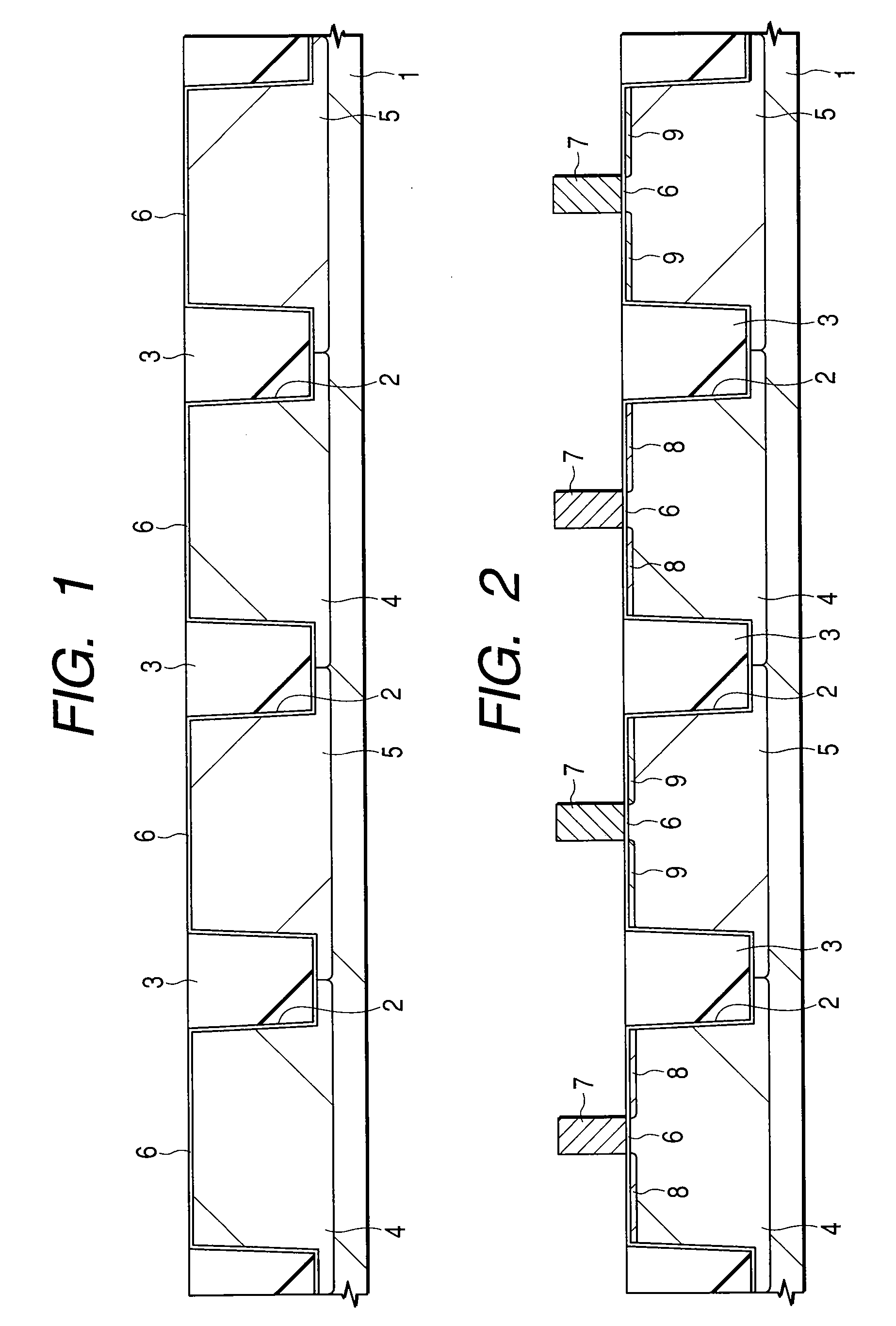

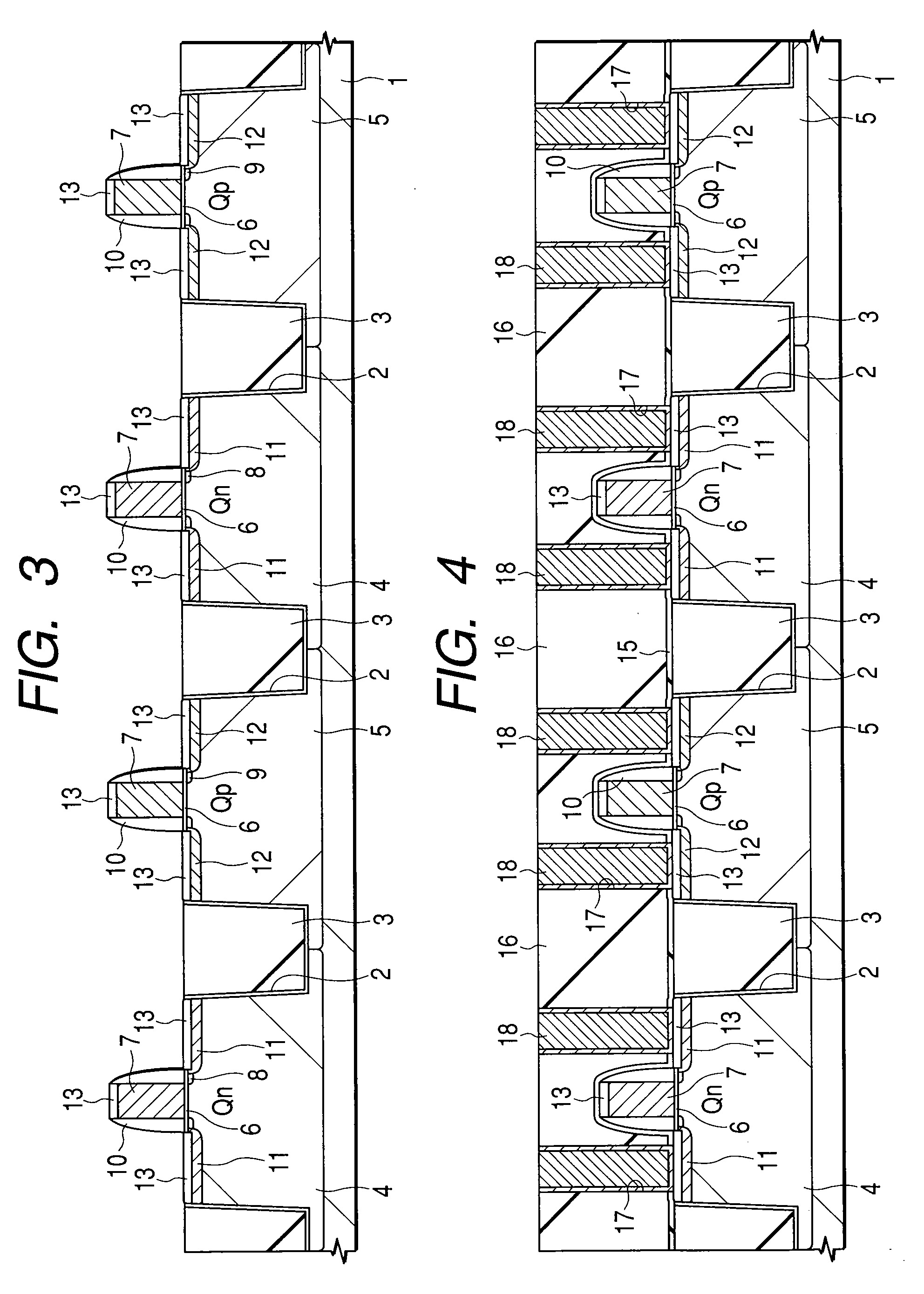

[0065] A process of fabricating a CMOS-LSI, which is an embodiment of the present invention, will be described in order of steps thereof, referring to FIGS. 1 to 15.

[0066] As illustrated in FIG. 1, first, element-isolating grooves 2 are made in a semiconductor substrate (hereinafter referred to as a substrate or a wafer) made of p-type monocrystal silicon having a resistivity of, for example, about 1 to 10 Ωcm. The element-isolating grooves 2 are made by etching element-isolating regions in the substrate 1 to make grooves, depositing a silicon oxide film 3 on the substrate 1 including the inside space of the grooves by CVD and subsequently polishing the silicon oxide film 3 outside of the grooves chemically and mechanically.

[0067] Next, boron is ion-implanted into some parts of the substrate 1, and phosphorous is ion-implanted into some other parts thereof to form p-type wells 4 and n-type wells 5. Thereafter, the substrate 1 is subjected to steam-oxidization to form a gate oxidiz...

embodiment 2

[0111] The following will describe, as the present embodiment, a case in which a siloxane (SiO)-based, low dielectric constant (Low-k) insulating film is used as an interlayer insulating film material and silicon nitride films are used as a diffusion barrier layer and an etching stopper layer. In the present embodiment, a SiOF film having a dielectric constant of 3.5 is used as the interlayer insulating film material. However, it is allowable to use some other inorganic or organic siloxane-based material (organic glass type insulating film), for example, HSQ (hydrogen silsesquioxane), MSQ (methyl silsesquioxane), porous HSQ, or porous MSQ.

[0112] Examples of the HSQ-based material include “OCD T-12” (made by Tokyo Ohka Kogyo Co., Ltd., dielectric constant=3.4-2.9), “FOx” (made by Dow Corning Co. in USA, dielectric constant=2.9), and “OCL T-32” (made by Tokyo Ohka Kogyo Co., Ltd., dielectric constant=2.5). Examples of the MSQ-based material include “OCD T-9” (made by Tokyo Ohka Kogyo...

embodiment 3

[0129] A process of fabricating a CMOS-LSI according to the present embodiment will be described in order of the steps thereof, referring to FIGS. 23 to 33.

[0130] As illustrated in FIG. 23, n-channel type MISFETs Qn and p-channel type MISFETs Qp are formed over a substrate 1. Thereafter, Cu interconnections 21 as a first layer are formed thereon. A process up to this step is the same as illustrated in FIGS. 1 to 6 about Embodiment 1.

[0131] Next, as illustrated in FIG. 24, a silicon carbonitride (SiCN) film 42, an organic insulating film 23, a silicon oxide film 24, an organic insulating film 25, a silicon oxide film 26 and a silicon carbonitride film 43 are successively deposited over the Cu interconnections 21. The silicon oxide films 24 and 26 are deposited by CVD. The organic insulating films 23 and 25 are formed by depositing an insulating material having a smaller dielectric constant than silicon oxide, for example, the above-mentioned “SiLK” or “FLARE”, by spin coating. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More