Semiconductor device and method of manufacturing the same

a semiconductor and film technology, applied in the field of semiconductor devices, can solve the problems of affecting the performance of transistors, difficult implementation, and the speed at which the tcs-sin film is formed, and achieves the effect of reducing the cost of production, and improving the performance of the transistor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

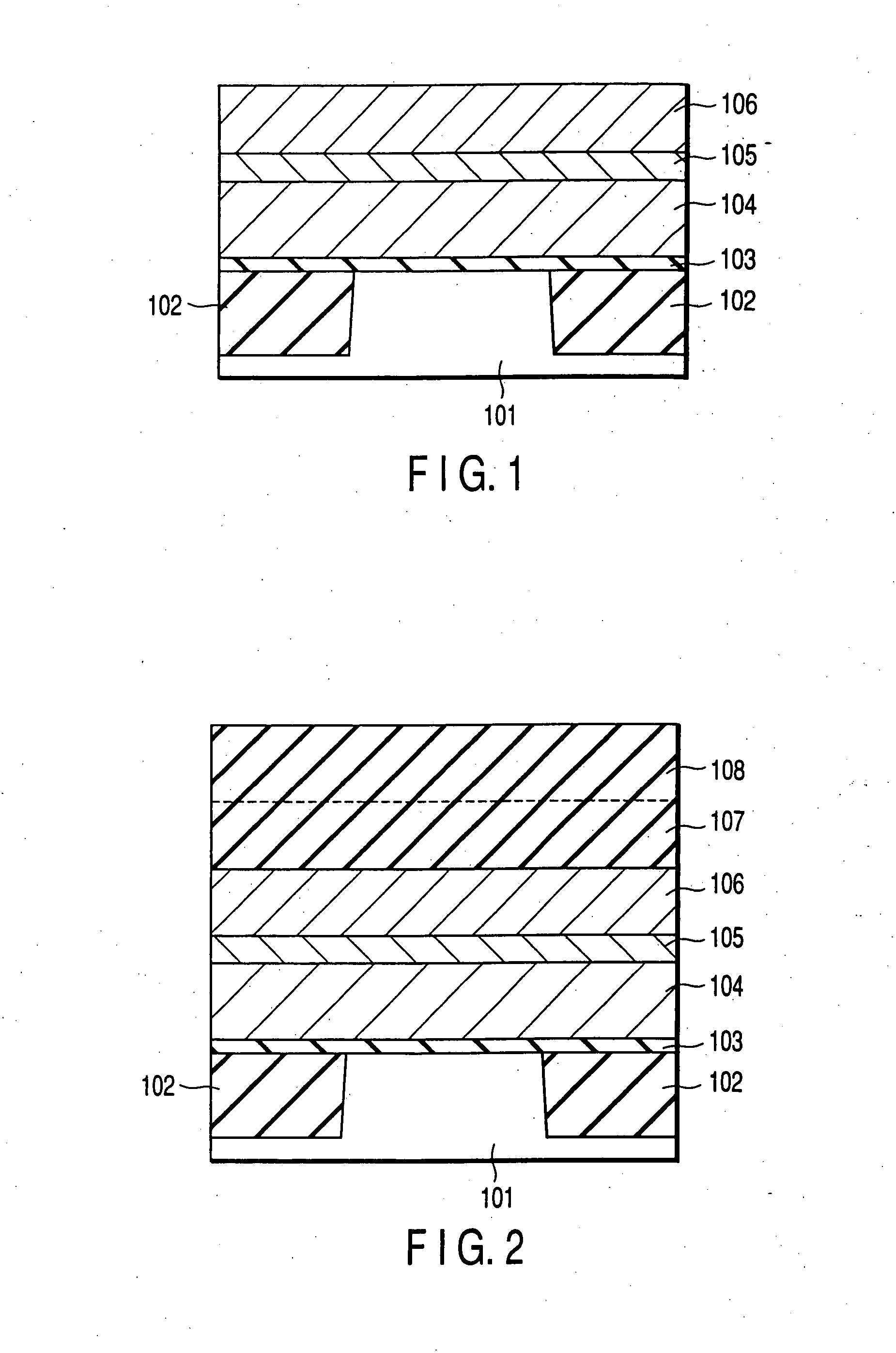

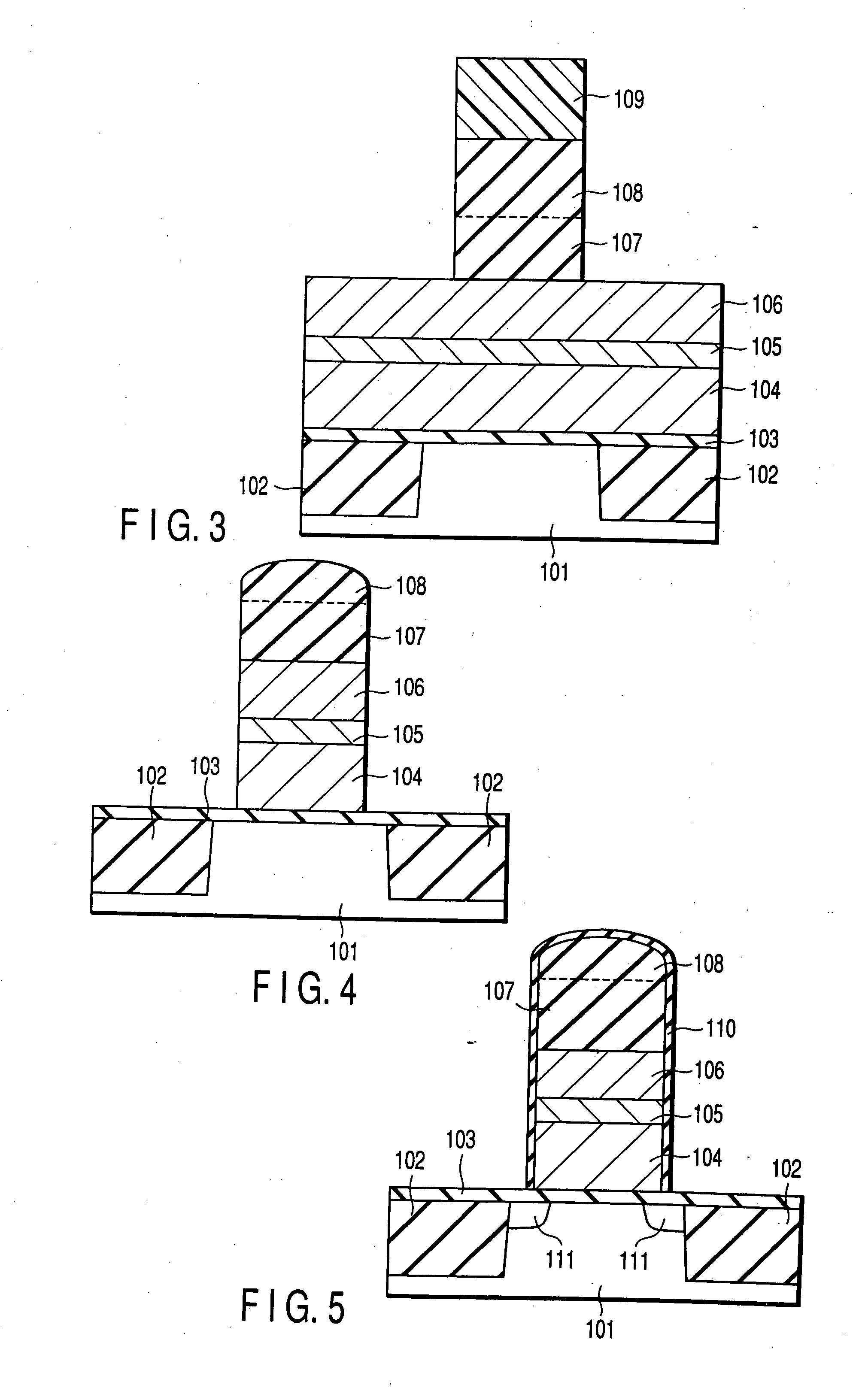

[0060] FIGS. 1 to 5 are sectional views showing a manufacture method for a semiconductor device (MIS transistor) according to a first embodiment of the present invention.

[0061] First, as shown in FIG. 1, an isolation region 102 and a gate insulating film 103 are formed on a silicon substrate 101. The gate insulating film 103 is a silicon oxynitride film of 4.5 nm thickness. Subsequently, a stacked structure composed of an amorphous silicon film 104 (70 nm), a tungsten nitride film 105 (5 nm), and a tungsten film 106 (40 nm) is formed on the gate insulating film 103 as a gate electrode. The amorphous silicon film 104 is doped with p-type impurities in a PMOS region and with n-type impurities in an NMOS region. For example, boron ions are implanted in the PMOS region at 5 keV over 5×1014 to 1×1016 cm−2, and phosphorous ions are implanted in the NMOS region at 10 keV over 5×1014 to 1×1016 cm−2. Thus, the amount of boron introduced into the PMOS gate electrode is more than 1×1019 / cm3 a...

embodiment 2

[0088] FIGS. 8 to 12 are sectional views showing a manufacture method for a semiconductor device (MIS transistor) according to a second embodiment of the present invention.

[0089] First, as shown in FIG. 8, the following components are formed on a silicon substrate 121 using a normal method: an isolation region (not shown), a gate insulating film 124, a gate electrode 125, a side wall insulating film 126, an extension region 123, and a source / drain region 122. The gate electrode 125 is formed of an amorphous silicon film. The amorphous silicon film is doped with p-type impurities in a PMOS region and with n-type impurities in an NMOS region. The impurities are implanted in the amorphous silicon film simultaneously with the implantation of ions in the source / drain region 122. For example, boron ions are implanted in the PMOS region at 7 keV over 5×1014 to 1×1016 cm−2, and arsenic ions are implanted in the NMOS region at 65 keV over 5×1014 to 1×1016 cm−2. The side wall insulating film...

embodiment 3

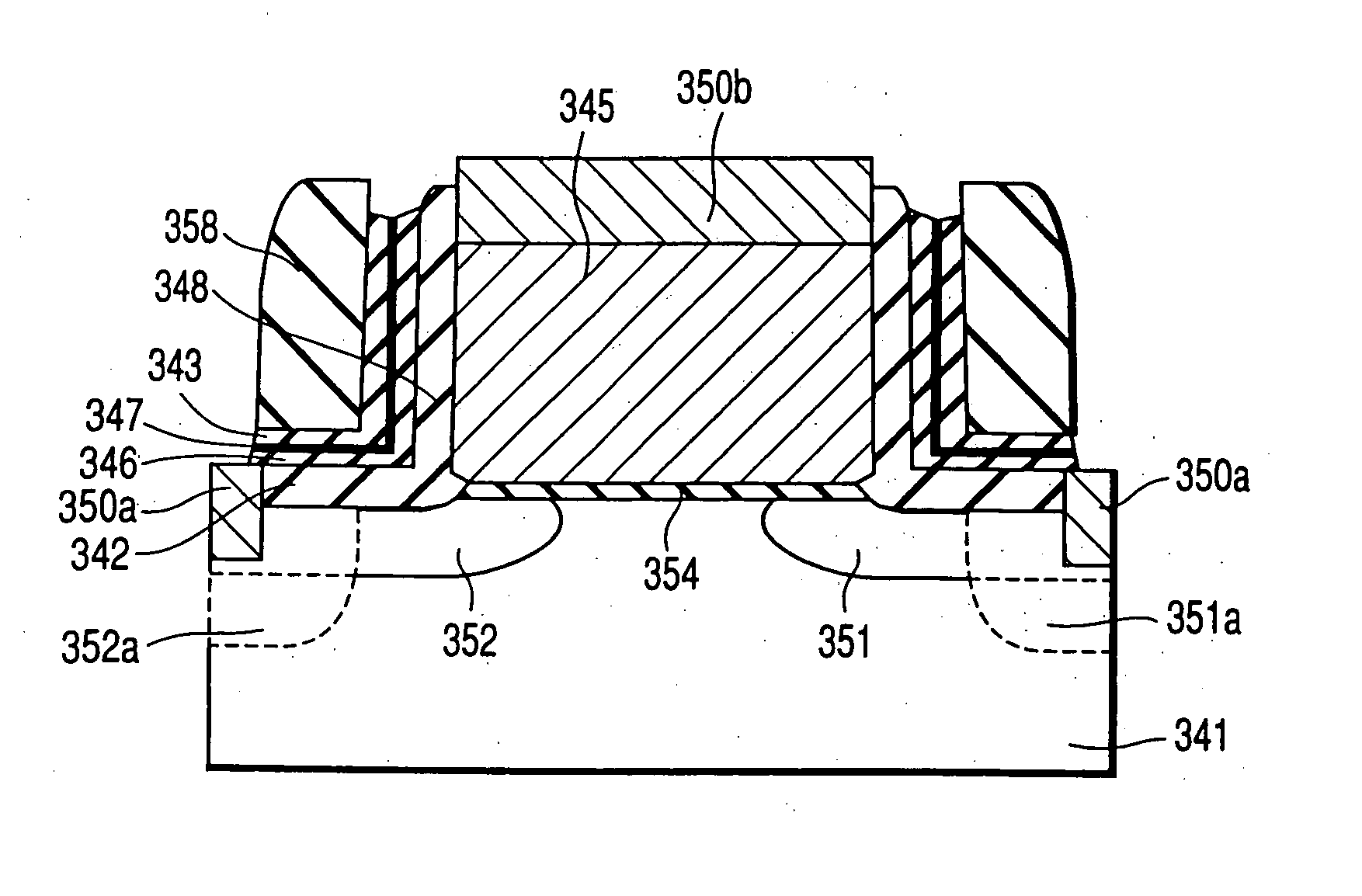

[0096]FIG. 13 is a sectional view showing the structure of a semiconductor device (a non-volatile memory or flash memory) according to a third embodiment of the present invention.

[0097] In FIG. 13, on a silicon substrate 141, the following components are formed: a tunnel insulating film 142, a floating gate 143 acting as a charge storage film, an inter-poly insulating film (an inter-electrode insulating film) 144, a control gate 145 formed of a polysilicon film, and a tungsten silicide film 146. Further, an SiN film 147 is formed on the tungsten silicide film 146, and an SiN film 148 is formed along side walls of a gate structure. At least one of the SiN film included in the inter-electrode insulating film 144, the SiN film 147, and the SiN film 148 has a stacked structure composed of a lower TCS-SiN film and an upper DCS-SiN film. Furthermore, source / drain diffusion layers 149 are formed so as to sandwich a gate structure.

[0098] This embodiment also produces effects similar to th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More