Method for forming silicon-germanium epitaxial layer

a technology of silicongermanium epitaxial layer and silicongermanium epitaxial layer, which is applied in the direction of basic electric elements, electrical apparatus, semiconductor devices, etc., can solve the problems of limiting the integration degree, affecting the yield, and limiting the performance improvement due to device miniaturization, so as to achieve uniformity and enhance throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

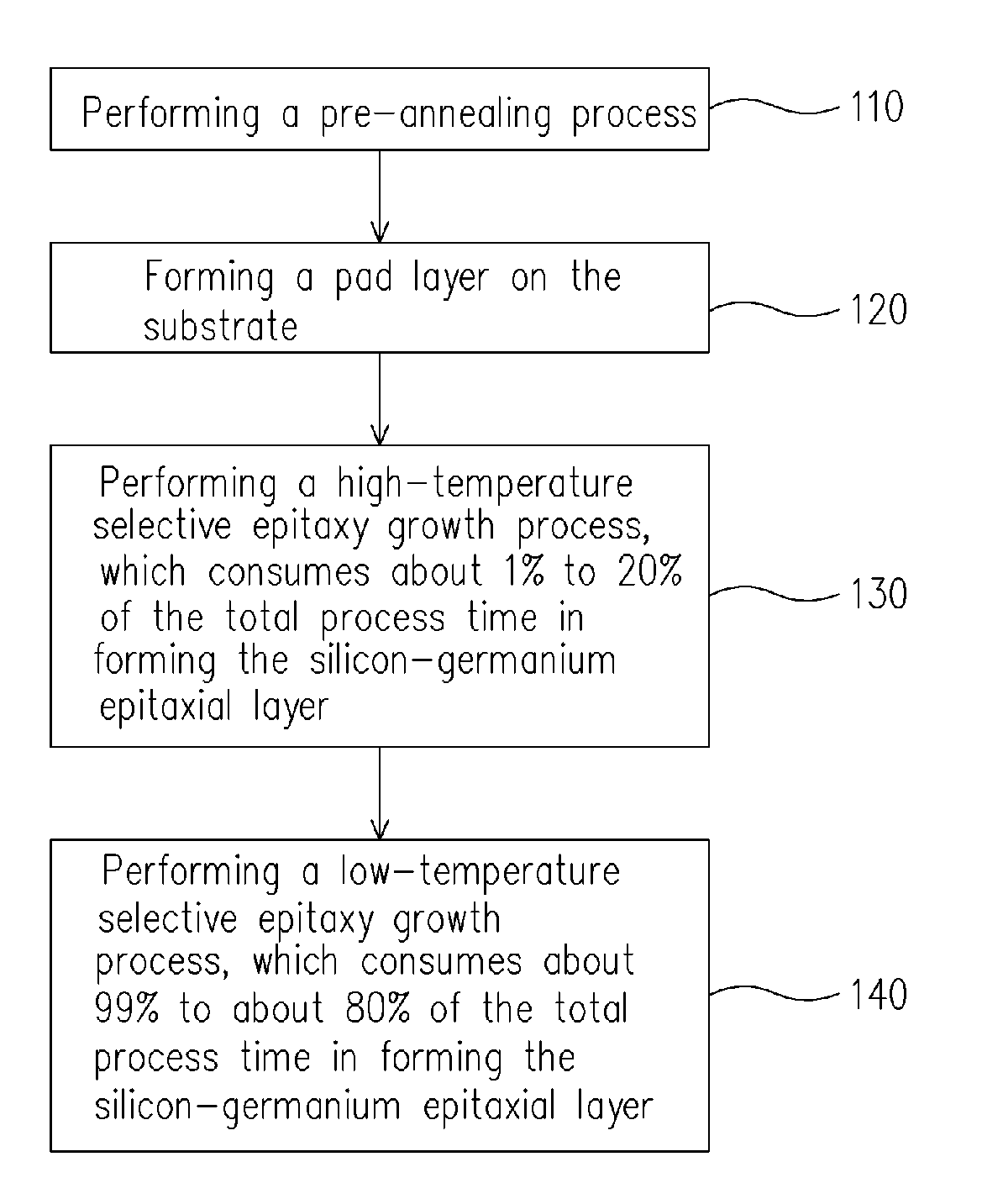

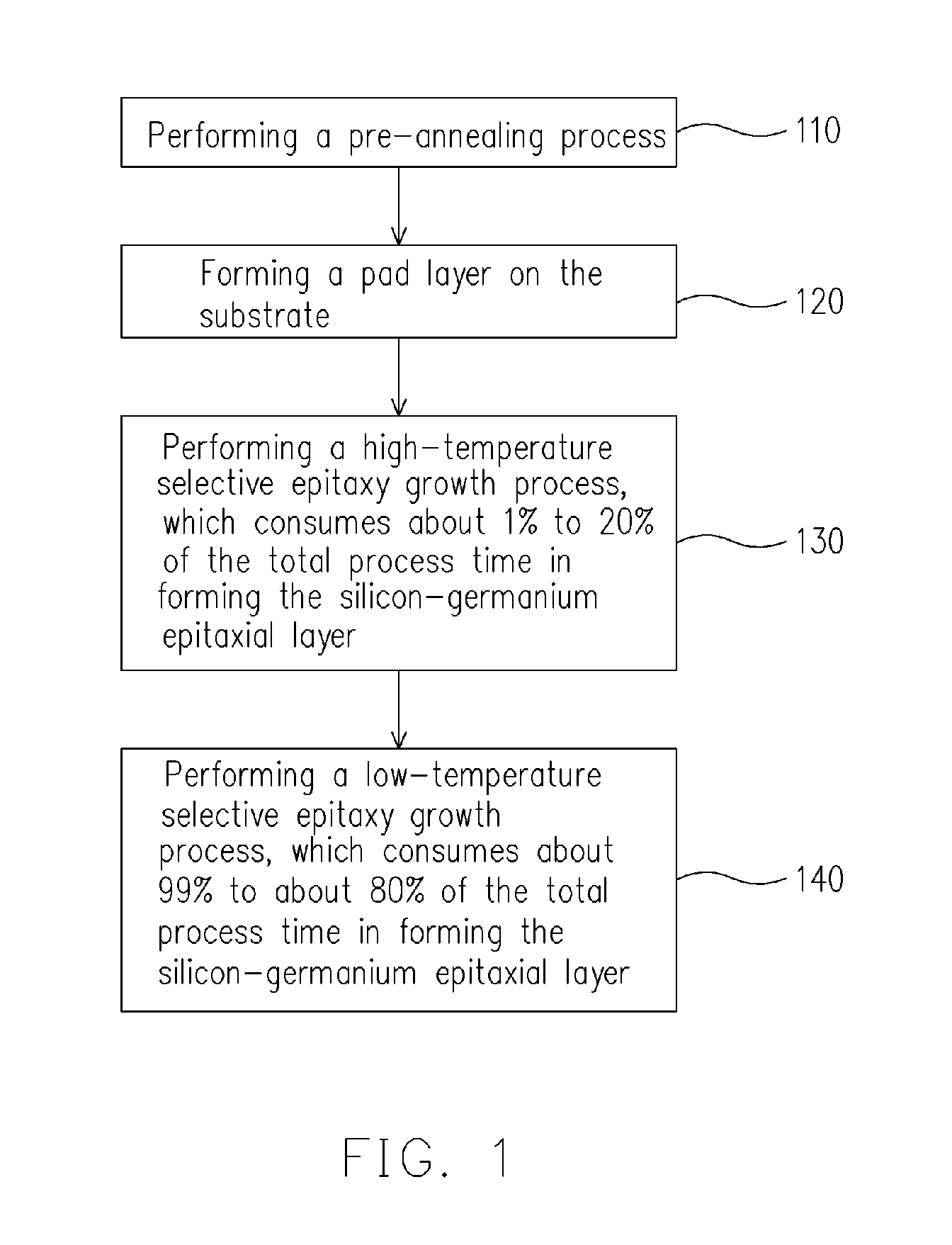

[0034]FIG. 1 is a flow chart of steps in exemplary processes that may be used in the formation of a SiGe layer according to one embodiment of this invention.

[0035]Referring to FIG. 1, in Step 110, a pre-annealing process is performed possibly at about 800° C. A pad layer is then formed on the substrate (Step 120). The pad layer and the substrate are formed with a similar material, such as, silicon.

[0036]Then, a high-temperature SEG process is conducted, consuming about 1% to 20% of the total process time for forming the entire SiGe epitaxial layer. In one embodiment, the high-temperature SEG process consumes about 1% to 15%, preferably about 1% to 10% and more preferably about 3% to 6%, of the total process time. In one embodiment, the high-temperature SEG process is conducted for about 30 seconds.

[0037]The high-temperature SEG process is performed at about 700-900° C., preferably about 750-850° C. and more preferably about 780° C.

[0038]In the above high-temperature SEG process, the...

second embodiment

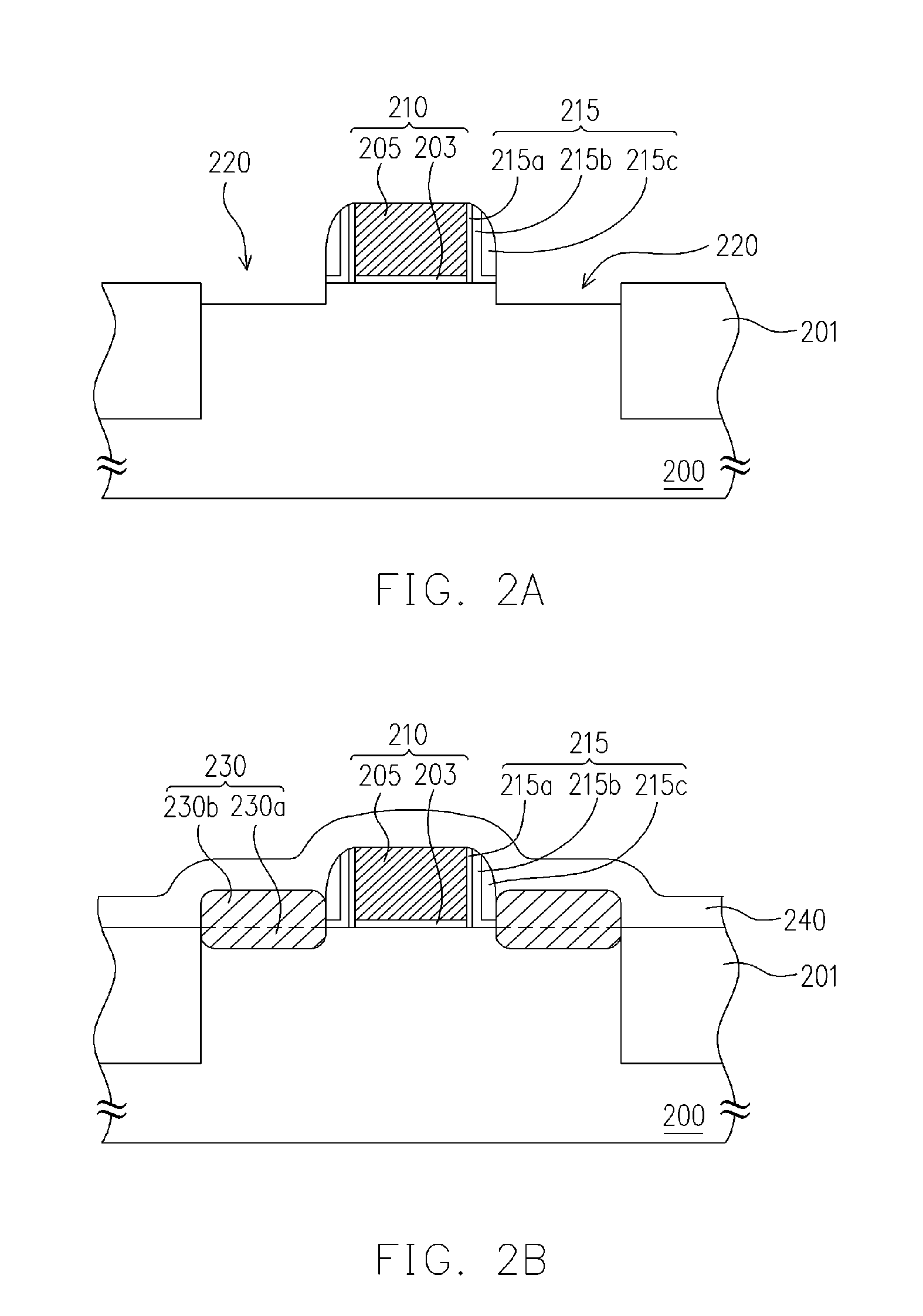

[0048]FIGS. 2A and 2B are cross-sectional views showing selected process steps for forming a SiGe epitaxial layer according to one embodiment of this invention.

[0049]Referring to FIG. 2A, the method for forming a SiGe layer of this invention is applied to the process of a PMOS transistor. An isolation structure 201 is formed in the substrate 200 and a gate structure 210 is formed on the substrate 200, wherein the substrate 200 is, for example, a silicon substrate. The isolation structure 201 includes a shallow trench isolation structure formed with silicon oxide. The gate structure 210 includes, from top to bottom, a gate dielectric layer 203 and a gate electrode 205. The material of the gate dielectric layer 203 may include silicon oxide, while that of the gate electrode 204 may include doped polysilicon, metal, metal silicide or other conductive material. The SiGe epitaxial layer is expected to form above the substrate 200 at both sides of the gate structure 210.

[0050]In one embod...

third embodiment

[0069]FIG. 4 is a flow chart of steps in exemplary processes that may be used in forming a SiGe epitaxial layer according to still another embodiment of this invention.

[0070]Referring to FIG. 4, a surface treatment is performed to the substrate in Step 410, possibly being a pre-cleaning or gas diffusion treatment. A pre-annealing process is then conducted in Step 420, possibly at a temperature of about 800° C.

[0071]In next step (430), a high-pressure SEG process is performed, consuming about 1% to 20%, preferably about 8% to 17%, of the total process time for forming the entire SiGe epitaxial layer.

[0072]The high-pressure SEG process may be performed under a pressure of about 10 Torr or higher at about 650° C. The reactant gas used includes at least a Si-containing gas and a Ge-containing gas. The Si-containing gas may include silane, disilane or dichlorosilane in a flow rate of about 50-500 sccm, preferably about 50-150 sccm. The Ge-containing gas may be germane in a flow rate of a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More