Copper reflow process

a technology of copper reflow and copper, which is applied in the direction of semiconductor/solid-state device manufacturing, basic electric elements, electric apparatus, etc., can solve the problems of aluminum resistance becoming non-negligible, resistance-capacitance (rc) time delay of the circuit, and the deficiency of aluminum and its allows becoming limiting factors in achieving superior performance. , to achieve the effect of improving the adhesion, reducing variability, and better modeling a process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] A manufacturable method for forming a highly reliable, electrical interconnection is described which is particularly well suited for advanced VLSI and ULSI applications. In the following description, numerous specific details such as layer thicknesses, process sequences, times, temperatures, etc. are set forth in order to provide a more thorough understanding of the present invention. It will be obvious, however, to one skilled in the art, that the present invention may be practiced without employing these specific details. In other instances, well-known processes and processing techniques have not been described in detail in order not to unnecessarily obscure the present invention.

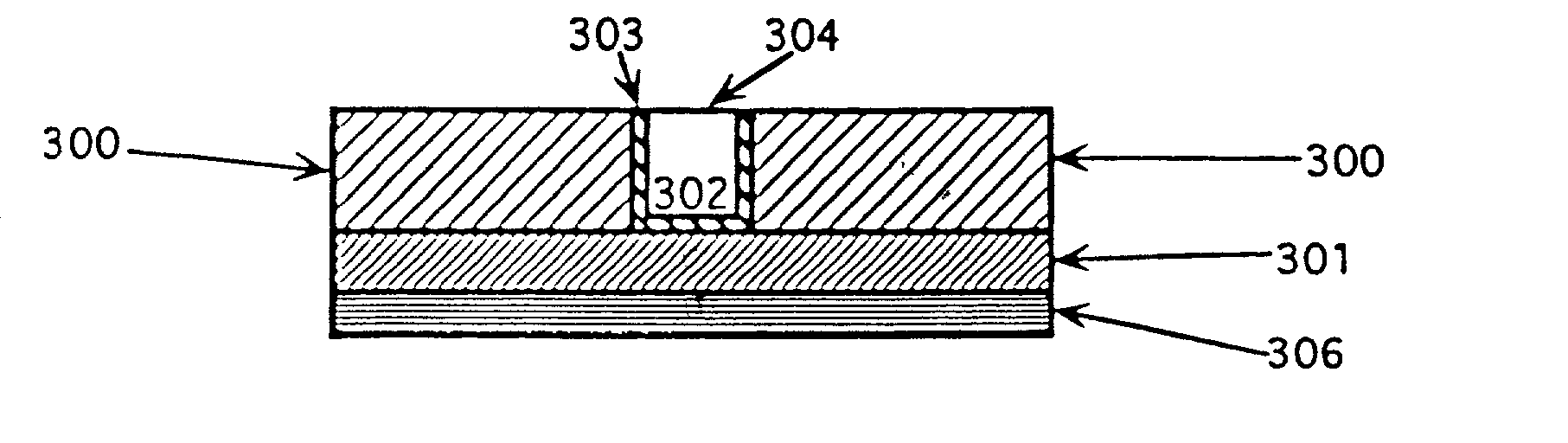

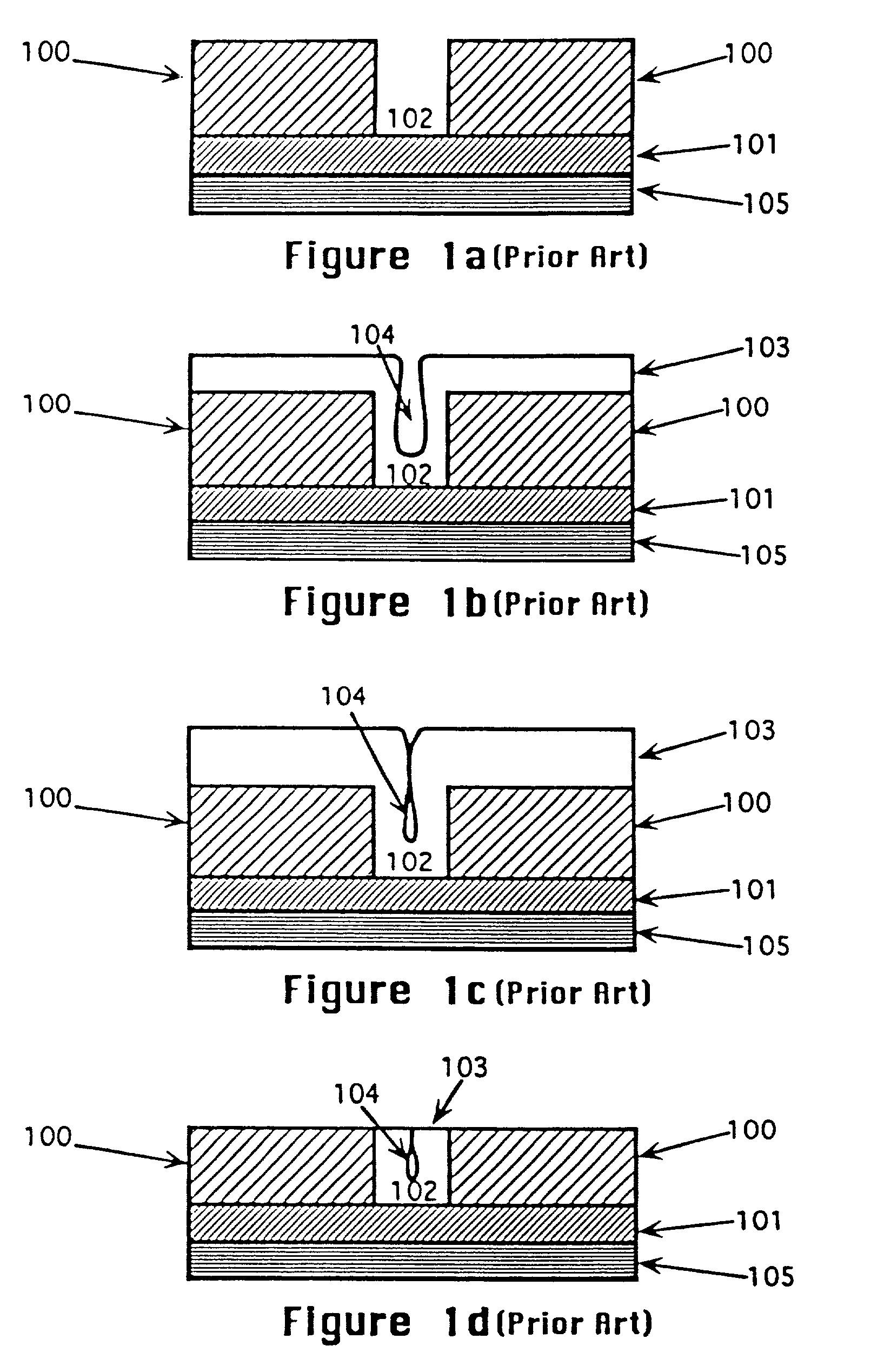

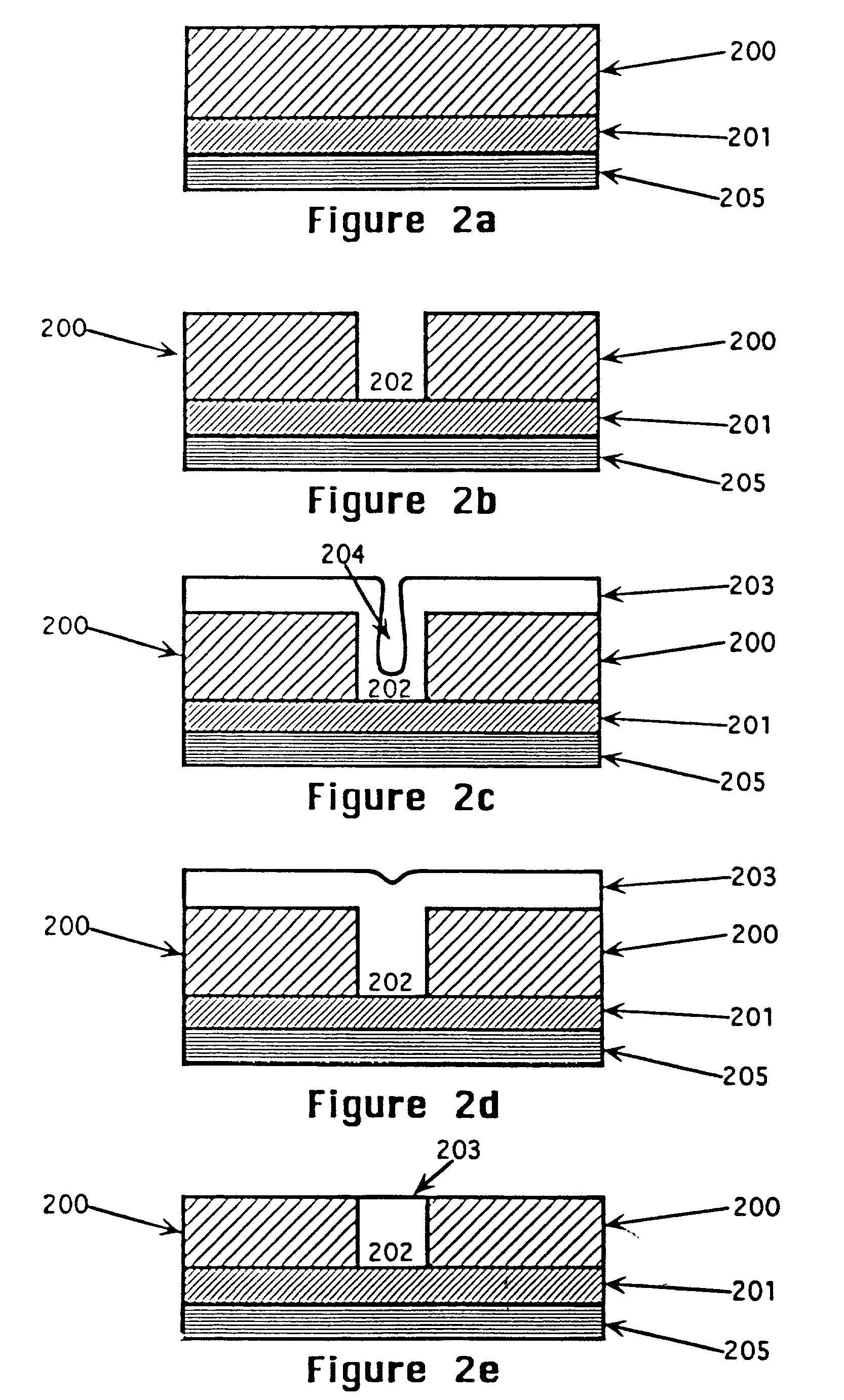

[0032] While diagrams representing a preferred embodiment of the present invention are illustrated in FIGS. 2a-3e, these illustrations are not intended to limit the invention. The specific processes described herein are only meant to help clarify an understanding of the present invention and to ill...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| temperature | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More