Flip chip mounting method and method for connecting substrates

a technology of flip chip and substrate, which is applied in the manufacture of printed circuits, printed circuit aspects, basic electric elements, etc., can solve the problems of difficult to respond to the need, presenting an obstacle to a reduction in the thickness of semiconductors, and serious problems associated with a higher speed and power consumption loss, etc., to achieve stable conductive state, high reliability, and stable conductive state

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066]Referring to the drawings, the embodiments of the present invention will be described herein below. For easier illustration, components having substantially the same functions are designated by the same reference numerals in the drawings shown below. The present invention is not limited to the following embodiments.

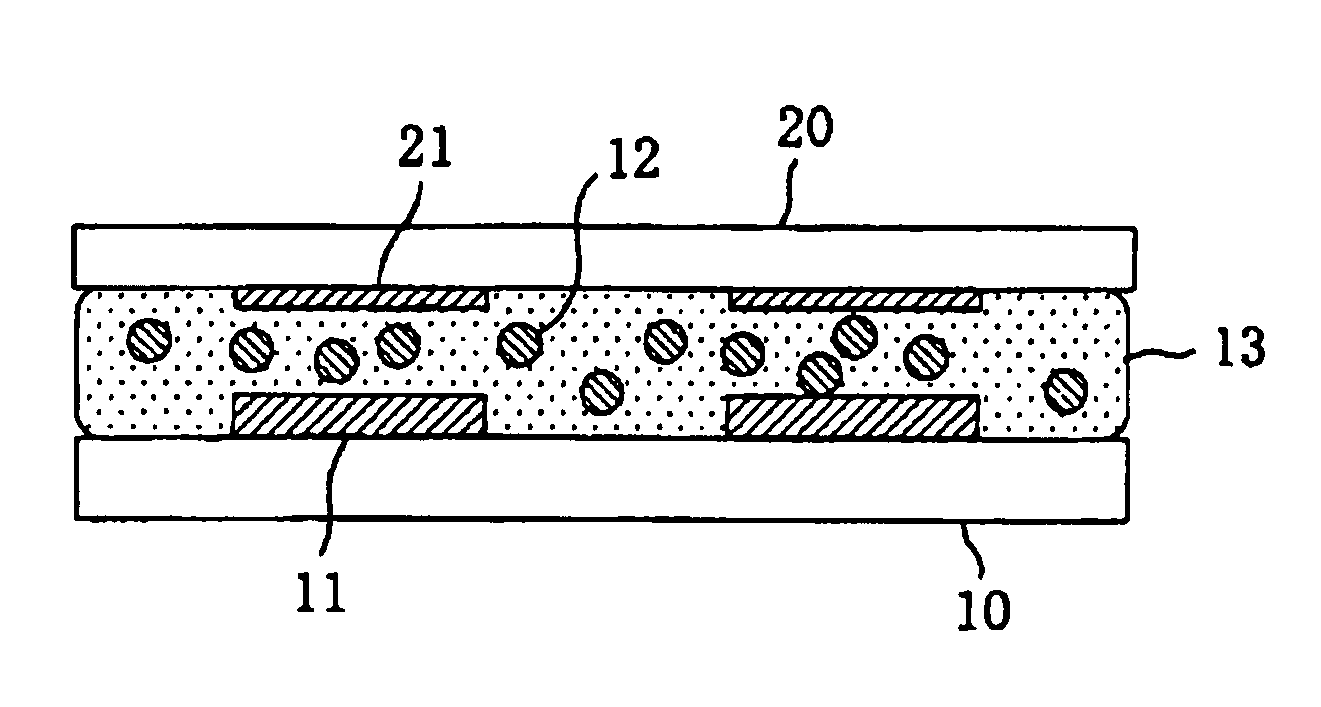

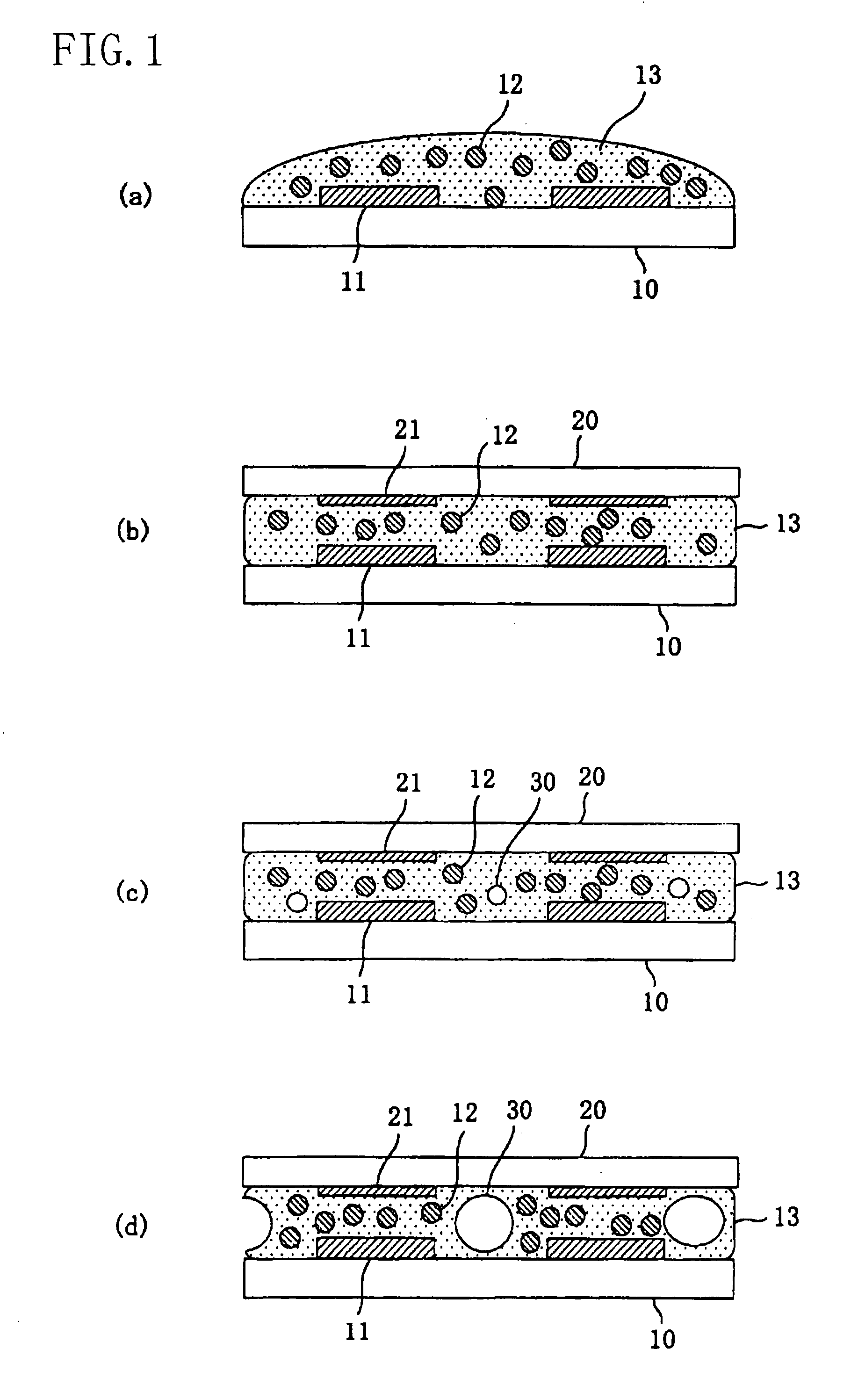

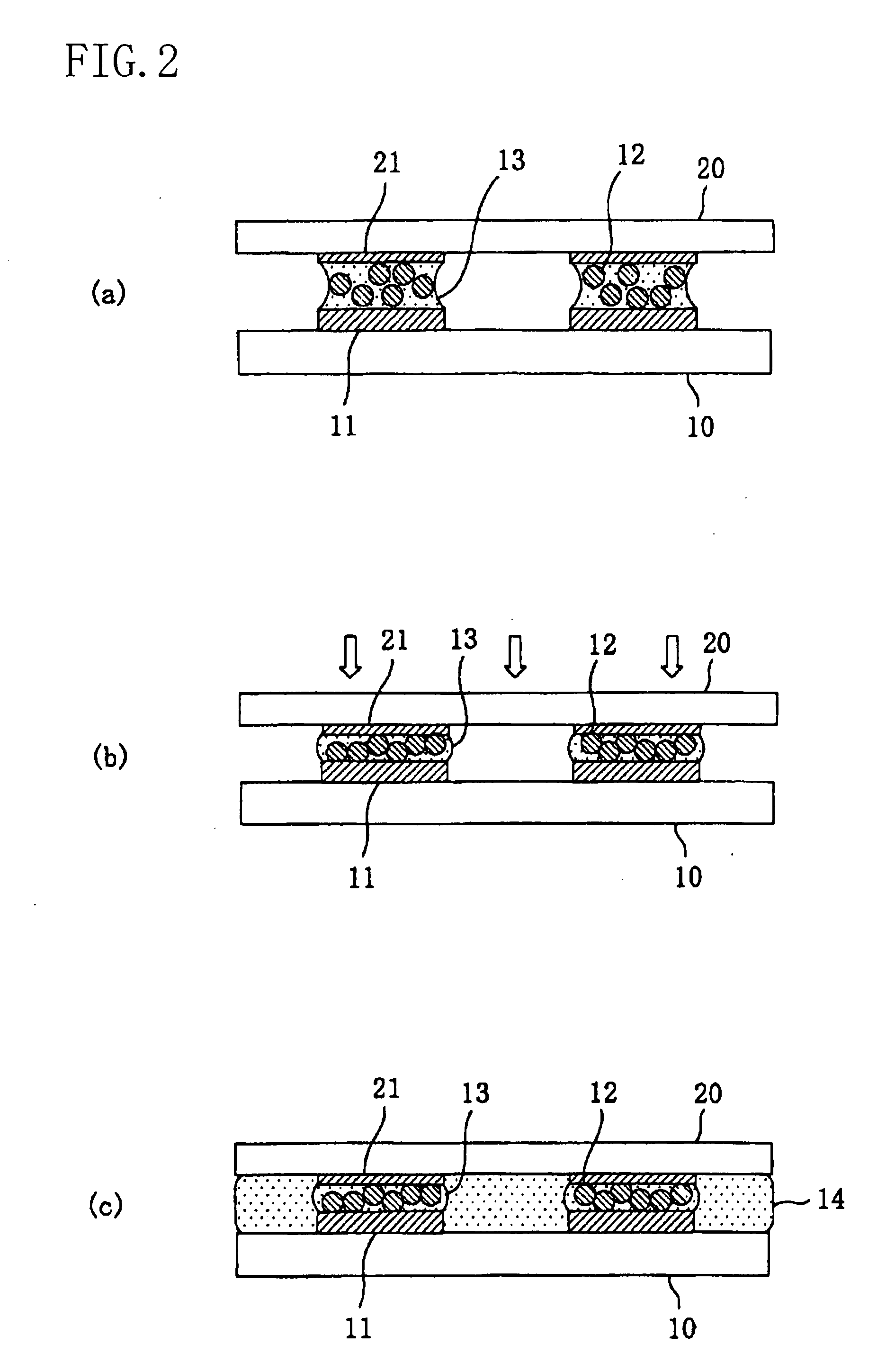

[0067]FIGS. 1(a) to 1(d) and FIGS. 2(a) to 2(c) are step-by-step cross-sectional views showing the basic steps of a flip chip mounting method in an embodiment of the present invention.

[0068]First, as shown in FIG. 1(a), a resin (e.g., an epoxy resin or the like) 13 containing conductive particles (e.g., Cu or the like) 12 and a gas bubble generating agent (e.g., isopropyl alcohol or the like) is supplied onto a circuit board 10 having a plurality of connecting terminals 11. Then, as shown in FIG. 1(b), a semiconductor chip 20 having a plurality of electrode terminals 21 is disposed on the surface of the resin 13 to face the circuit board 10. At this time, the electr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More