Semiconductor integrated circuit including a DRAM and an analog circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

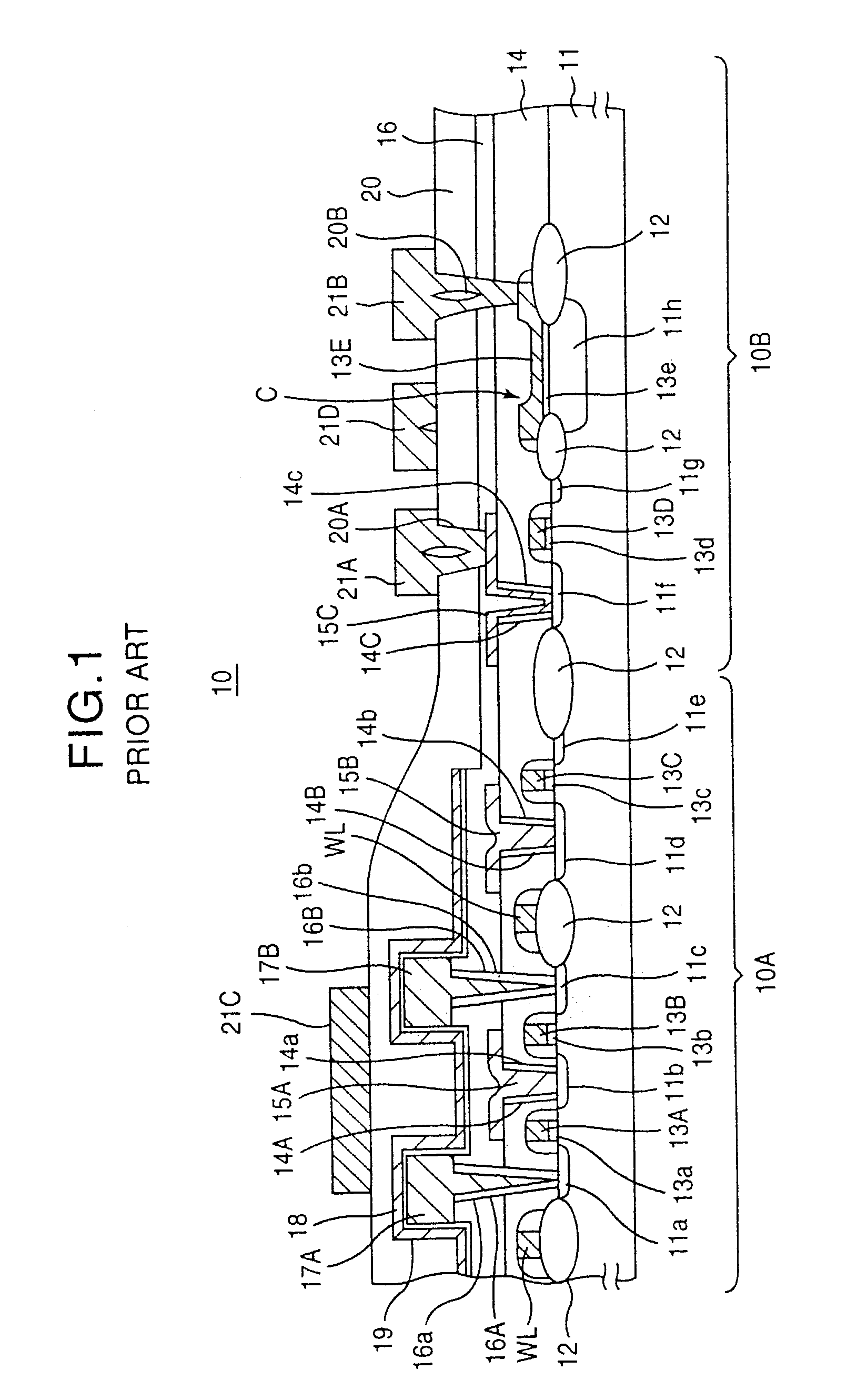

[First Embodiment]

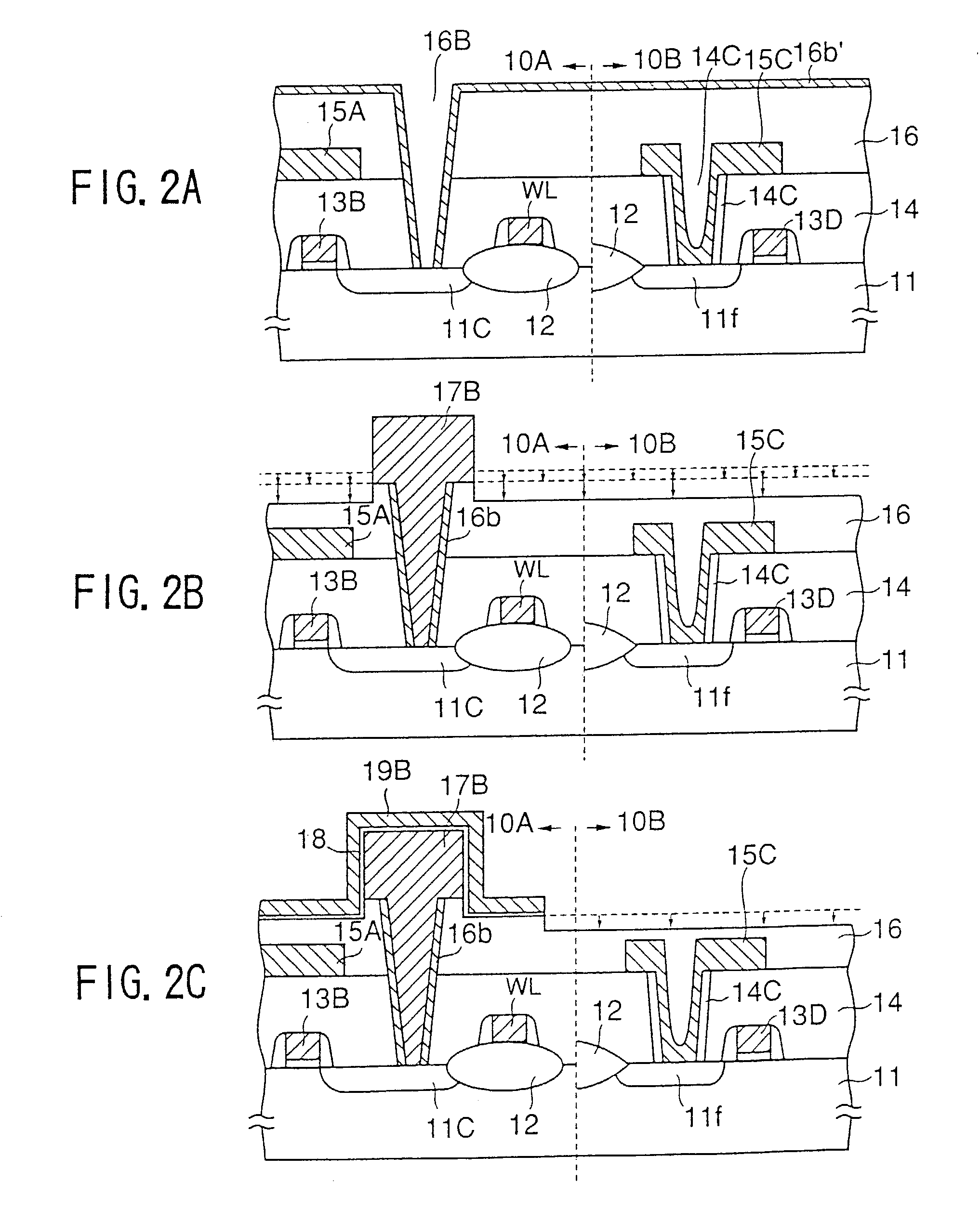

[0069]FIGS. 2A–2C show the process of forming the memory cell capacitor in the semiconductor device of FIG. 1 according to a first embodiment of the present invention, wherein those parts corresponding to the parts described previously are designated by the same reference numerals and the description thereof will be omitted.

[0070]Referring to FIG. 2A, the contact hole 16B is formed in the second interlayer insulation film 16 so as to expose the diffusion region 11c, and an insulation film 16′ is deposited on the interlayer insulation film 16 so as to cover the side wall of the contact hole 16B. Next, in the step of FIG. 2B, an anisotropic etching process acting substantially perpendicularly to the principal surface of the substrate 11 is applied on the insulation film 16′, and the side wall insulation film 16b is formed by removing the insulation film 16′ remaining on the interlayer insulation film 16.

[0071]Next, in the step of FIG. 2B, a polysilicon film is deposi...

second embodiment

[Second Embodiment]

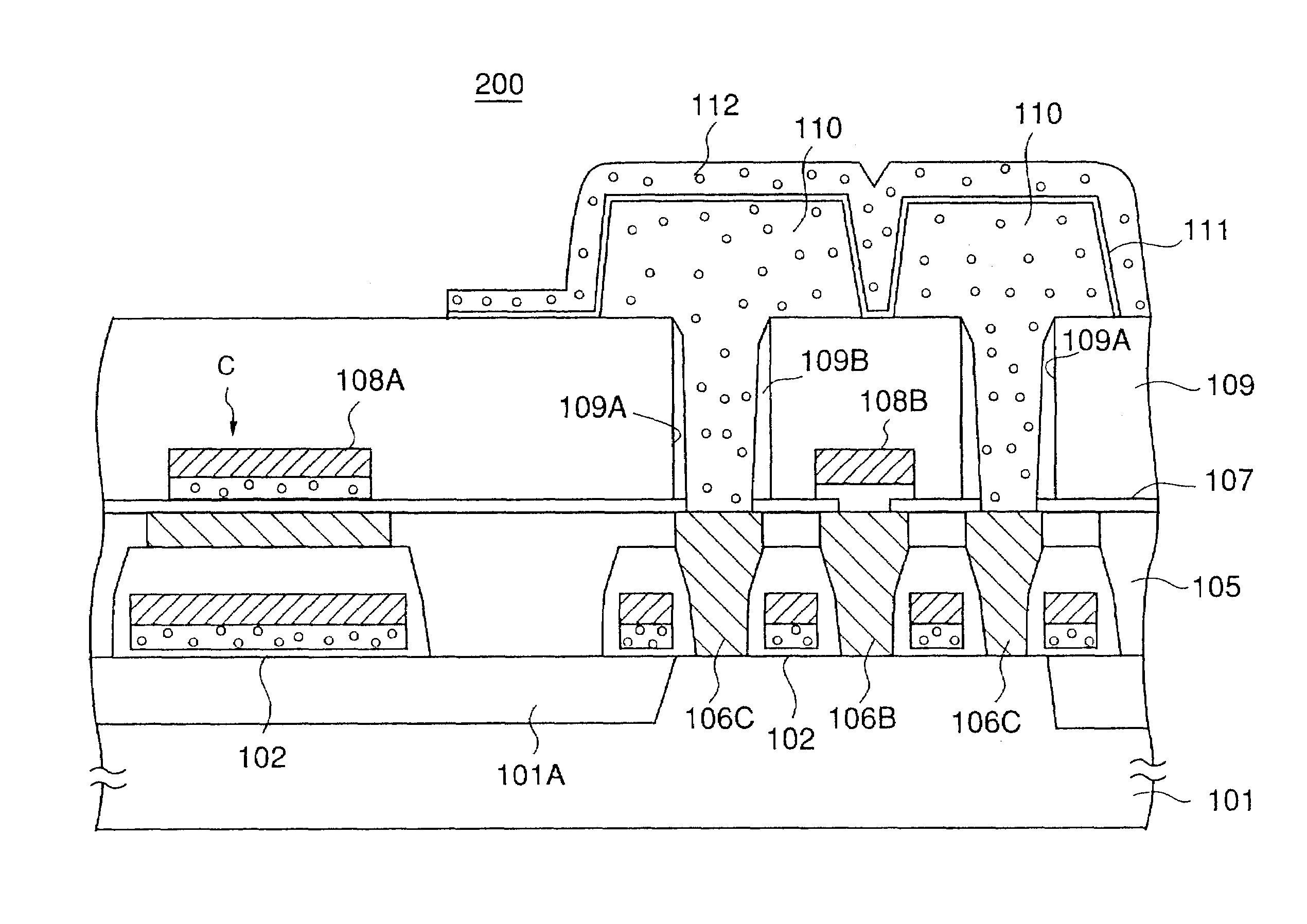

[0074]FIGS. 3A–3F show the fabrication process of a DRAM according to a second embodiment of the present invention wherein the problems of the first embodiment is eliminated.

[0075]Referring to FIG. 3A, a p-type Si substrate 31 is formed with an n-type well 31A and an initial oxide film (not shown) is formed on the substrate with a thickness of about 3 nm. Further, an SiN pattern 32 is formed thereon with a thickness of about 115 nm, such that the SiN pattern 32 defines a device isolation region.

[0076]Next, in the step of FIG. 3B, field oxide films 33A–33F are formed on the substrate 31 by a wet oxidation process with a thickness of about 320 nm while using the SiN pattern 32 as a mask. Further, a p-type well 31A is formed in the n-type well 31A in correspondence to the memory cell region 30A by conducting an ion implantation process of B+. Further, there is formed a p-type well 31C in the substrate 31 in correspondence to a peripheral region 30B formed outside the...

third embodiment

[Third Embodiment]

[0097]In the DRAM of the previous embodiment, there can be a case in which the conductor layer constituting the storage electrode 41 or the opposing electrode 43 remains unetched along the stepped part S3 between the memory cell region 30A and the peripheral region 30B as an irregular pattern 42X at the time of the patterning of the storage electrode 41 or the opposing electrode 43 as represented in FIG. 6.

[0098]FIGS. 7A and 7B show the formation of the memory cell capacitor in the memory cell region 30A in a plan view, wherein FIG. 7A corresponds to the step of FIG. 4B.

[0099]Referring to FIG. 4A, there is formed a stepped part S1 at the outer side of the memory cell region 30A represented by the broken line as a result of the patterning process conducted by the resist pattern 40, and contact holes 30A are formed in the memory cell region 30A in a row and column formation.

[0100]On the other hand, FIG. 4B corresponds to the foregoing step of FIG. 4D and shows the st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More