High performance sub-micron P-channel transistor with germanium implant

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

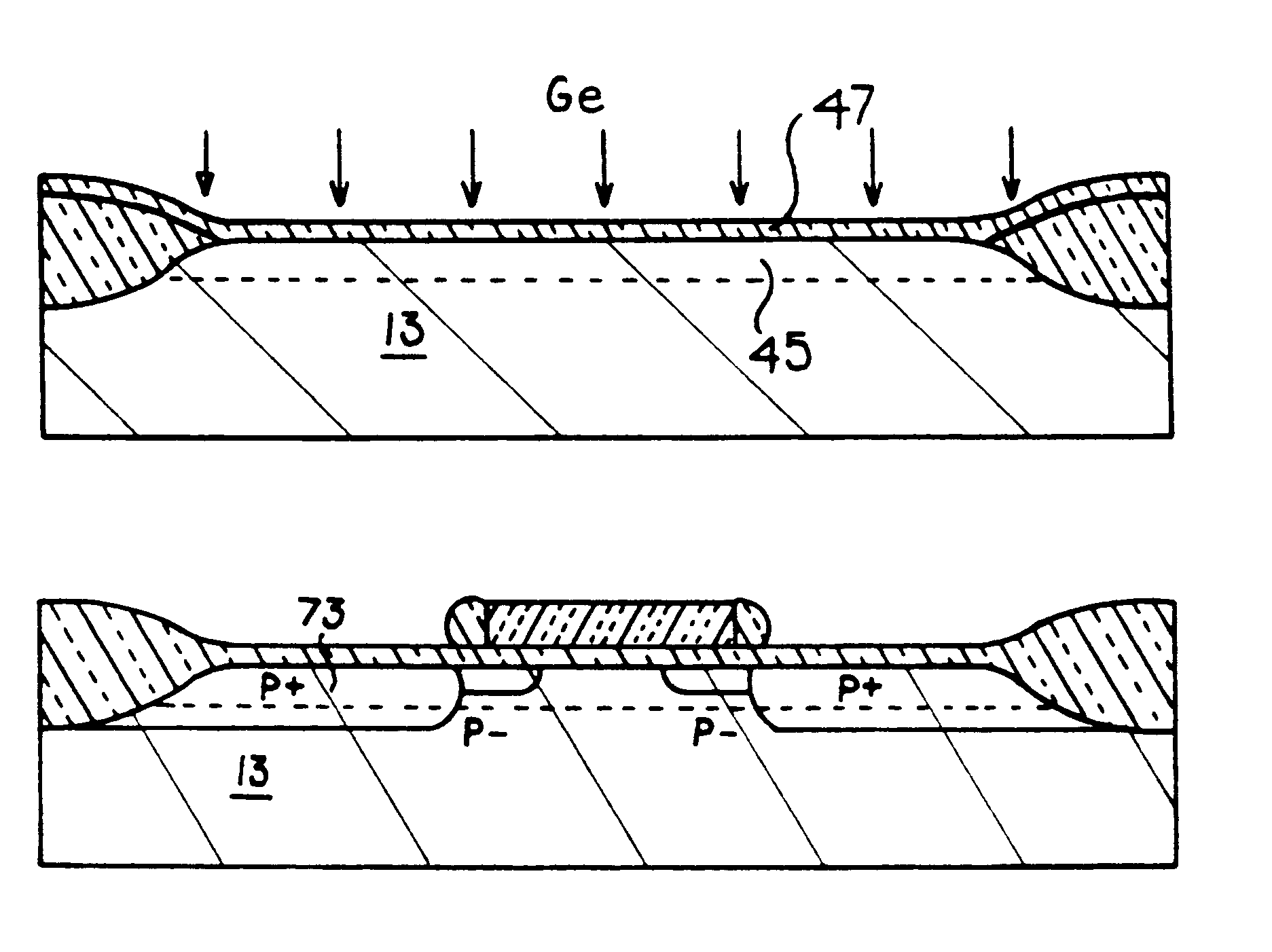

FIG. 1 shows a cross-section of a semiconductor circuit during its fabrication. A silicon wafer 13 is prepared by forming a thin film of oxide 15 and then depositing nitride 17 over the thin oxide 15. The nitride is masked and etched in order to define active area (31, FIG. 3). The unmasked portions of the wafer 13 are then implanted with boron in order to increase parasitic field transistor threshold voltage V.sub.TF.

After the field implant, a thick layer of silicon oxide 21 is grown onto the wafer 13 to form field ox, as shown in FIG. 2. The growth of silicon oxide occurs in areas which are not covered by the nitride mask 17, but tends to encroach on the active area, marked AA. The encroachment is present around the edges of the nitride 17, as indicated by dashed lines 23, where the oxide 21 begins to "buck up" or lift the nitride 17.

The nitride 17 is then stripped and the wafer 13 is oxide etched in order to remove a top portion 41 of the field ox 21, as shown in FIG. 3. This red...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More