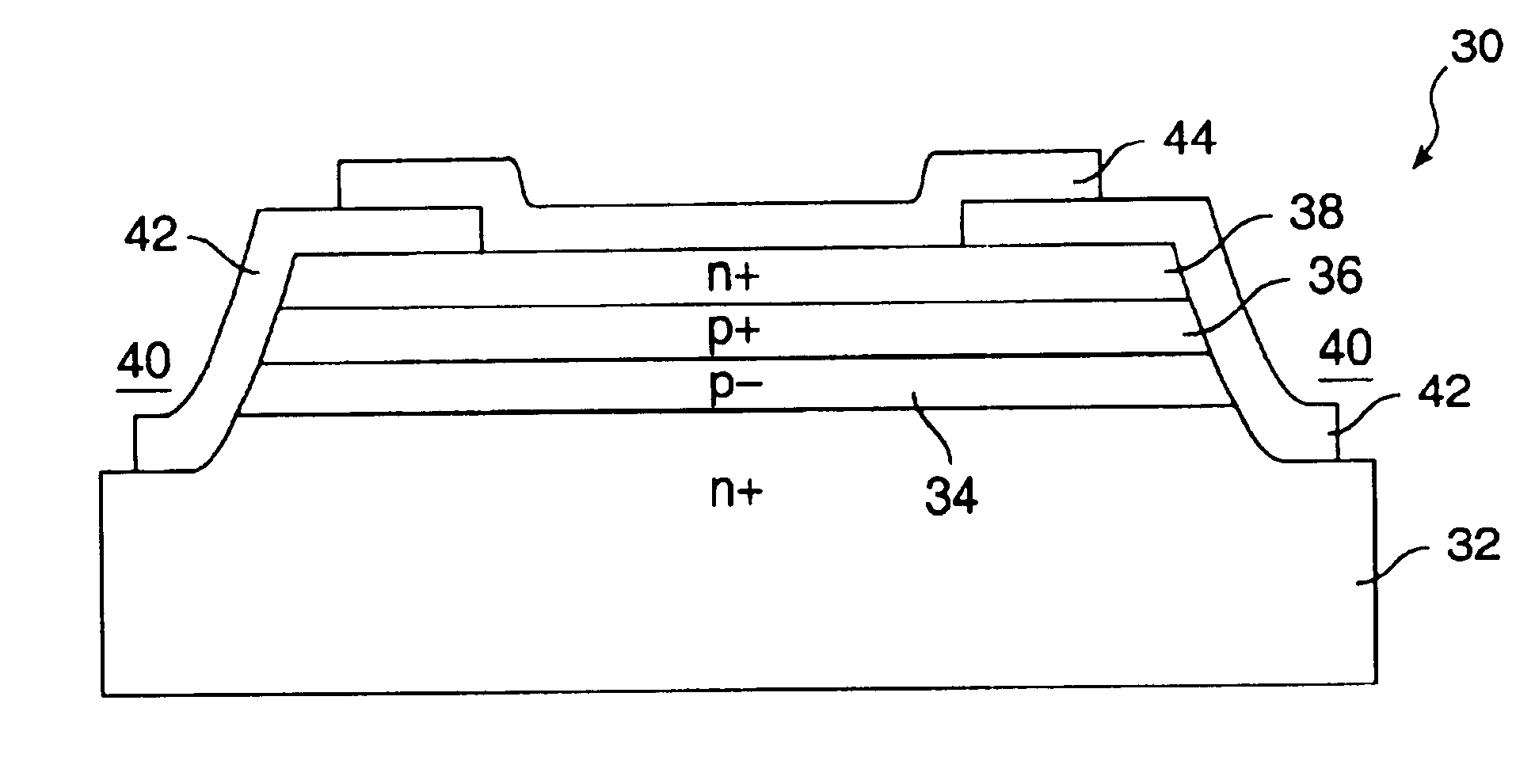

Low-voltage punch-through transient suppressor employing a dual-base structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Those of ordinary skill in the art will realize that the following description of the present invention is illustrative only and not in any way limiting. Other embodiments of the invention will readily suggest themselves to such skilled persons.

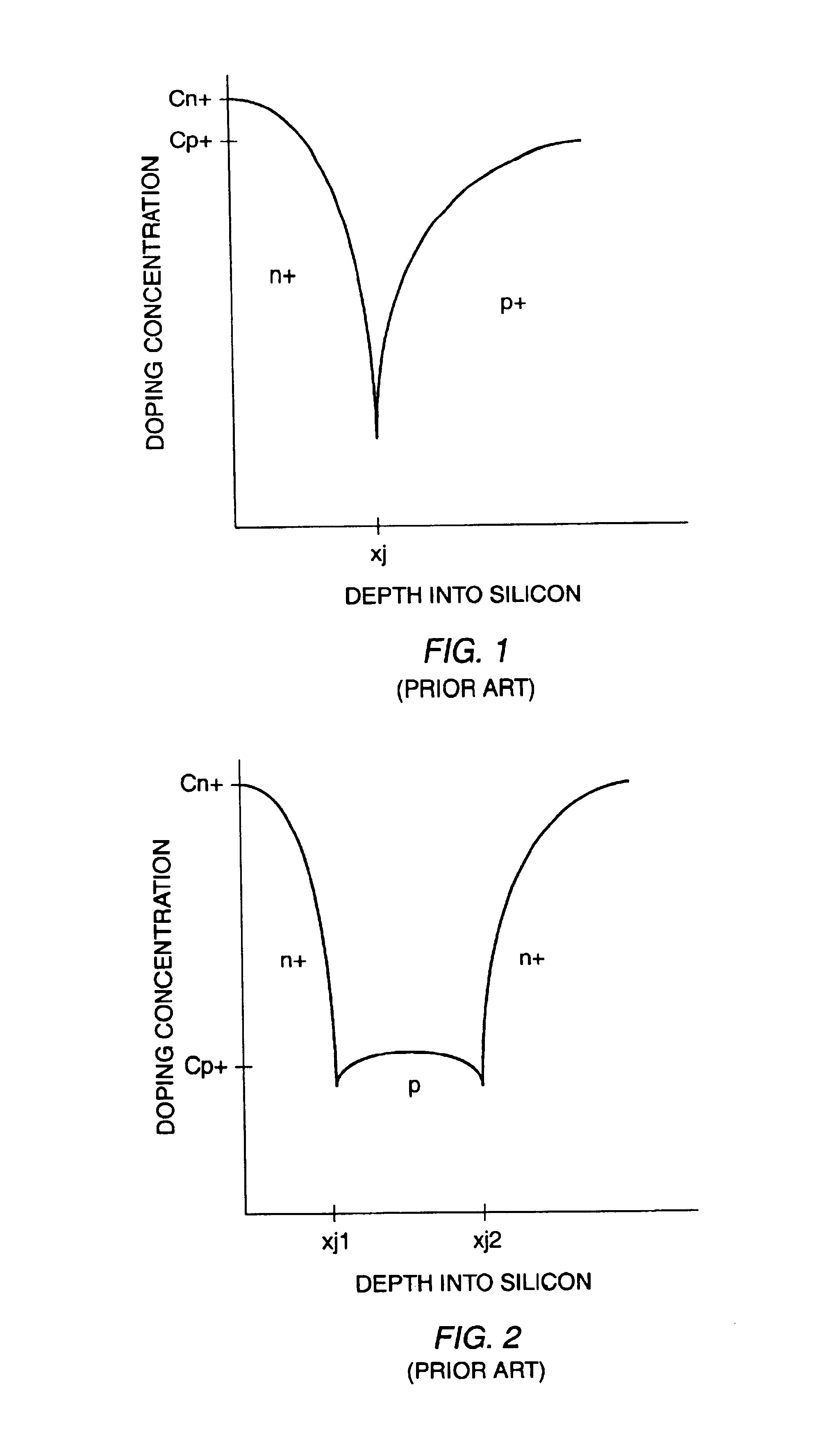

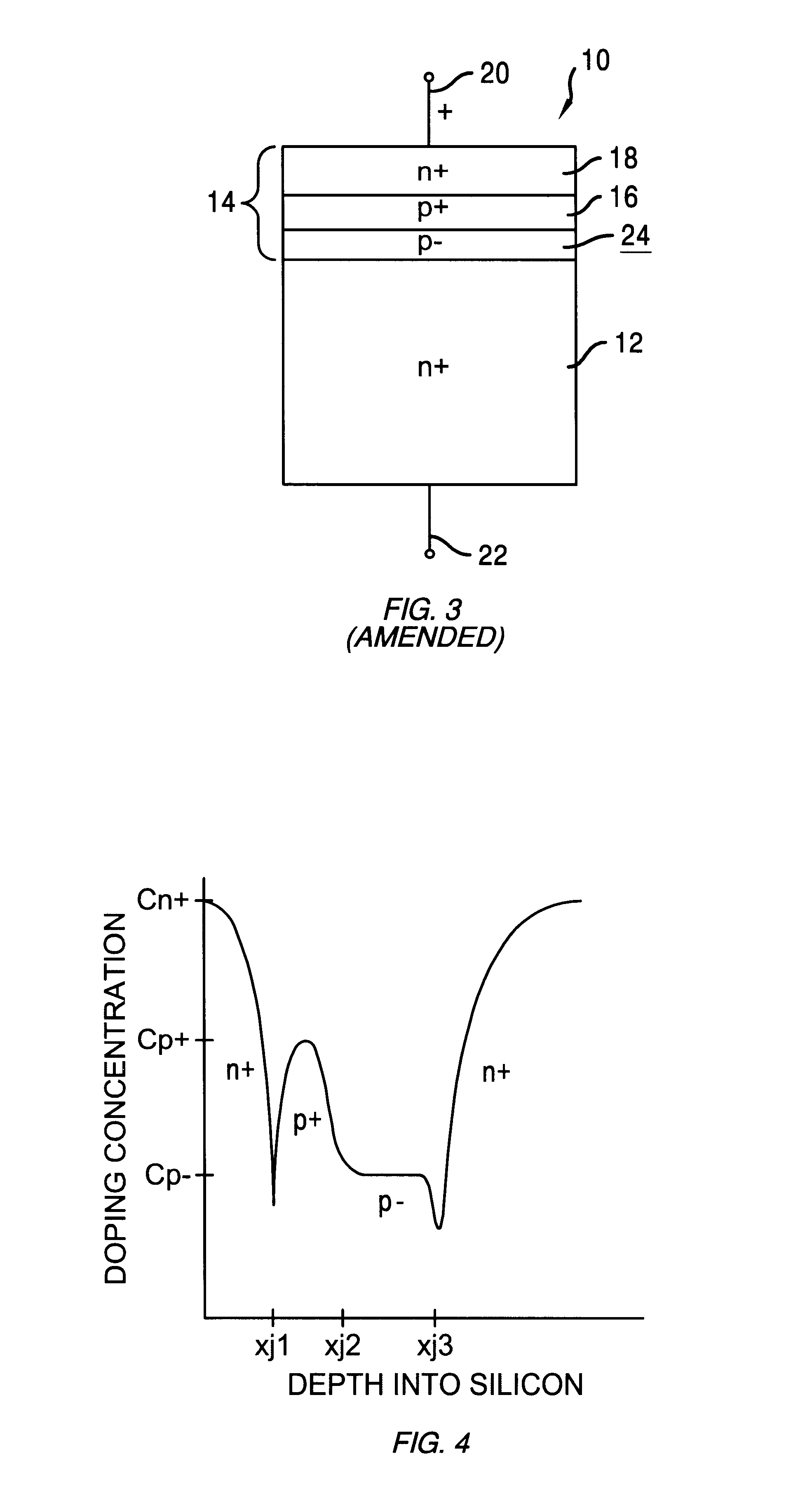

Reversed biased p+n+ zener diodes are currently the most widely-used devices for low voltage protection. These devices perform satisfactorily at voltages of 5 volts and above but exhibit very large leakage currents and high capacitance, two major drawbacks, when designed to clamp below 5 volts. FIG. 1. depicts the impurity doping profile of a typical low voltage pn junction device.

The n+p+ uniform base punch-through diode is a second device capable of clamping low voltages. While the leakage and capacitance characteristics of the punch-through diode are superior to the conventional pn diode, the punch-through diode has poor clamping characteristics at high currents. The doping profile of a low voltage n+pn+ uniform base punch-through diode is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More