Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor devices, electric solid devices, instruments, etc., can solve problems such as slow action speed, increased film resistance, difficult process combination, etc., to achieve improved reliability, miniaturization, and easy The effect formed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0153] 6 to 8 are schematic plan views showing step by step the manufacturing steps of the ferroelectric memory cell array according to Embodiment 1 of the present invention.

[0154] FIGS. 9 to 12 schematically show a partial cross-sectional structure in the manufacturing process of the above-mentioned cell array, specifically, they are cross-sectional views including the active region and the cell capacitor along the line A-A in FIG. 8 .

[0155] First, the structure of the cell array will be described. 12 shows a cross-sectional view of the completed cell array. Compared with the previous example in which the bit line is first formed and the upper electrode connection structure is compared, the connection structure between the switching transistor and the upper electrode 19 of the ferroelectric capacitor and the structure of the upper electrode 19 are different.

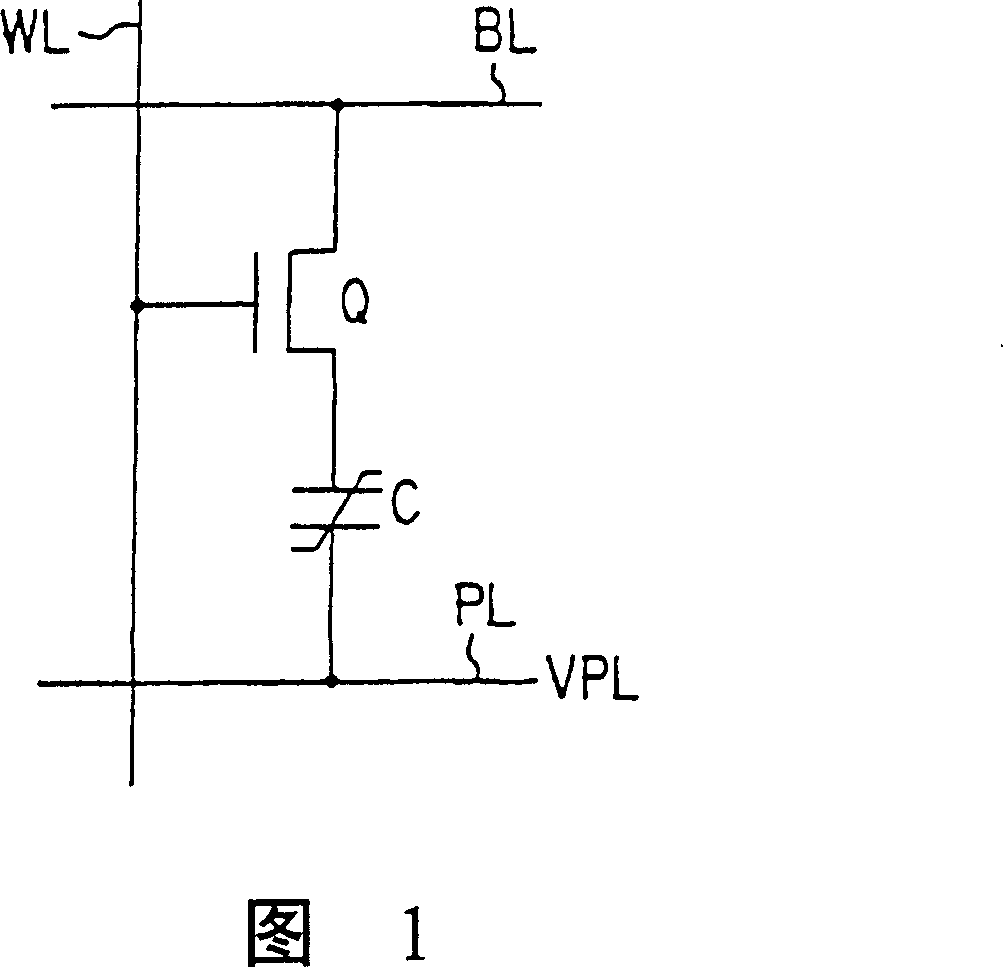

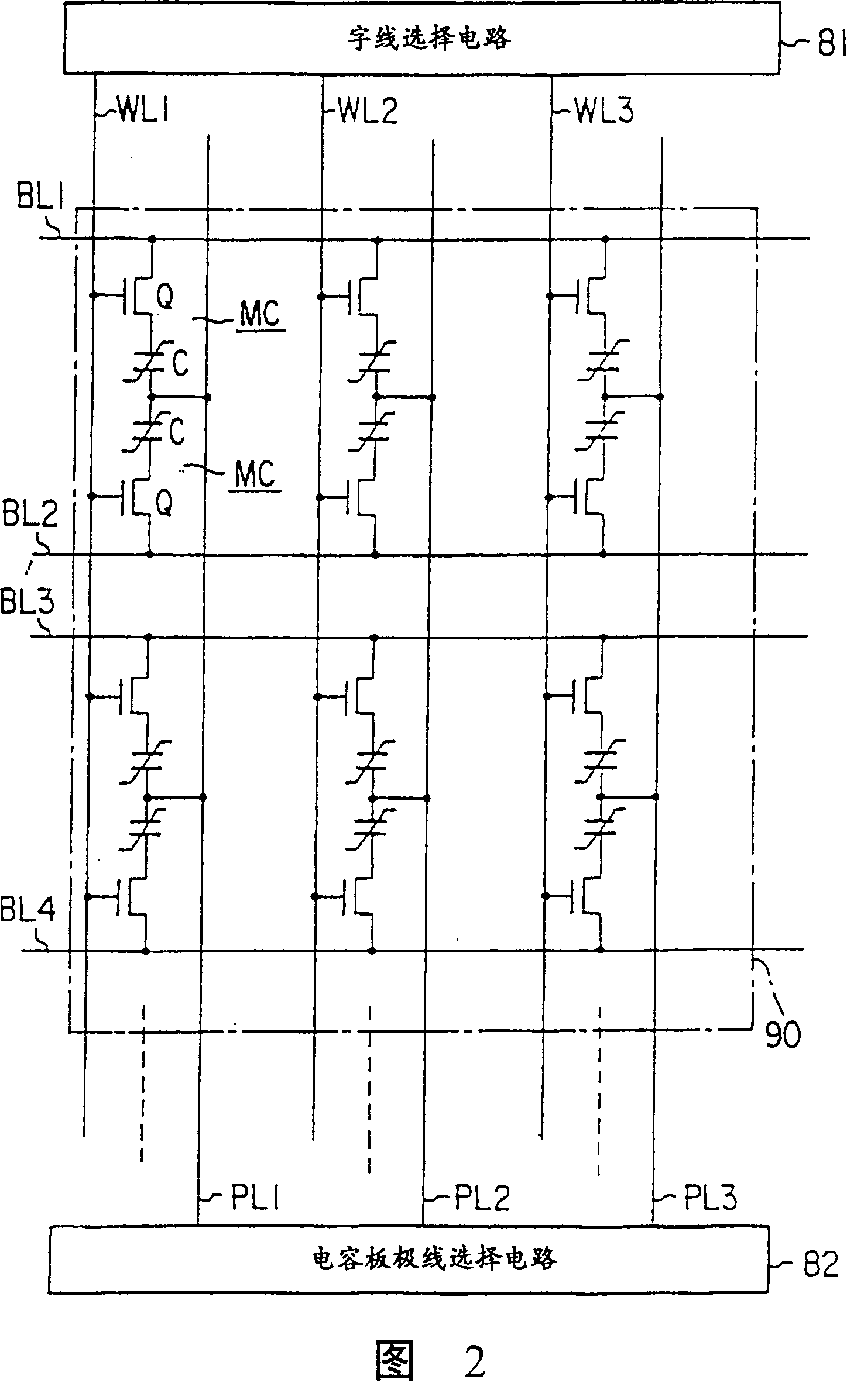

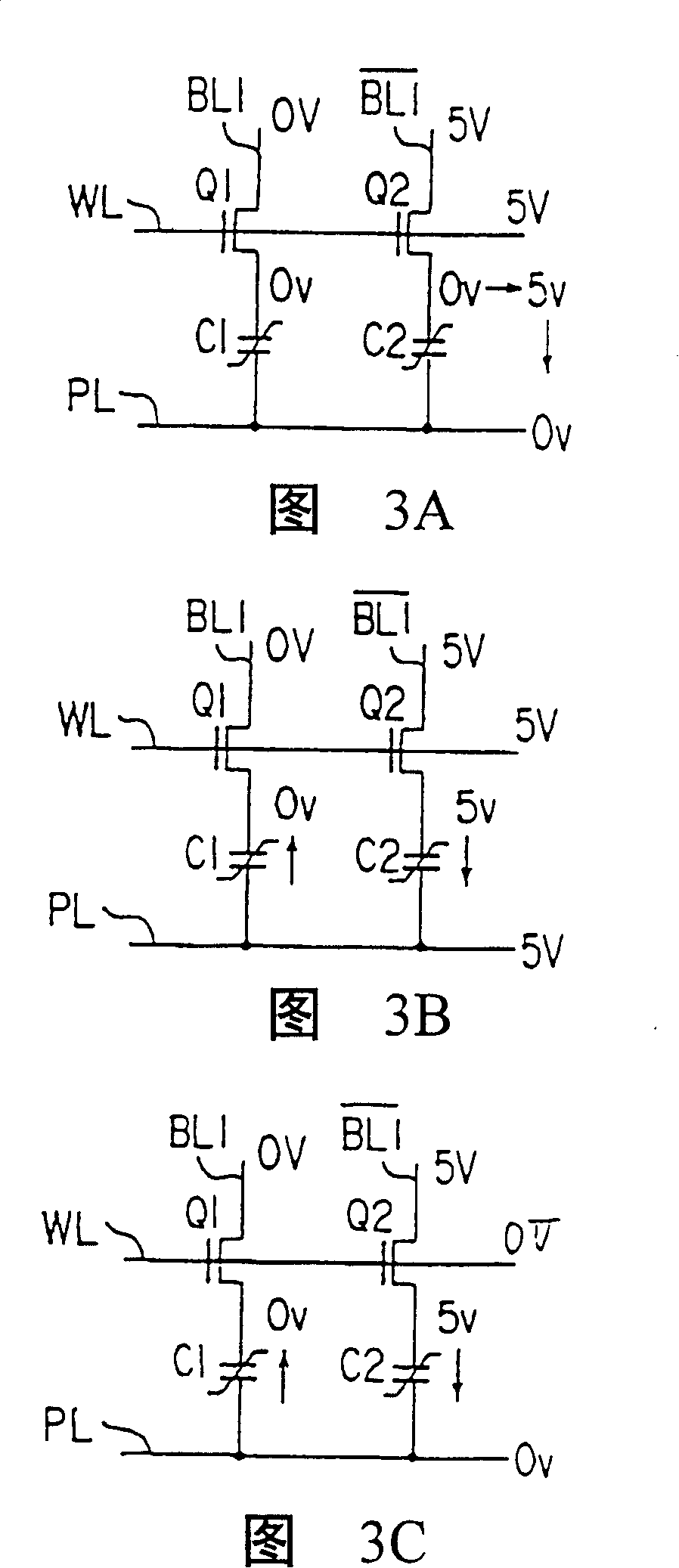

[0156] In addition, in this embodiment, an FRAM will be described as an example. This FRAM has a unit cell in w...

Embodiment 2

[0214] 16 and 17 are schematic cross-sectional views of FRAM for explaining the manufacturing method of the FRAM cell and other elements mixed therewith according to the second embodiment of the present invention in order of steps. Fig. 18 is a schematic plan view of a partial cell array of the FRAM of this embodiment. The same parts as in Embodiment 1 are assigned the same reference numerals.

[0215] The manufacturing method of this embodiment is characterized in that in order to connect the second-layer wiring (bit line or other wiring) and the first-layer wiring in the two-layer wiring structure, at least Al, AlCu, AlCuSi, WSi 2 , Cu, a material (aluminum in this case) is reflowed, and the vias are buried.

[0216] In FIGS. 16 and 17 , a MOS transistor 31 for switching a memory cell and another MOS transistor 32 for a device other than the memory cell are formed on the semiconductor substrate 1 .

[0217] In the first insulating layer 10 that covers the above-mentioned t...

Embodiment 3

[0249] 19 is a schematic cross-sectional view of an FRAM showing a partial cross-sectional structure of a FRAM cell (including an SDG region and a cell capacitor) according to Embodiment 3 of the present invention.

[0250] The FRAM cell structure shown in FIG. 19 is basically the same as the aforementioned FRAM cell structure in FIG. 2 The film 51 forms a ferroelectric capacitor, and forms the second SiO2 on the ferroelectric capacitor. 2 Membrane 52 is different in this respect.

[0251] The FRAM cell manufacturing process shown in FIG. 19 is different from the aforementioned manufacturing process with reference to FIGS. 1st SiO 2 The process of film 51, (2) after forming the ferroelectric capacitor, add the second SiO2 of about 100nm by sputtering 2 The process of film 52, (3) in the 2nd SiO 2 The second interlayer insulating film 13 is deposited on the film 52, and when it selectively opens holes, the second SiO2 layer in the lower layer 2 Film 52 or 2nd SiO 2 Film 5...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com