Multilayer interconnection substrate, semiconductor device, and solder resist

A multi-layer interconnection, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as damage, large, damaged joints, etc. The effect of reducing inductance and elastic modulus

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

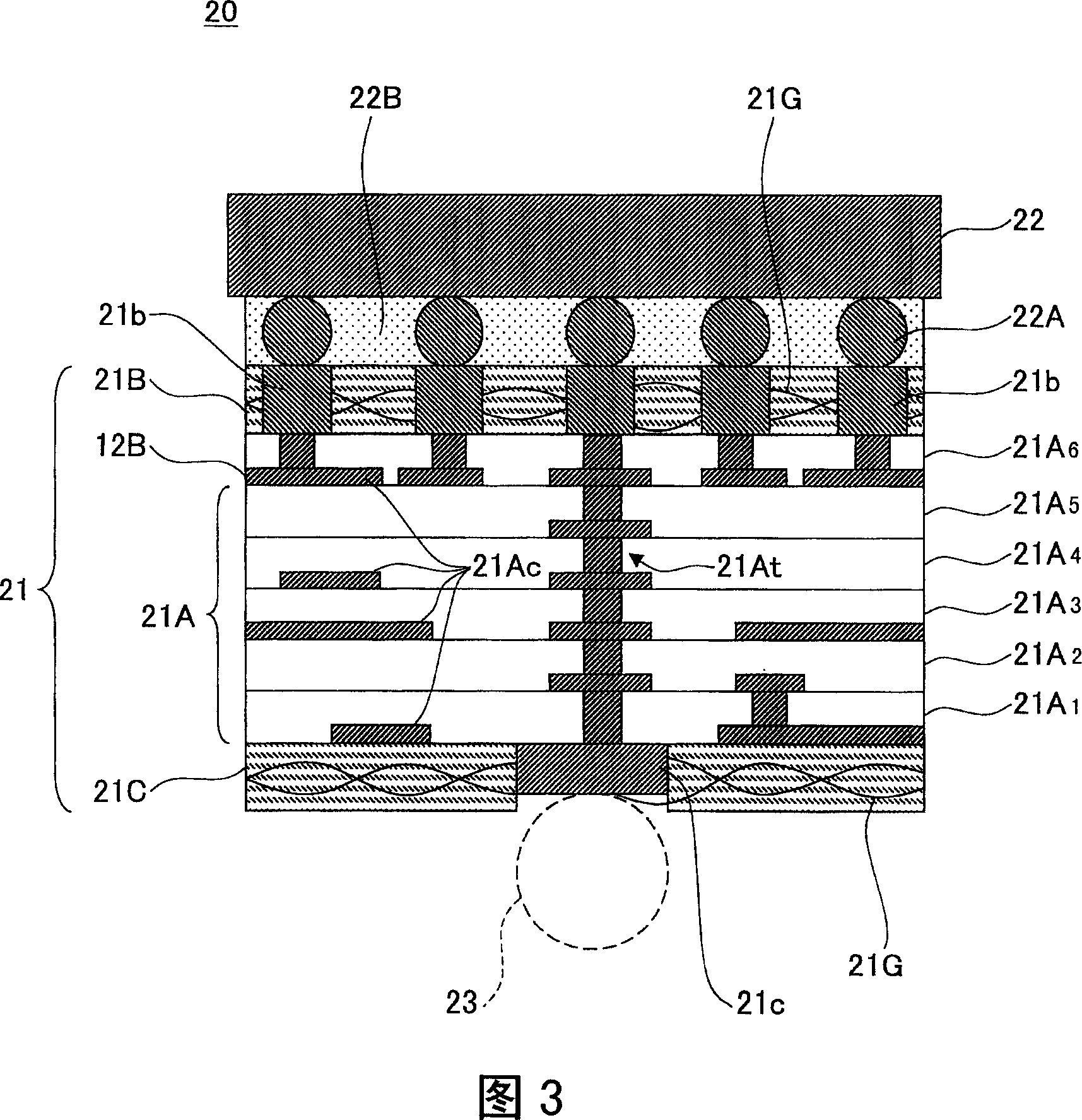

[0045] FIG. 3 shows the configuration of a semiconductor device 20 according to the first embodiment of the present invention.

[0046] 3, the semiconductor device 20 is formed by a resin multilayer interconnection substrate 21 and a semiconductor chip 22 flip-chip mounted on the resin multilayer interconnection substrate 21 through solder bumps 22A, wherein the resin multilayer interconnection substrate 21 is formed. The connecting substrate 21 includes a resin build-up layer 21A, and a plurality of build-up layers 21A are stacked in the resin build-up layer 21A. 1 -21A 6 , and solder resist layers 21B and 21C are respectively formed on the top surface and the bottom surface of the resin build-up layer 21A. The built-in layer 21A 1 -21A 6 Cu interconnection pattern 21Ac is formed on each layer of each layer. The Cu interconnection pattern 21Ac is, for example, a via pattern with a diameter of 40 μm and a line-and-space pattern of 30 μm / 30 μm in line width and line spacing....

PUM

| Property | Measurement | Unit |

|---|---|---|

| elastic modulus | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More