Forming method for metal silicide blocking area and method for producing semiconductor device

A technology of metal silicide and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as poor adhesion of deep ultraviolet photoresist

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

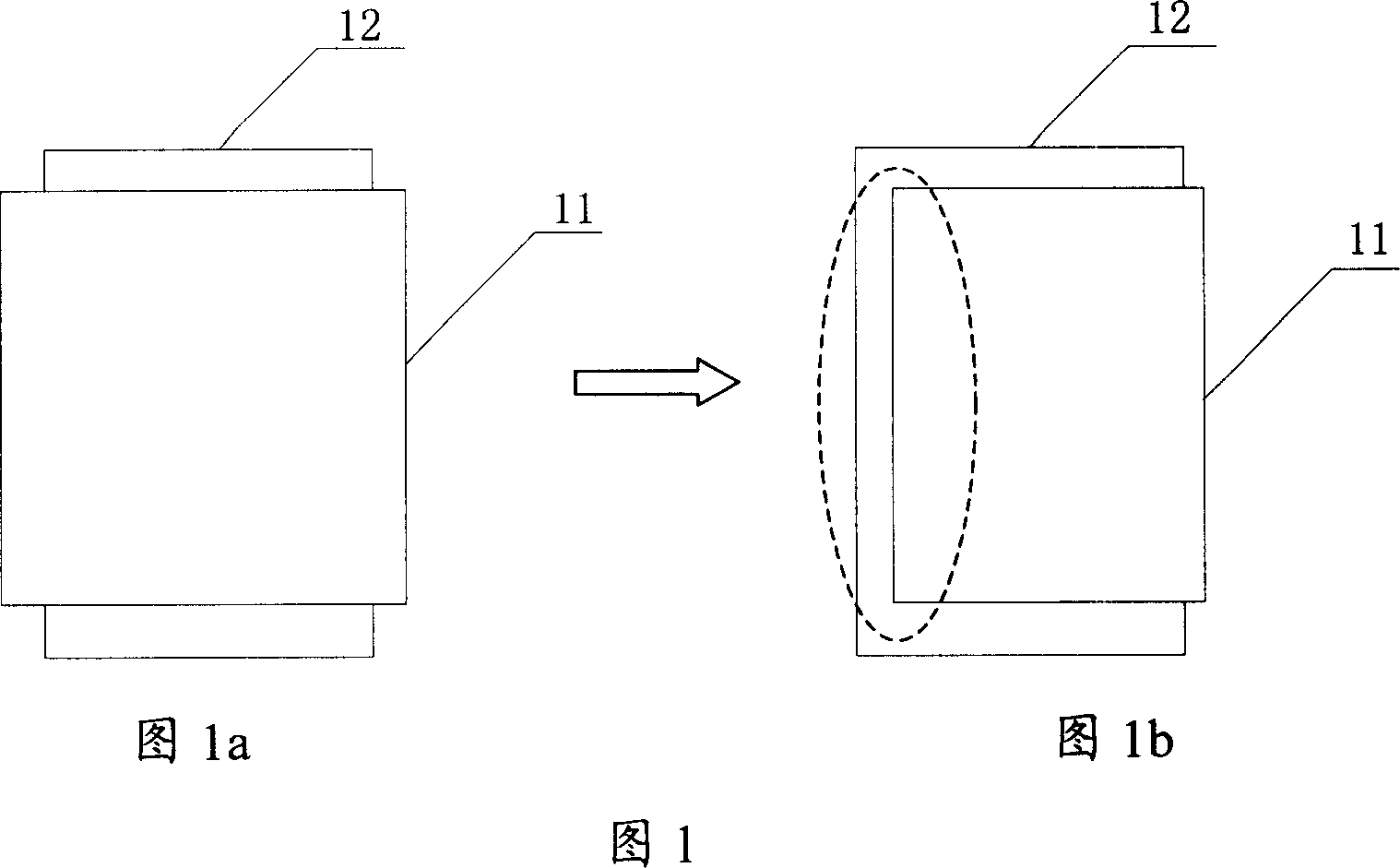

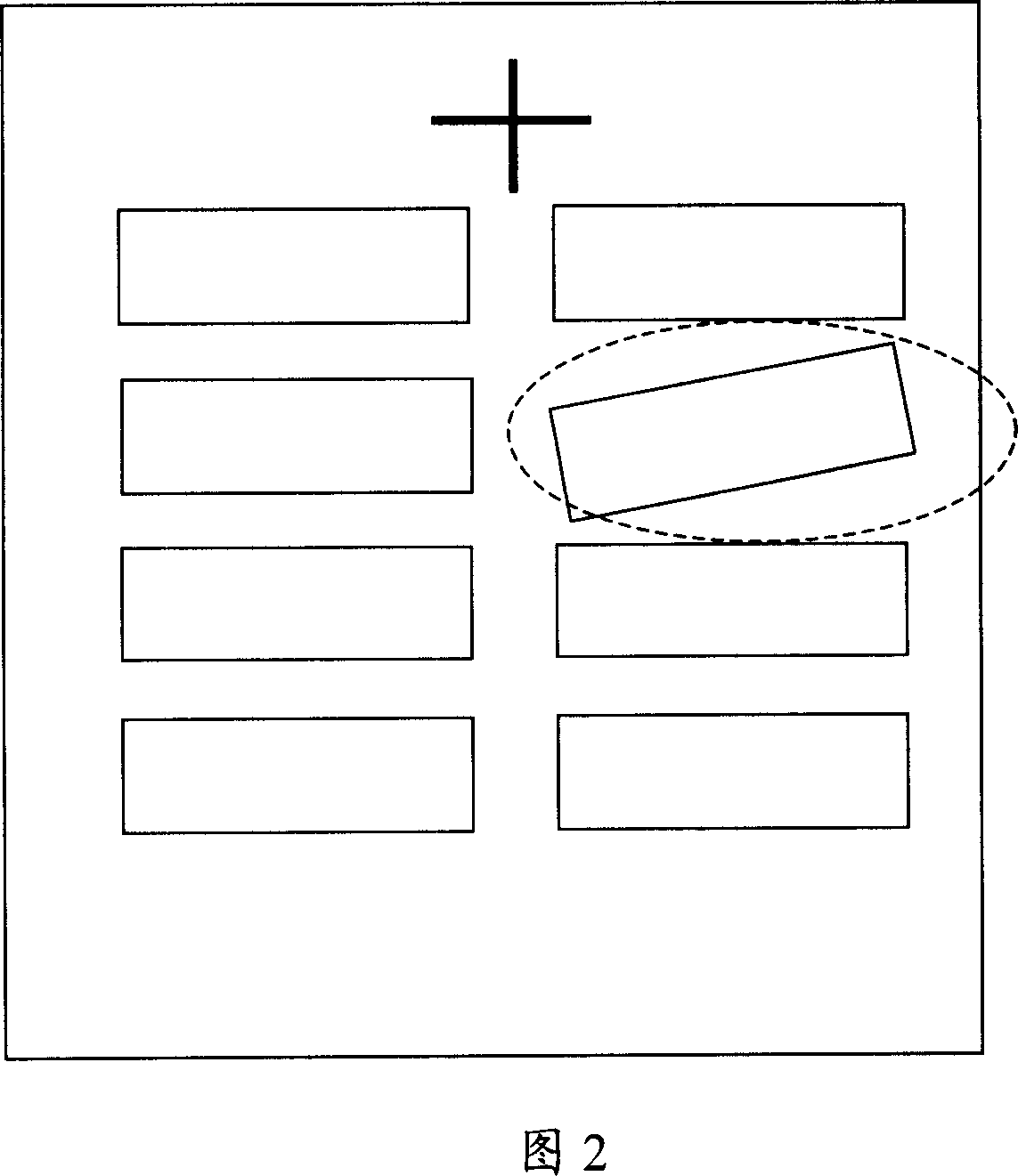

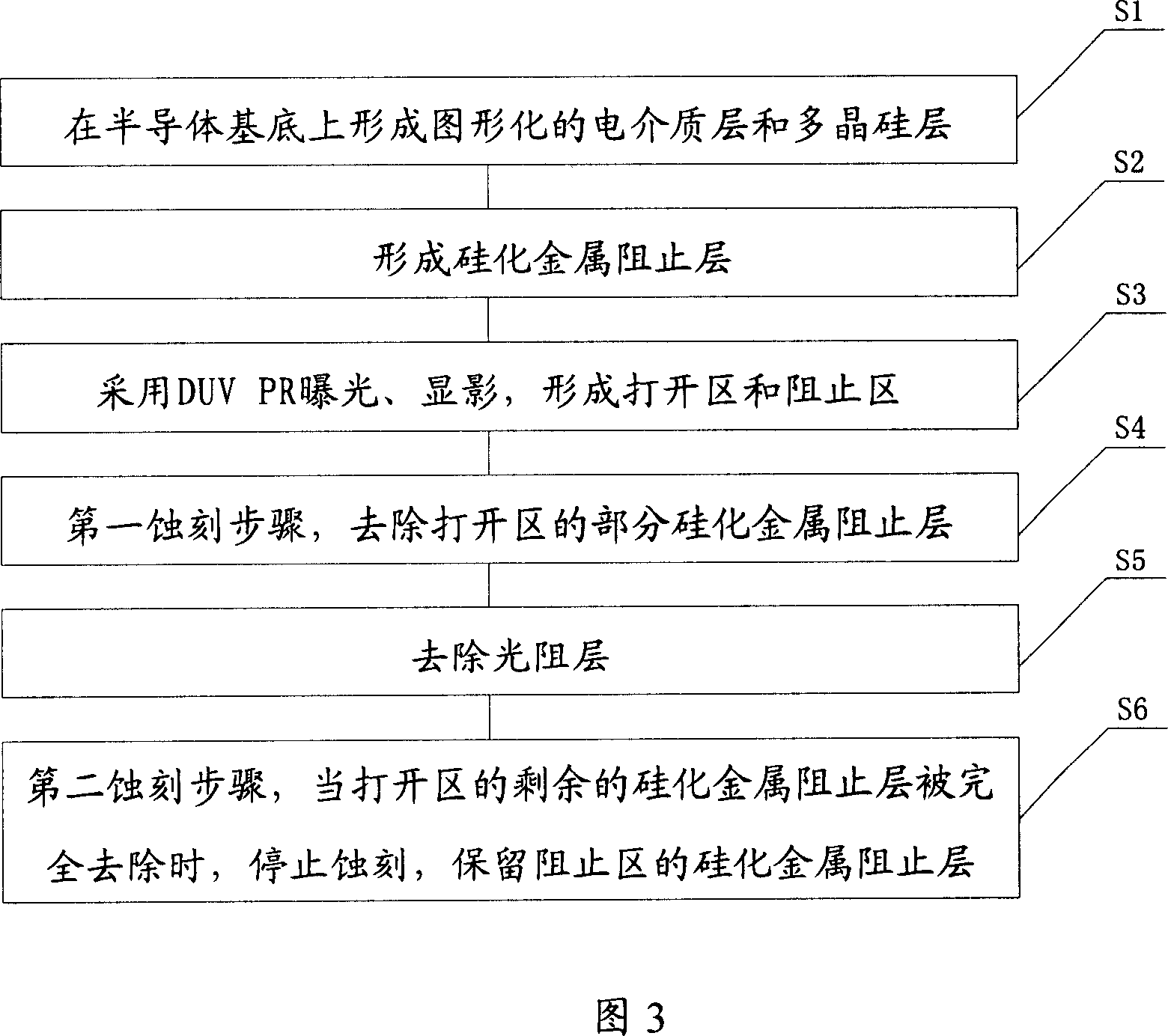

[0045] The core idea of the present invention is: in the process of forming the metal silicide prevention region, the order of the process is improved, and the deep ultraviolet photoresist is removed (strip) before the wet etching process; and by adjusting the thickness of the metal silicide prevention layer, It is ensured that the metal silicide preventing layer in the opening region can be completely removed, and the metal silicide preventing layer in the preventing region can be kept with sufficient thickness. In this way, the fineness of lines required by the 0.16 / 0.18 μm process is met, and the phenomenon of peeling and offset of the photoresist layer does not occur.

[0046] Referring to FIG. 3 , it shows a flow chart of steps for forming a metal silicide prevention region by using the method of the present invention. Referring to FIG. 4 , it shows a schematic cross-sectional view of the steps of the embodiment shown in FIG. 3 , and FIG. 4 includes FIGS. 4a-4d.

[004...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com