Flash- and rom-memory

A memory cell, RM2 technology, used in flash and read-only (ROM) memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

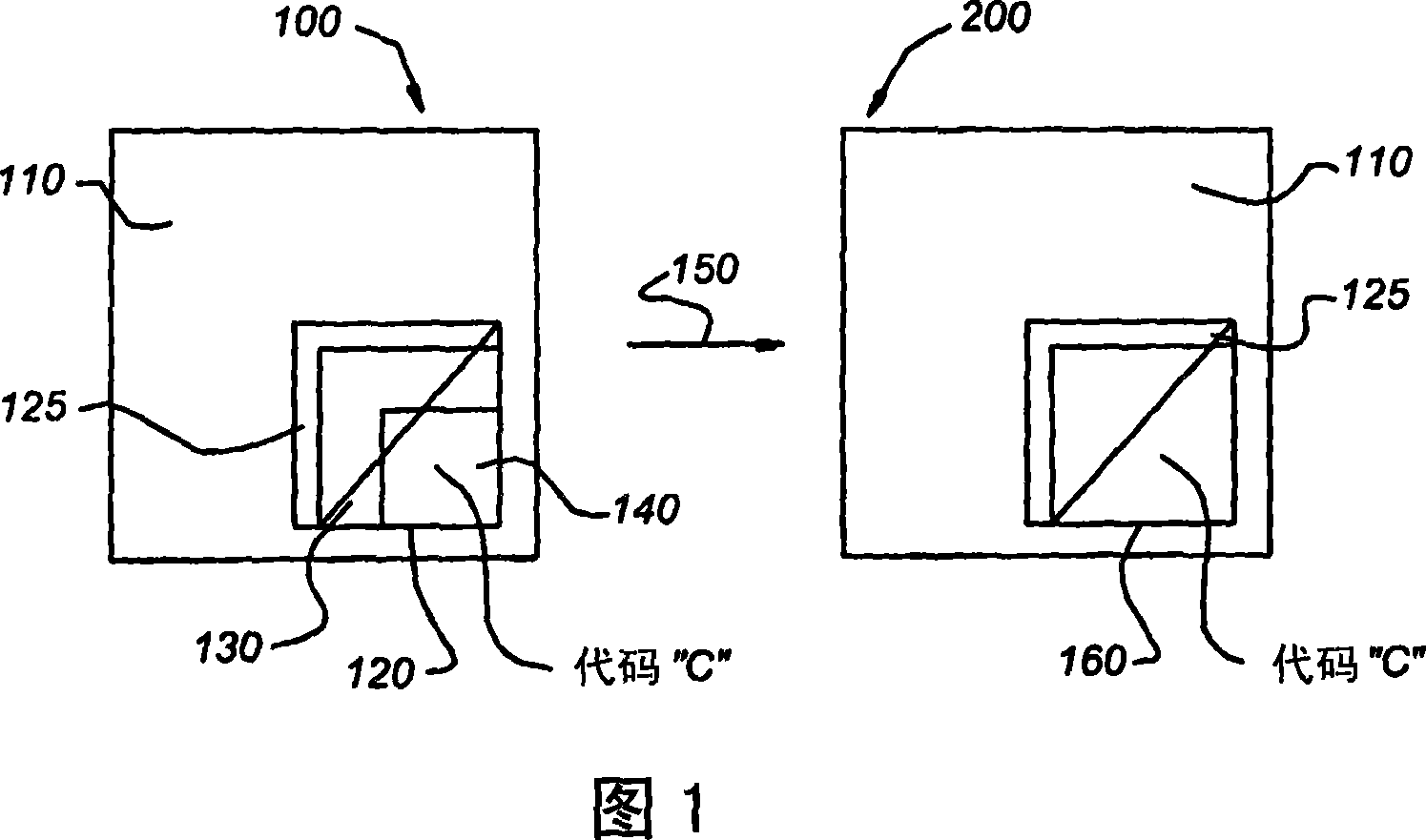

[0054] Figure 1 schematically shows the Flash-ROM conversion of an SOC device.

[0055] The first SOC device 100 includes a device portion 110 produced by baseline technology. Embedded in the device portion 110 is a Flash portion 120 . Symbolically, the wiring scheme between device portion 110 and Flash portion 120 is represented by region 125 . The flash memory part 120 includes a peripheral circuit 130 and a flash memory part 140 . The peripheral circuit 130 is connected to the wiring scheme 125 of the device part 110 at one end and connected to the flash memory part 140 at the other end. The flash memory part 140 includes a plurality of flash memory cells, and the flash memory part 140 is configured to store program code C in the plurality of flash memory cells. The program code C refers to a program that provides functions to the SOC device 100 during operation of the SOC device 100 .

[0056] The peripheral circuit 130 includes a high voltage driving circuit configure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More