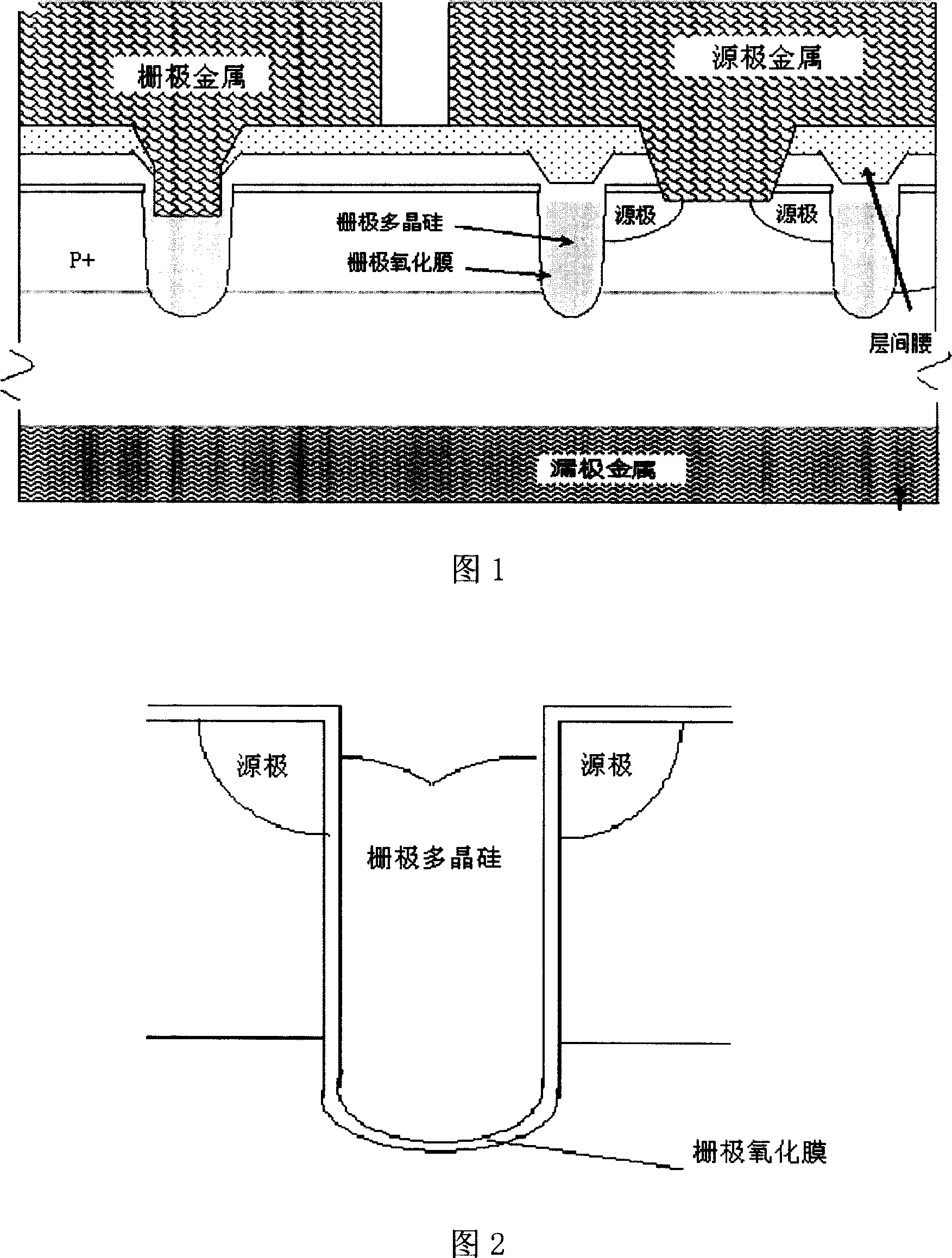

Method for manufacturing groove type MOS transistor

A technology of a MOS transistor and a manufacturing method, which is applied to the manufacturing field of trench MOS transistors, can solve problems such as an increase in turn-on voltage and on-resistance, an increase in the overall power consumption of the transistor, a large capacitance, etc., so as to reduce the capacitance and improve the switching rate. , the effect of increasing the thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

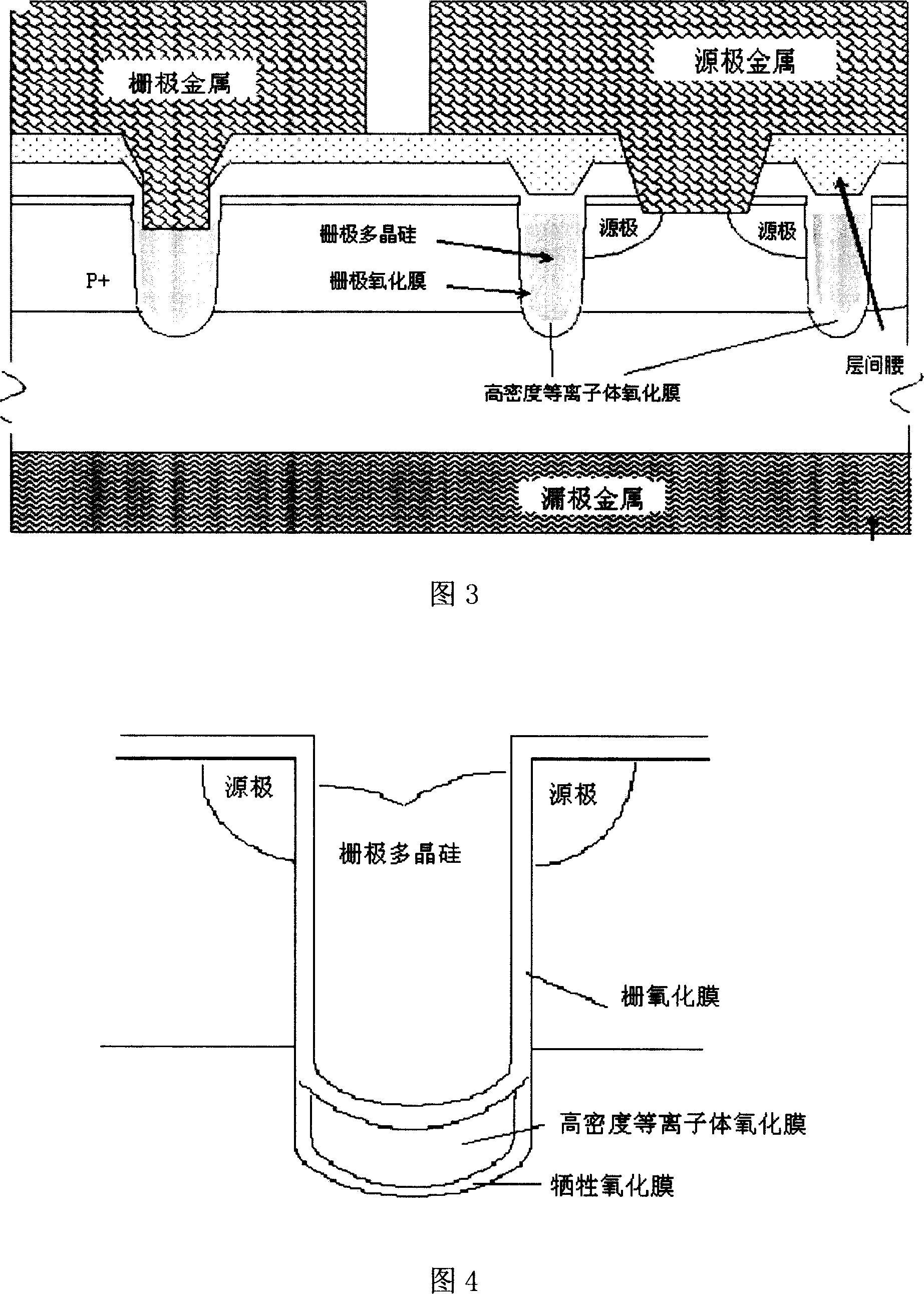

[0019] The method of the present invention comprises the following steps:

[0020] (1) Forming deep trenches by dry etching;

[0021] (2) On the bottom and sidewalls of the trench, a layer of sacrificial oxide film is grown, the thickness of the sacrificial oxide film is about 300-500 angstroms;

[0022] (3) At the bottom and sidewall of the trench, that is, on the sacrificial oxide film grown in step (2), use high-density plasma deposition (HDP) to grow a layer with a thickness of 1000-3000 angstroms High-density plasma oxide film;

[0023] (4) using a chemical solution, such as hydrofluoric acid, to remove the oxide film grown on the sidewall of the trench, the removed oxide film includes a sacrificial oxide film and a high-density plasma oxide film;

[0024] (5) at the position of the sidewall and the bottom of the trench, further grow a layer of gate oxide film;

[0025] (6) Growth and etching back of gate polysilicon in the trench;

[0026] Following the conventional ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com