Wafer press welding and bonding method and structure thereof

A bonding structure and wafer technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problem of wafers being easily broken, and achieve the effects of being beneficial to handling, increasing redundancy, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

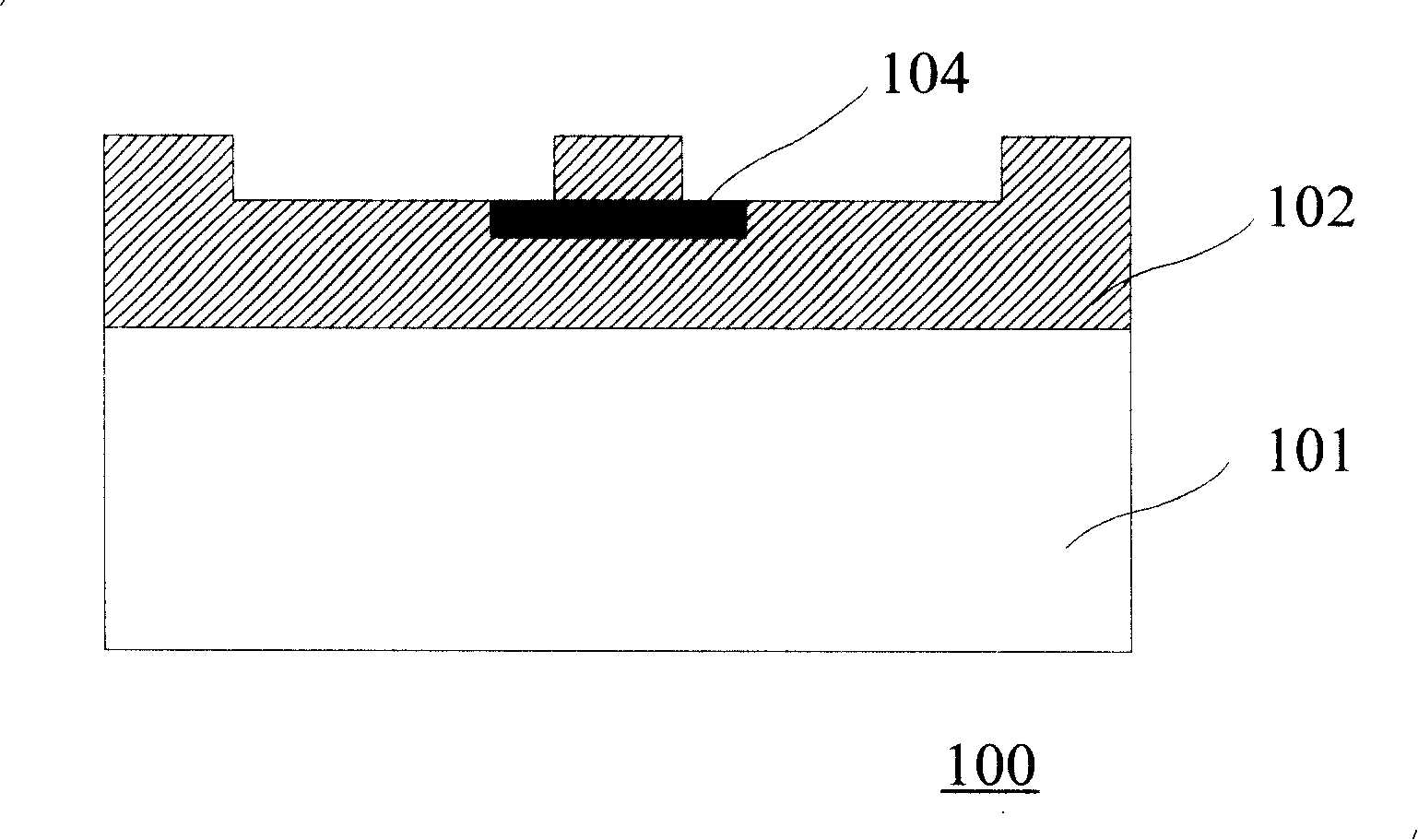

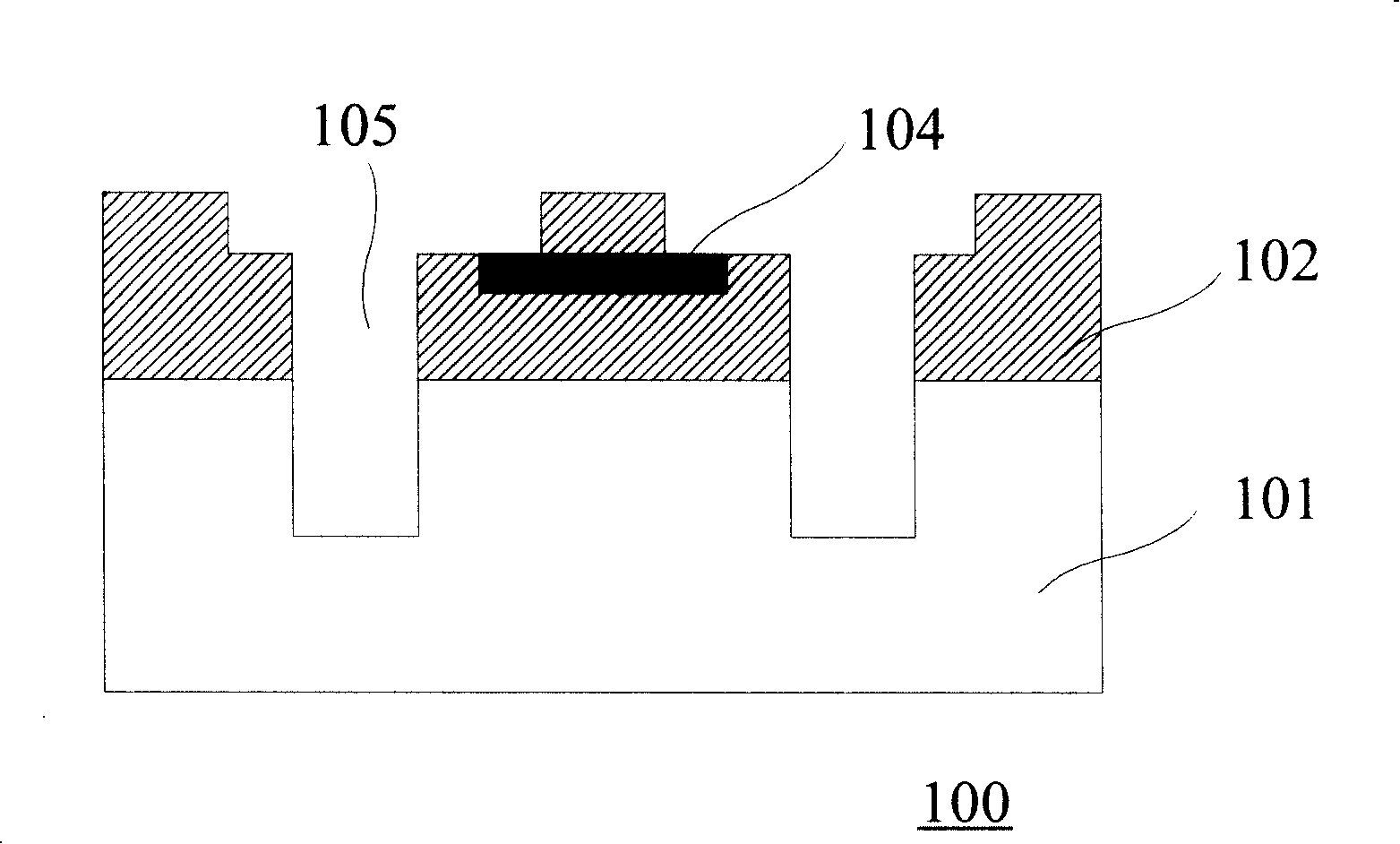

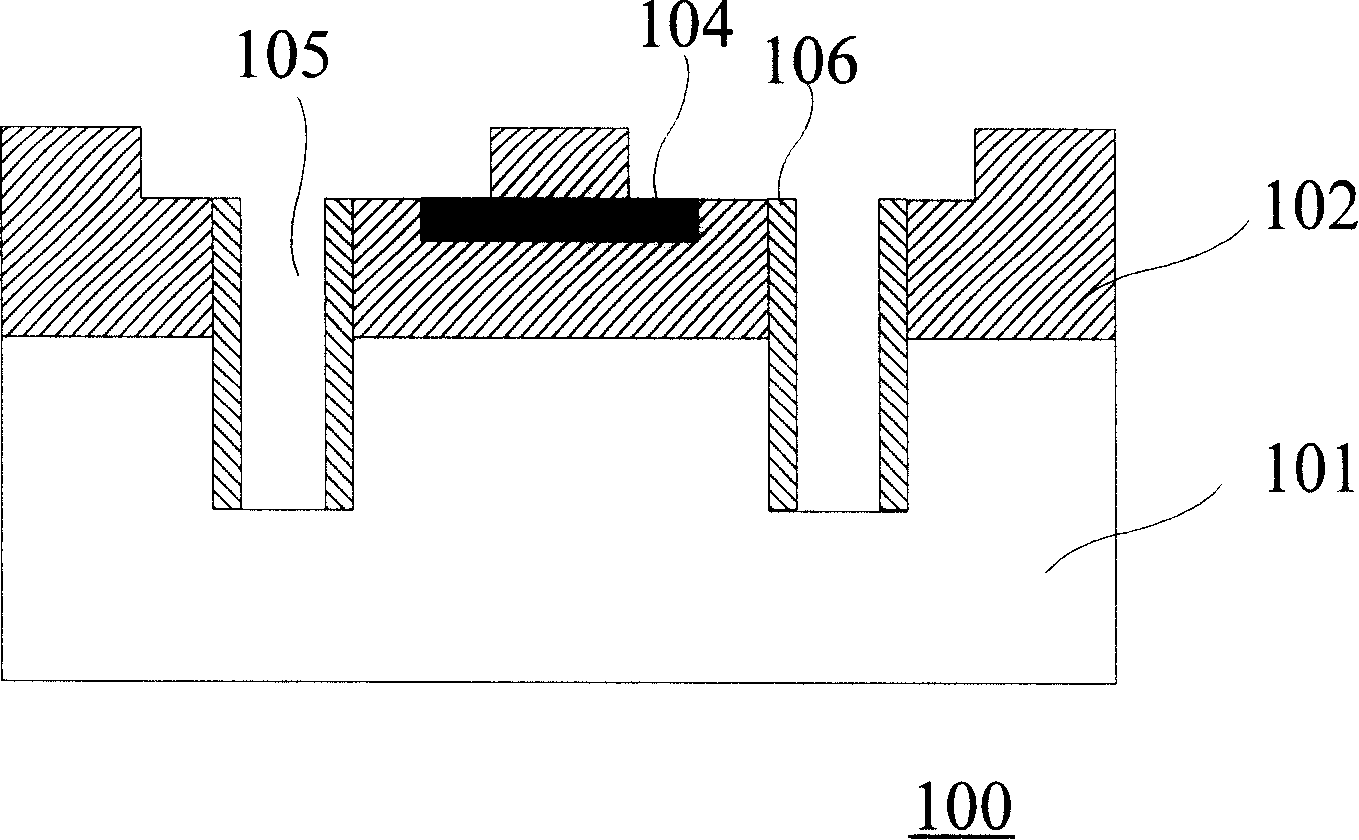

[0047] Figure 11 It is a flow chart of the wafer pressure bonding method of the present invention. Such as Figure 11 As shown, firstly, a first semiconductor wafer and a second semiconductor wafer are provided, the first semiconductor wafer and the second semiconductor wafer have completed chip manufacturing, and a passivation layer has been formed on the semiconductor wafer. The passivation layer is used to protect semiconductor chips and interconnection structures on the wafer from external moisture, scratches, and contamination. A first connection hole and a first groove are formed in the passivation layer of the first semiconductor wafer and the second semiconductor wafer by photolithography and etching process, and the bottom ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com