Method and system for delayed processing active electric power filter

A power filter and delay processing technology, which is applied in active power filter, harmonic reduction device, AC network to reduce harmonic/ripple, etc., can solve the problem of affecting the compensation accuracy and delay effect of active power filter Problems such as loss of compensation effect are not considered, and it is easy to realize full digitalization, ensure stability and dynamic response speed, and eliminate sampling delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

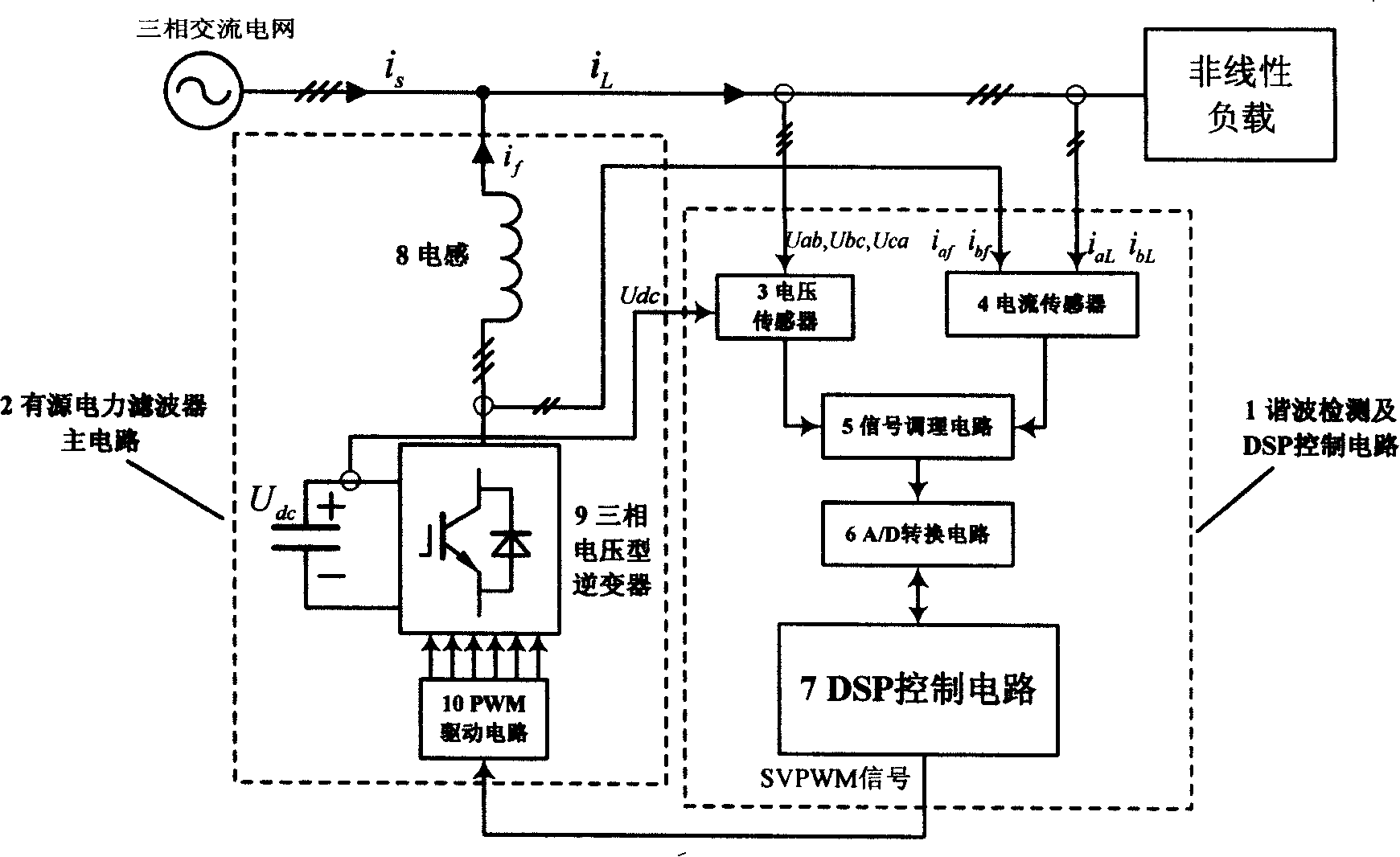

[0026] figure 1 It is the active power filter of the present invention. It is composed of a harmonic detection and DSP control circuit 1 and an active power filter main circuit 2. Harmonic detection and DSP control circuit 1 includes voltage sensor 3, current sensor 4, signal conditioning circuit 5, A / D conversion circuit 6 and DSP control circuit 7; active power filter main circuit 2 includes inductor 8, three-phase voltage type Inverter 9 and PWM drive circuit 10.

[0027] The voltage sensor 3 detects the grid voltage signal u in real time ab , u bc , u ca and the DC voltage u across the DC bus capacitor of the three-phase voltage inverter 9 dc , sent to the signal conditioning circuit 5; the current sensor 4 detects the nonlinear load current i in real time aL , i bL and active power filter output current i af , i bf , is also sent to the signal conditioning circuit 5; the signal conditioning circuit 5 is used to filter out the output signal u of the voltage sensor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More