Semiconductor device has conductive projection and its manufacturing method

A conductive bump and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the cracking and delamination of the metal layer at the bottom of the solder bump, and the ineffectiveness of the metal layer at the bottom of the solder bump. Absorb copper pillar stress and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

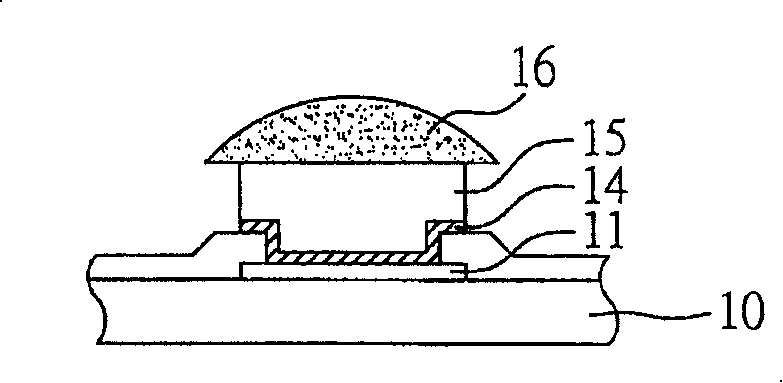

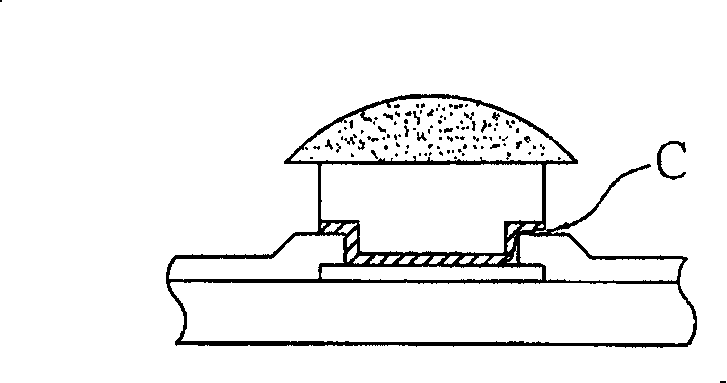

[0077] see Figure 2A to Figure 2F , is a schematic cross-sectional view showing the first embodiment of the semiconductor device with conductive bumps and its manufacturing method of the present invention.

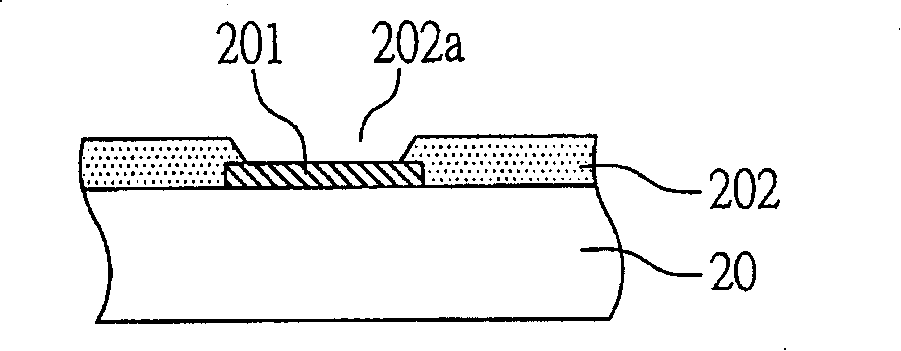

[0078] Such as Figure 2A As shown, firstly, a semiconductor base material 20 with a plurality of welding pads 201 and a protective layer 202 is prefabricated on the surface (in this figure, only the area covered by a single welding pad 201 is illustrated), and the semiconductor base material is, for example, a semiconductor A chip or wafer comprising a plurality of chip units. The semiconductor substrate 20 is covered with a protective layer 202, and the protective layer 202 has an opening 202a to expose the pad 201. The material of the protective layer 202 is, for example, polyimide (PI) to protect the semiconductor substrate. 20.

[0079] Such as Figure 2B As shown, the first metal layer 241 is directly formed on the semiconductor substrate 20 , and the first meta...

no. 2 example

[0093] see image 3 , is a schematic cross-sectional view of the second embodiment of the semiconductor device with conductive bumps of the present invention. The semiconductor device with conductive bumps in this embodiment is roughly the same as the previous embodiment, and the main difference is that when the protective layer material of the semiconductor substrate is such as When it is a nitride (such as silicon nitride), a first covering layer can be covered on the protective layer first, and then a first metal layer, a second covering, a second metal layer, and a second metal layer are sequentially formed on the first covering layer. The third covering layer, the metal post and the solder material.

[0094] As shown in the figure, the first covering layer 331 covers the protective layer 302 of the semiconductor substrate 30 and exposes the solder pad 301. The first covering layer 331 can be selected from benzo-cyclobutene (Benzo-Cyclo- One of Butene; BCB) and polyimide ...

no. 3 example

[0097] see Figure 4 , is a schematic cross-sectional view of the third embodiment of the semiconductor device with conductive bumps of the present invention, the semiconductor device with conductive bumps of this embodiment is roughly the same as the first embodiment, the main difference is that a solder pad 401 is provided on the surface A first metal layer 441, a second covering layer 432, and a second metal layer 442 are successively formed on the semiconductor substrate 40 of the protective layer 402, and the second metal layer 442 is electrically connected to the first metal layer 441, Then cover the third covering layer 433 on the second metal layer 442 and the second covering layer 432, and make the third covering layer 433 correspond to the position vertically above the welding pad 401 to be provided with an opening 433a, exposing part of the first Two metal layers 442 .

[0098] Next, a third metal layer 443 is formed on the second metal layer 442 exposing the openi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More