A self-adapted tolerance method based on learning for chip network

A network-on-chip, self-adaptive technology used in error prevention/detection using return channels, error prevention, digital transmission systems, etc., and can solve problems such as path performance degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

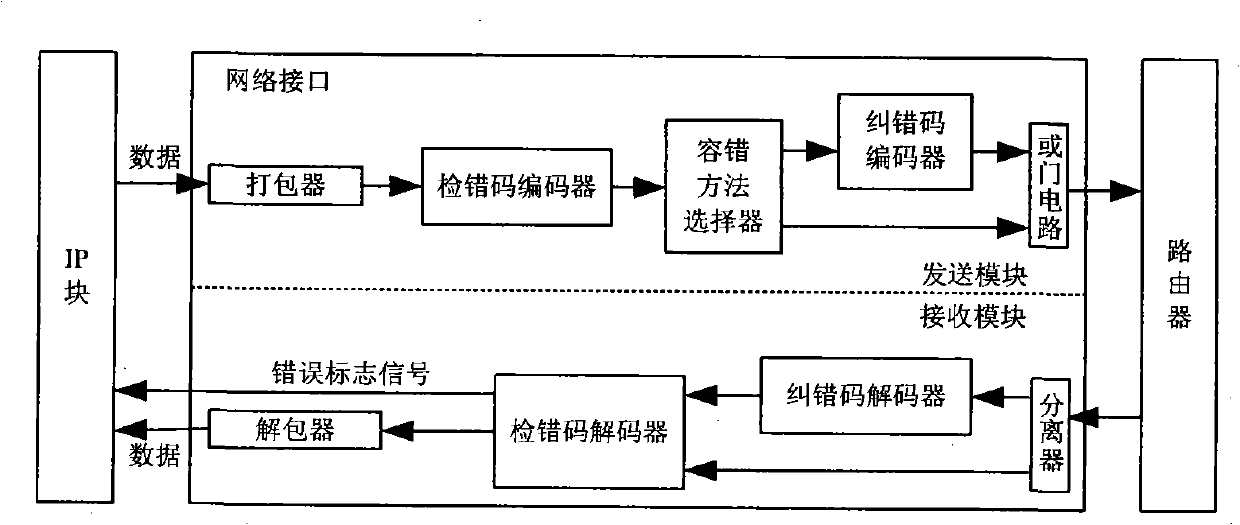

Embodiment Construction

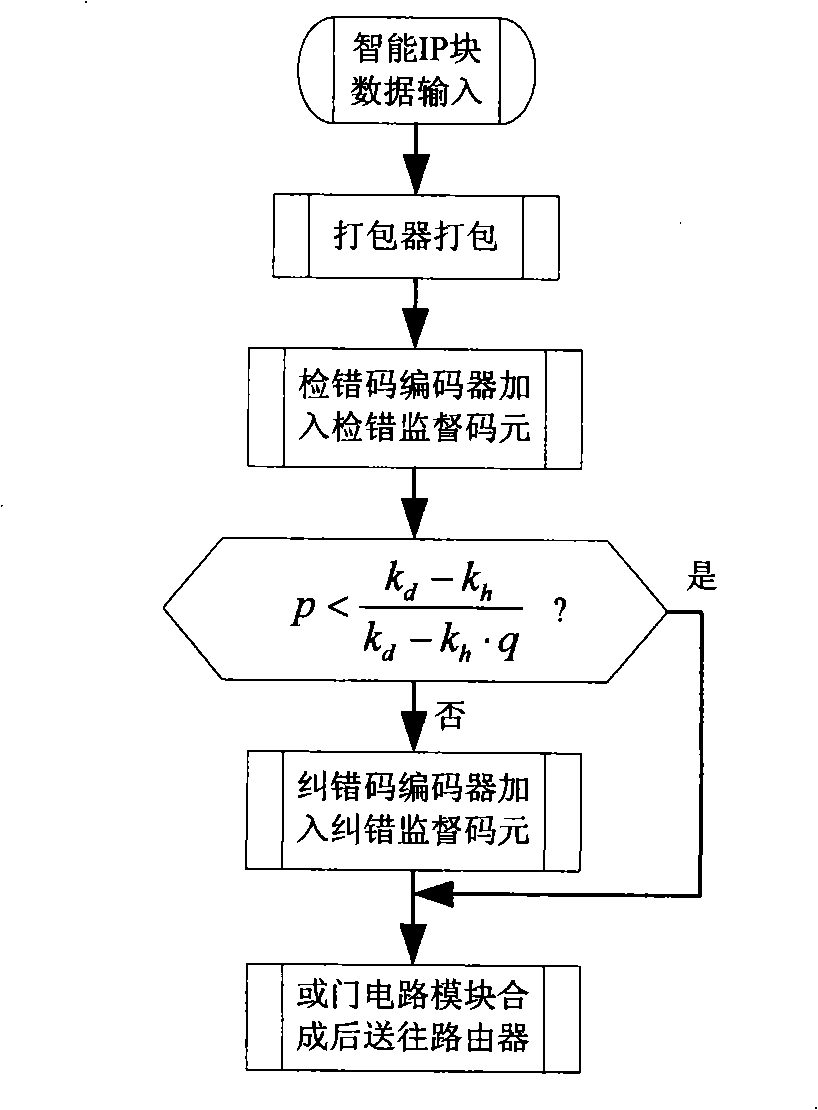

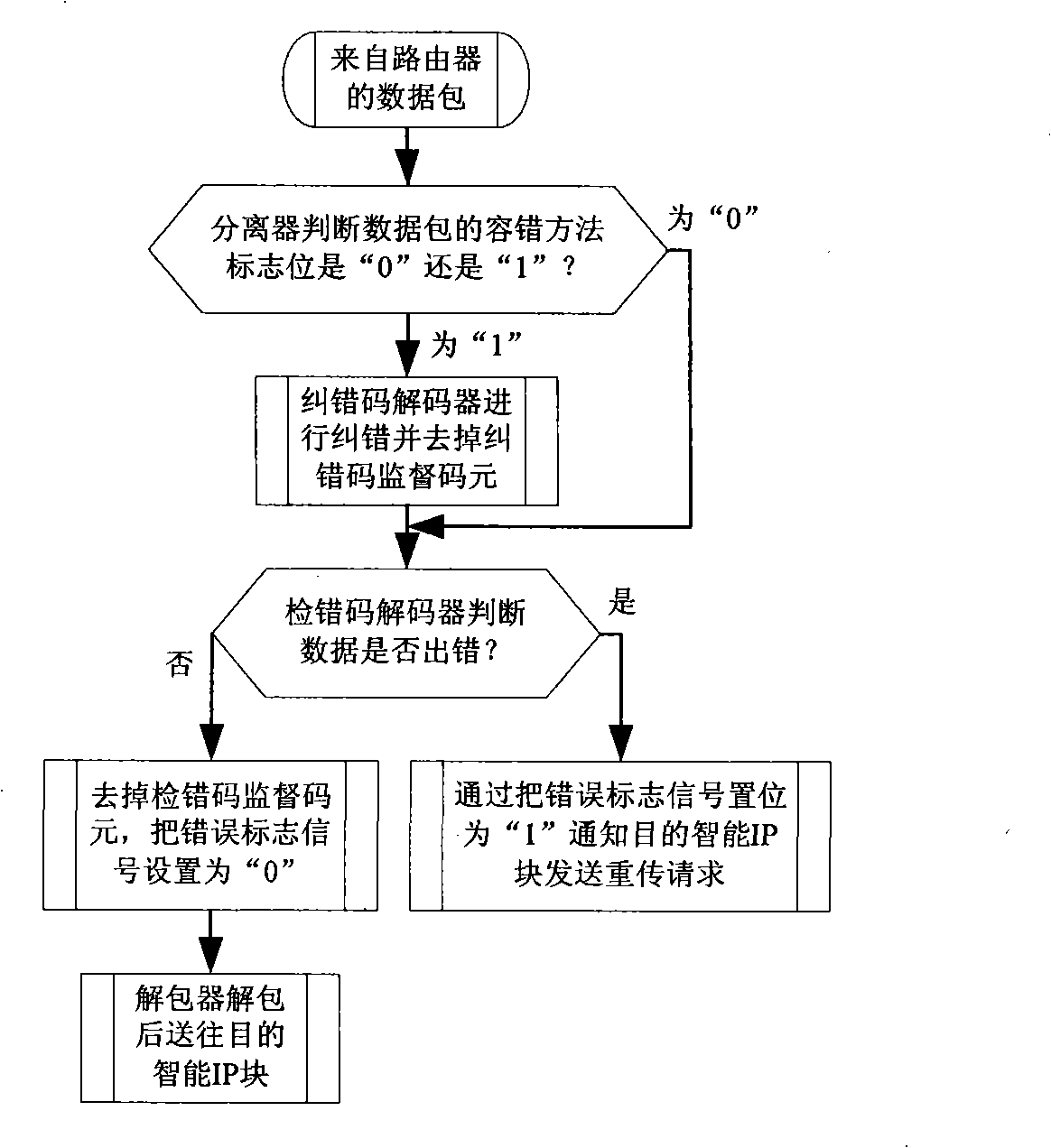

[0022] This method first analyzes and derives the end-to-end error retransmission method and the hybrid fault-tolerant method, and obtains a fault-tolerant method selection formula. Through this formula, we can select the fault-tolerant method with less redundant bits required to achieve error-free transmission. method. Then, after the on-chip network is established, the fault-tolerant method selector sends a known sequence to each link. We call this process learning. According to the learning results and the previously derived formula, the fault-tolerant method selector selects the optimal path for different paths. (less redundant bits needed to achieve error-free transmission) error-tolerant method.

[0023] The following introduces our analysis and derivation process of the end-to-end error retransmission method and the hybrid fault tolerance method. Before the derivation, we first define the following:

[0024] 1) The code length is N.

[0025] 2) Coding efficiency k, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More