Structure for testing integrality of grid medium layer, forming method and test method thereof

A gate dielectric layer and test structure technology, which is applied in semiconductor/solid-state device testing/measurement, electrical components, electric solid-state devices, etc., can solve the problems of increased process cost, long cycle period, product impact, etc., and achieve process cost saving, Good repeatability and reduced process risk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

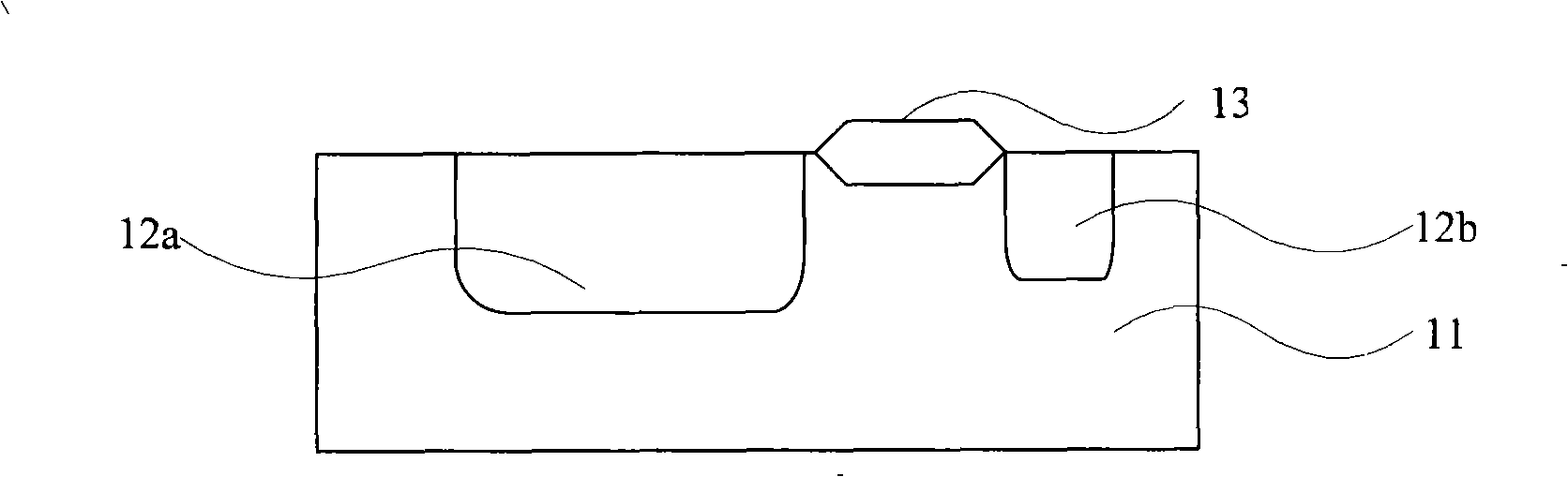

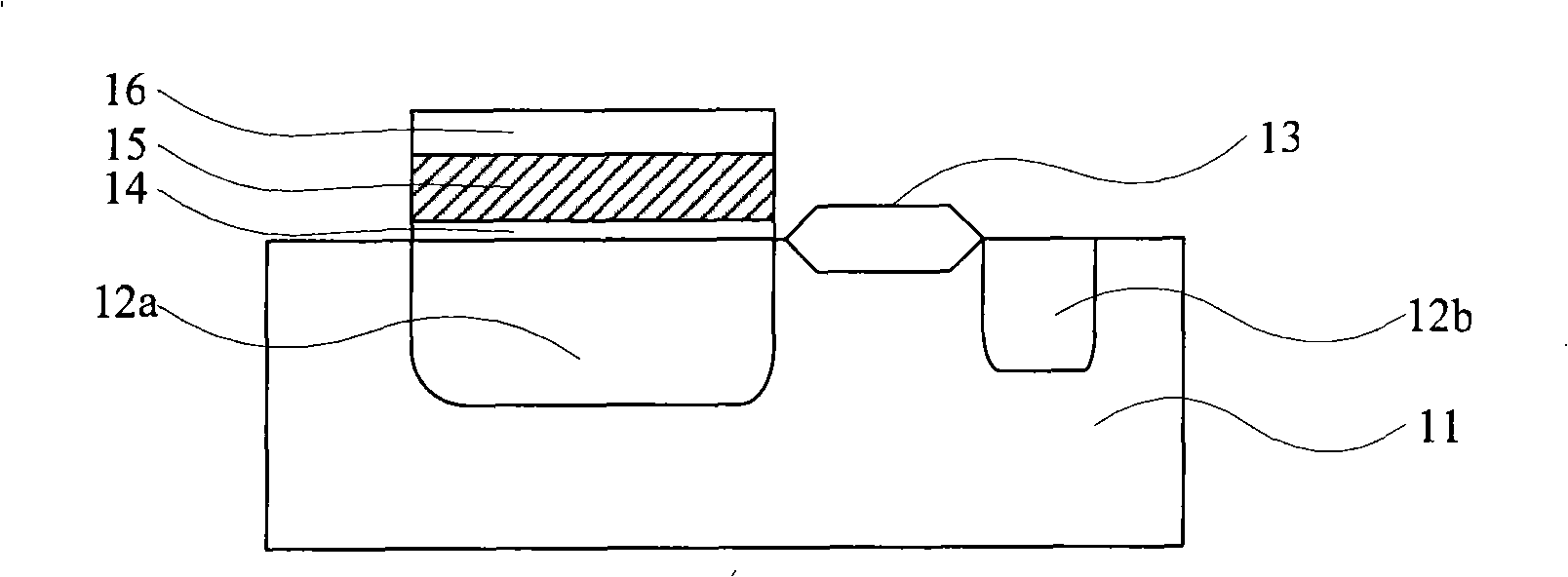

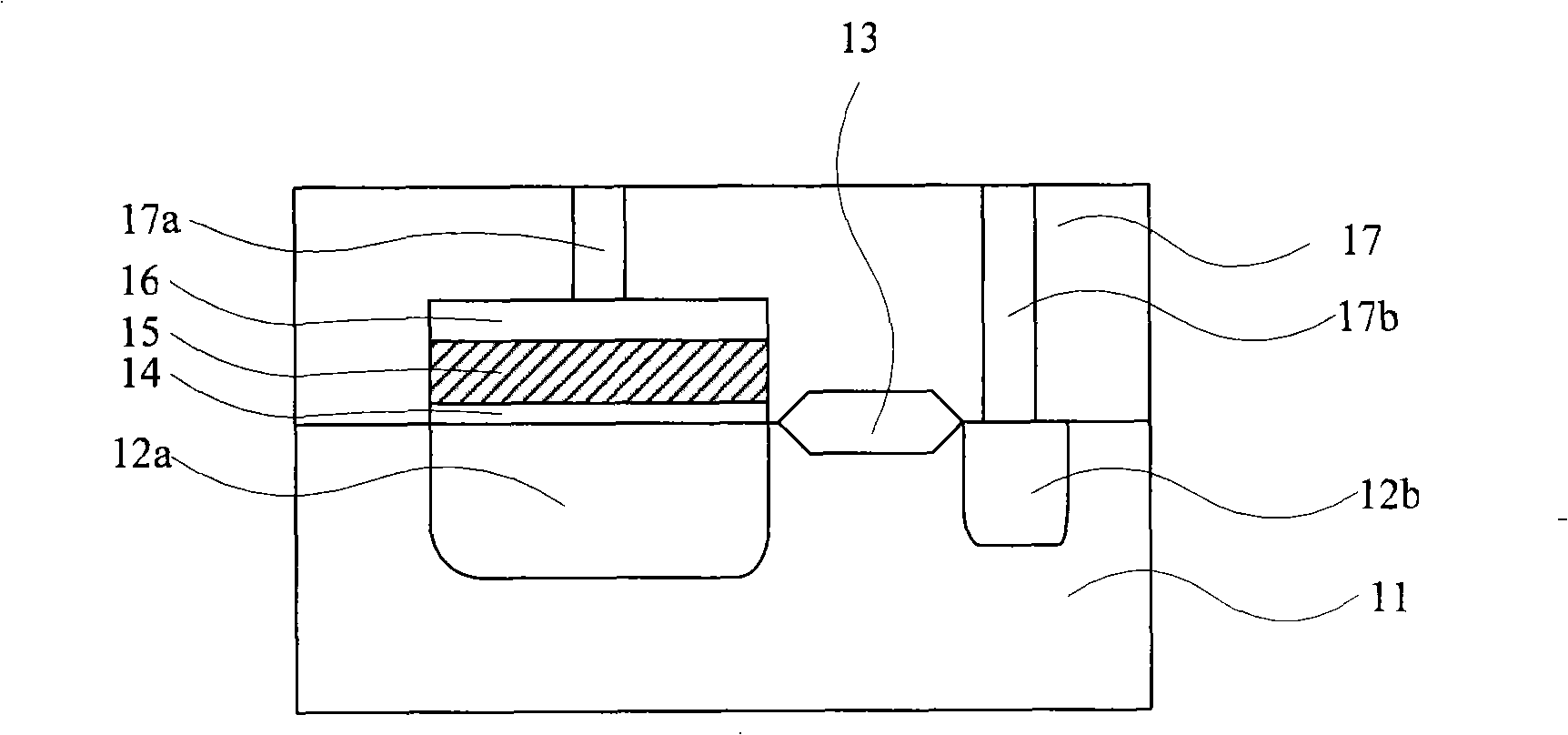

[0027] The essence of the present invention is to provide a test structure for the integrity of the gate dielectric layer and its formation method. The present invention forms the integrity of the gate dielectric layer of the present invention by forming isolation grooves, gate dielectric layers, and gate electrode layers on the semiconductor substrate. Sexual test structure. Apply a negative gate voltage on the gate electrode through the probe, ground the semiconductor substrate, and conduct an electrical test. Since the contact resistance between the probe and the gate electrode is small, the electrical test result is consistent with the integrity of the gate dielectric layer in the prior art. The test results of the test structure are comparable, and the repeatability of the test results is good, indicating that the test result of the test structure using the integrity of the gate dielectric layer of the present invention is reliable and can accurately reflect the integrity ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More