CMOS image sensor chip scale package with die receiving opening and method of the same

A technology of image sensors and grains, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., and can solve problems such as increased thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Certain similar embodiments of the invention will not be described in detail. However, it should be understood that all the preferred embodiments in the present invention are only used for illustration rather than limitation. Therefore, except for the preferred embodiments herein, the present invention can also be widely applied in other embodiments. The dimensions of different components are not particularly described, and the dimensions of certain related components are enlarged and meaningless parts are omitted to clearly describe and emphasize the content of the present invention.

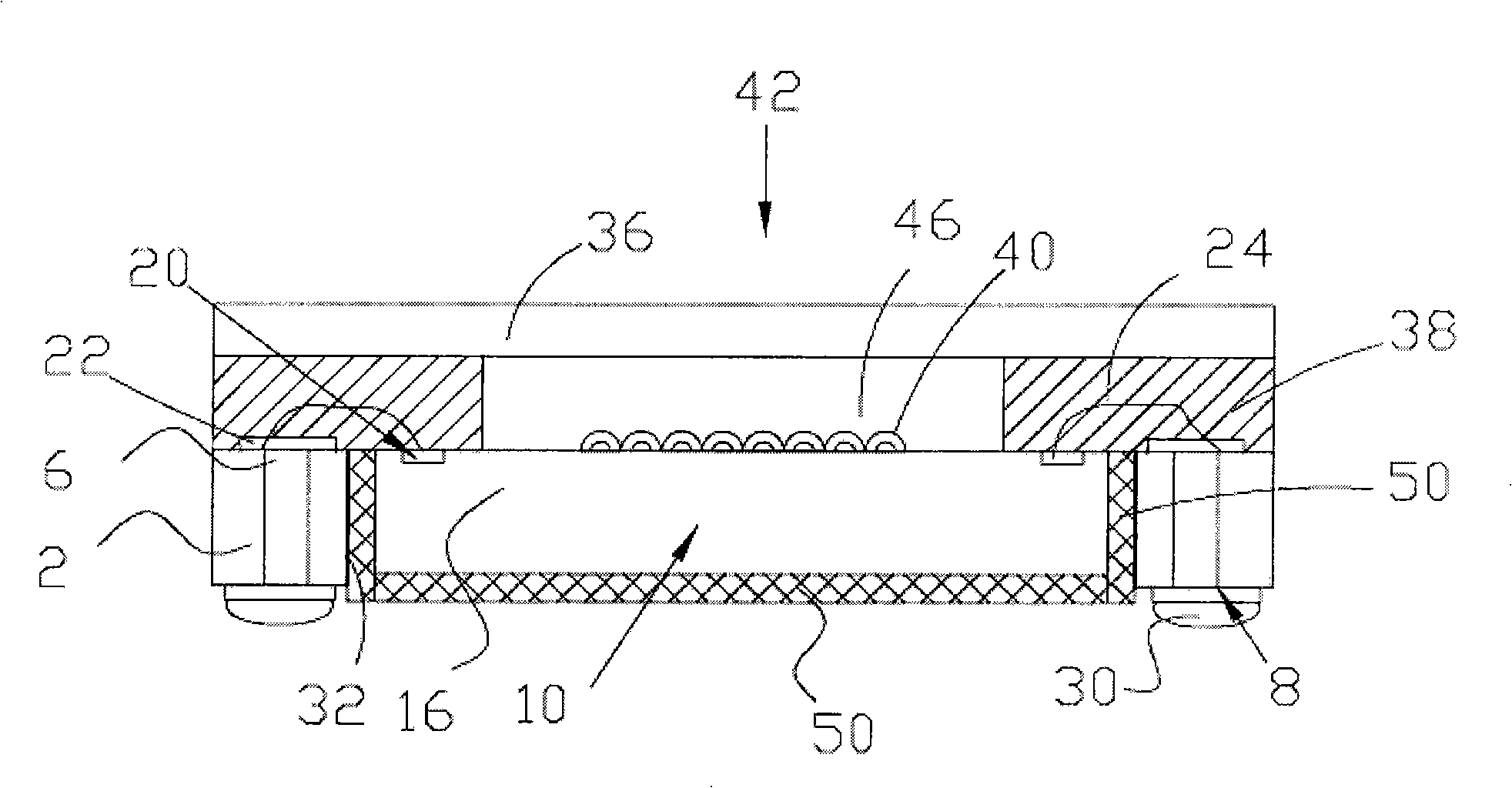

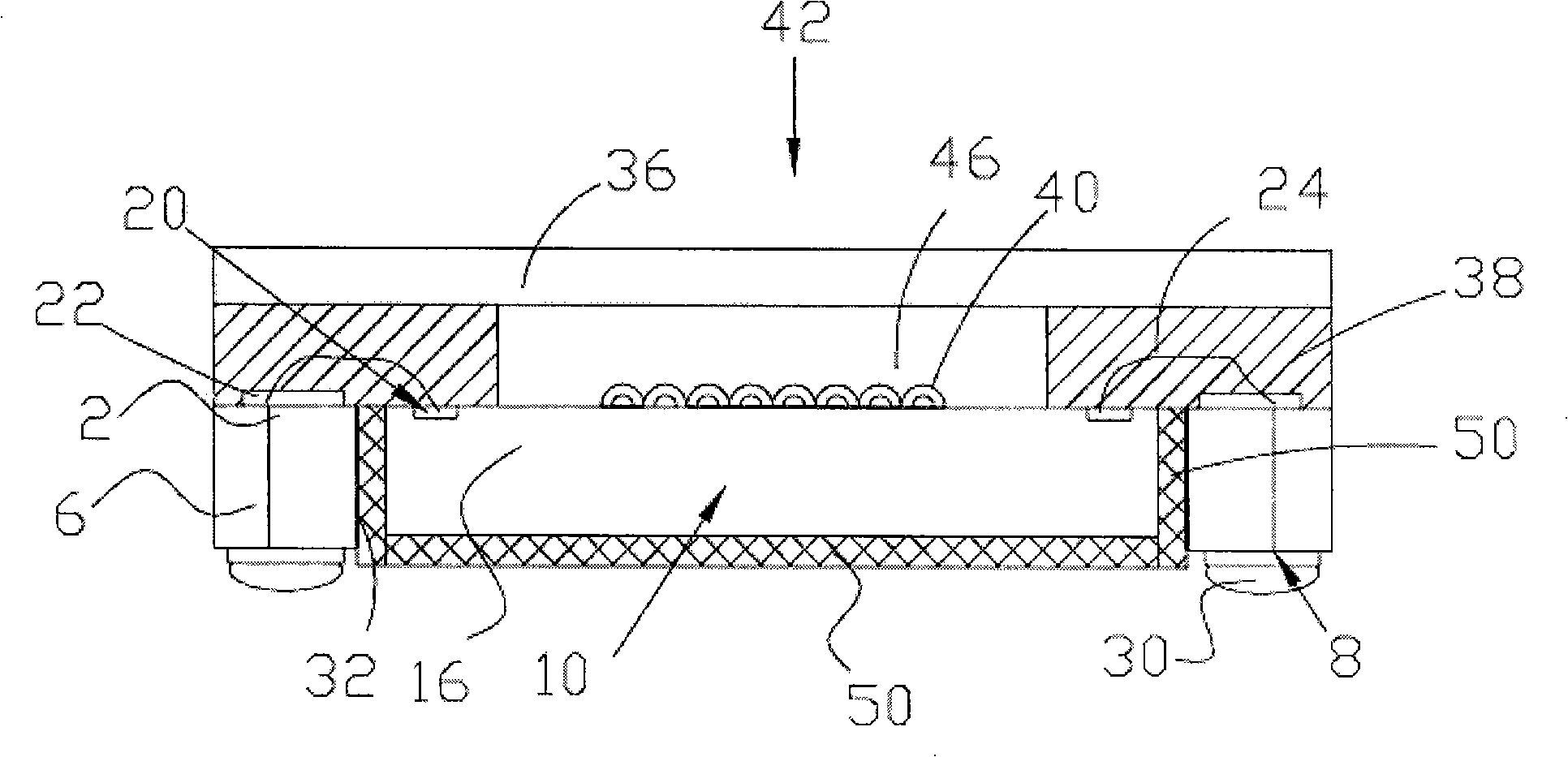

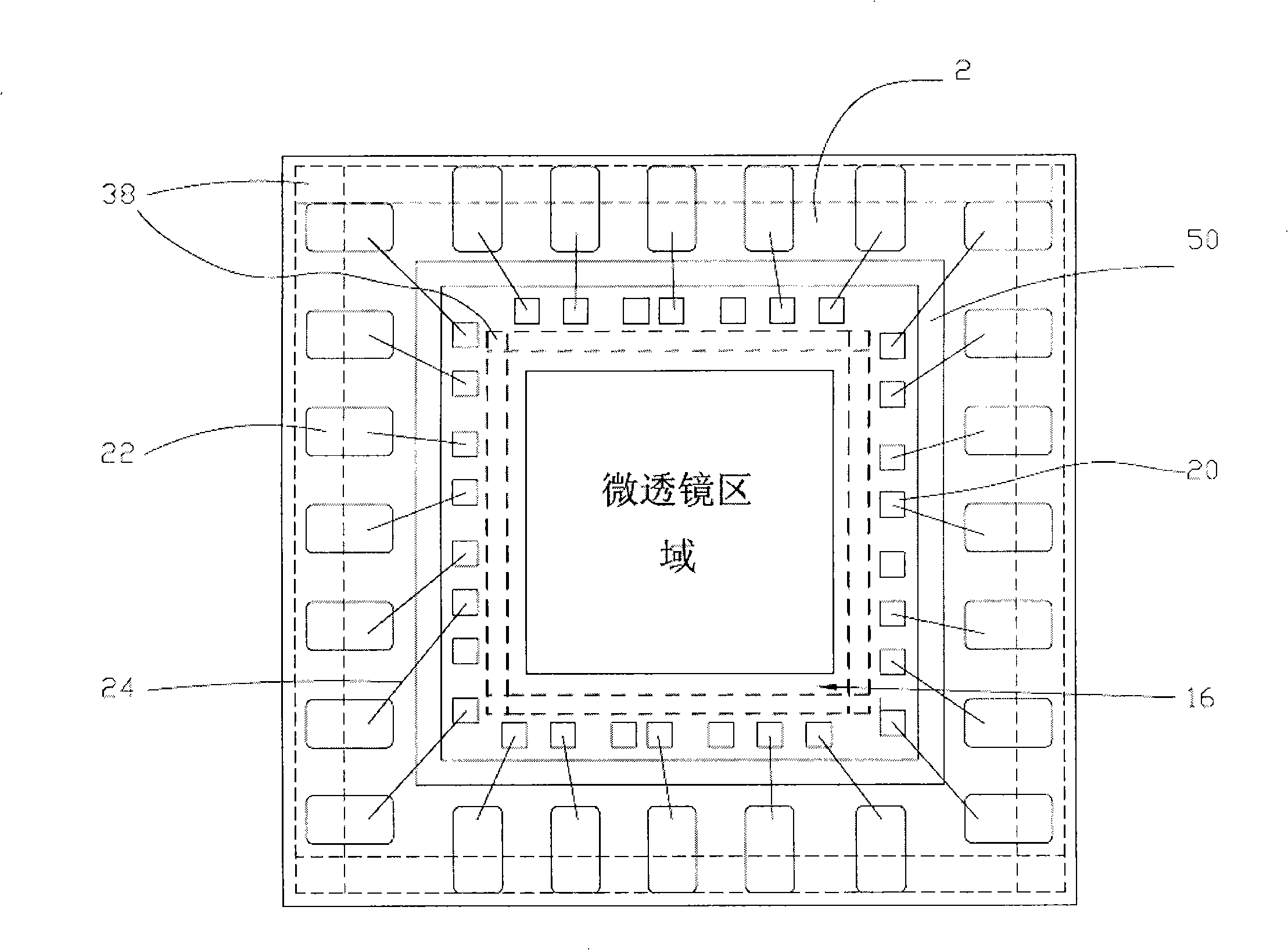

[0019] The invention discloses a PLP which adopts preset grain perforation and contact (internal connection) perforation on the substrate, the contact metal pad is located above the substrate, and the terminal contact pad is located below the substrate, and the two are connected through the metal in the perforation hole. A plurality of through holes pass through the substrate. Bonding w...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More