Electric isolation region forming method adopting low temperature process, single chip integration method and chip

A technology of electrical isolation and low-temperature technology, which is applied to the technology for producing decorative surface effects, metal material coating technology, TV, etc., and can solve problems such as difficult to achieve post-IC technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

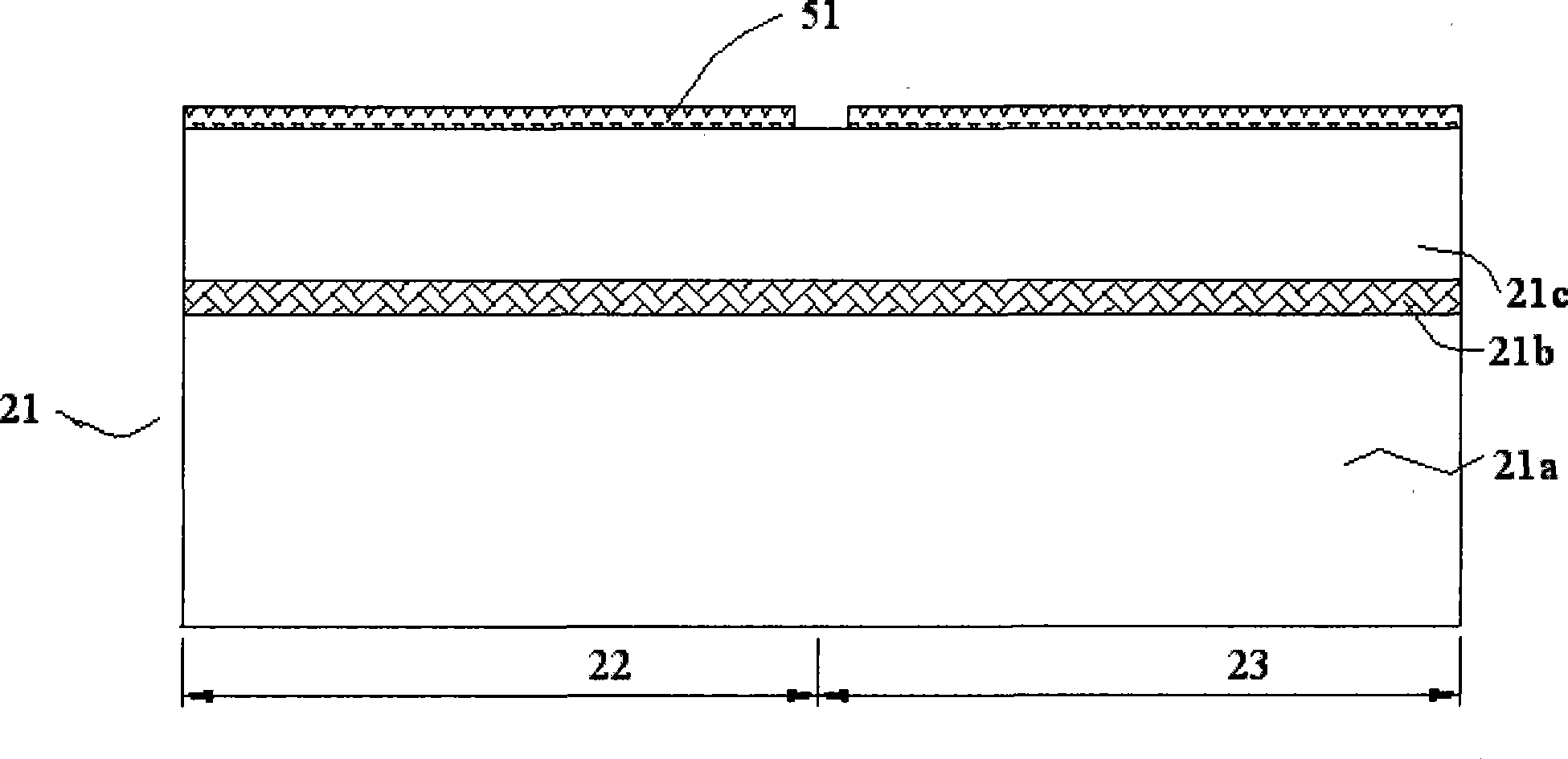

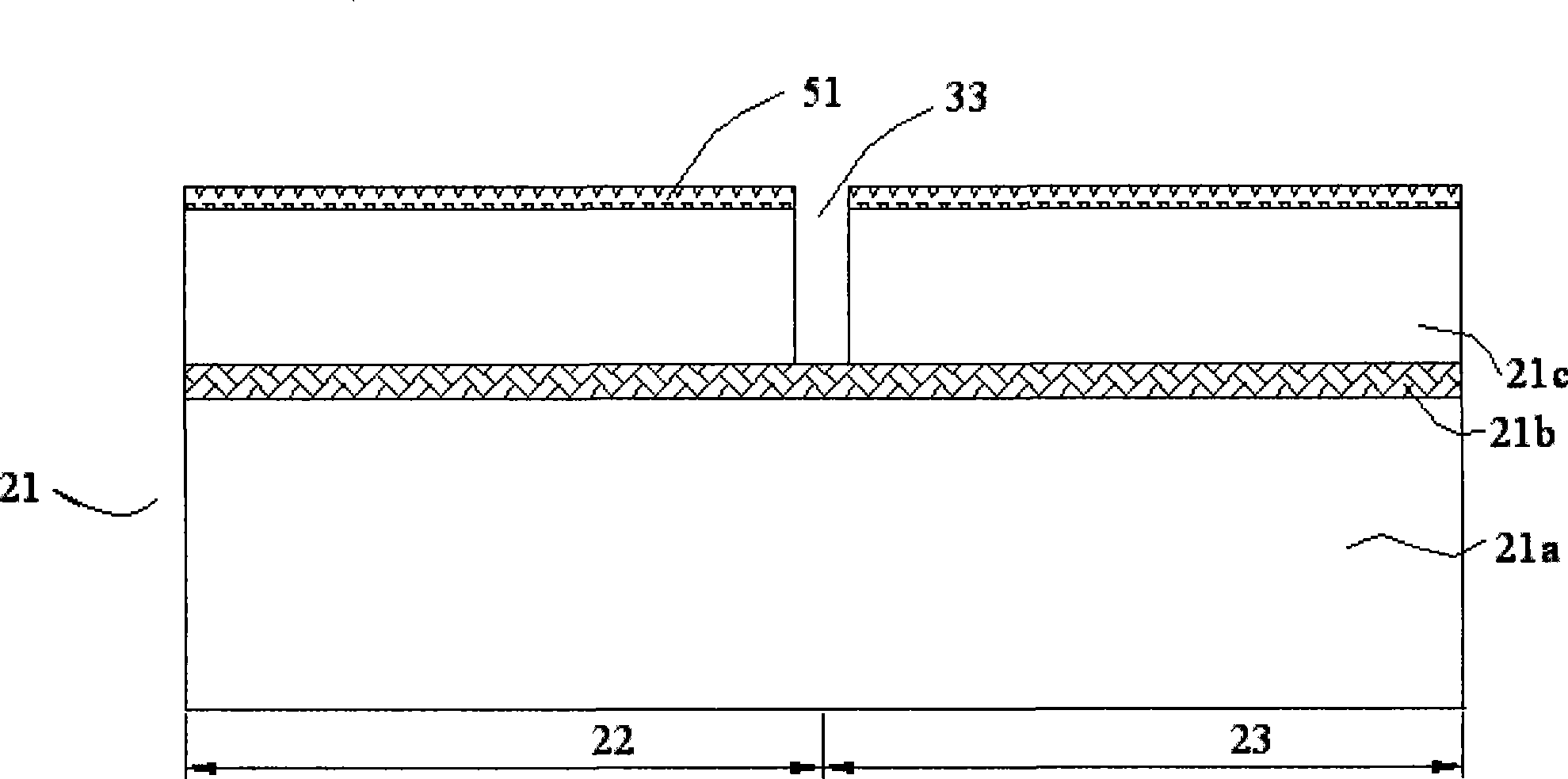

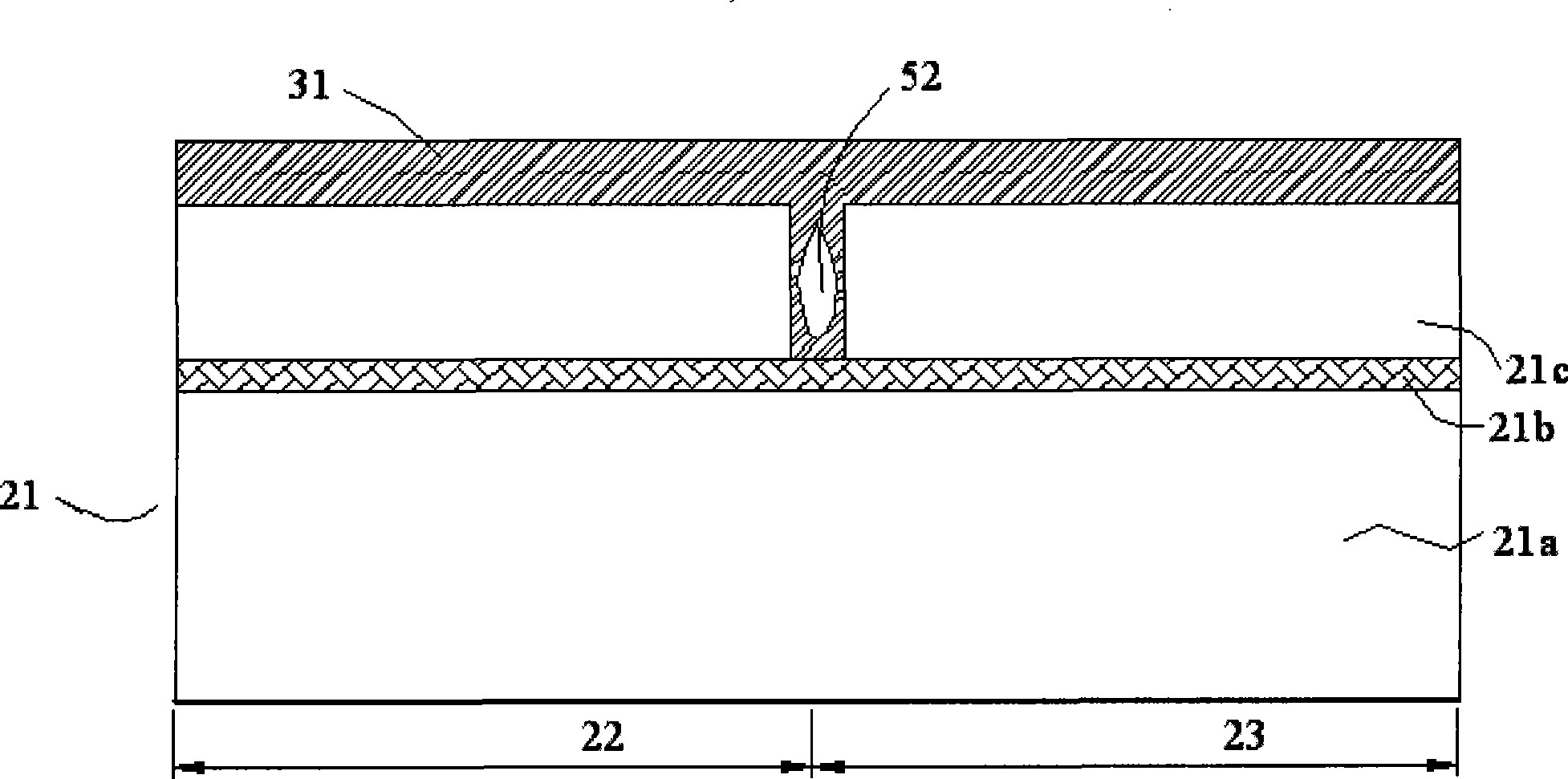

[0030] see Figures 1A-1E , the method for forming an electrical isolation region using a low-temperature process on an insulating silicon substrate may include the following steps:

[0031] First, if Figure 1A and Figure 1B As shown, according to the design requirements, the corresponding part of the device layer 21c of a silicon-on-insulator (SOI) substrate 21 is etched by deep groove reactive ion etching method or plasma dry etching method, and the etching is carried out to the silicon-insulator substrate. The silicon oxide buried layer 21b (between the device layer 21c and the substrate 21a of the insulating silicon substrate 21) that the sheet 21 has is used to form the corresponding isolation groove 33, and the insulating silicon substrate 21 is covered by the isolation groove 33 is divided into electrical isolation regions 22 and 23. For example, a mask layer 51 for deep groove reactive ion etching (DRIE) is usually formed on the device layer 21c first. This layer ca...

Embodiment 2

[0036] See Figure 2A-2E , the method for forming an electrical isolation region on an insulating silicon substrate using a low-temperature process may also include the following steps:

[0037] First, if Figure 2A As shown, according to design requirements, wet etching is used to etch the corresponding part of the device layer 21c that an insulating silicon substrate 21 has, and the etching is carried out to the silicon oxide buried layer 21b (in the insulating silicon substrate 21) that the insulating silicon substrate 21 has. between the device layer 21c of the silicon substrate 21 and the substrate 21a) to form a corresponding isolation groove 33, while the insulating silicon substrate 21 is separated into electrical isolation regions 22 and 23 by the isolation groove, for example, prior to the device A mask layer 61 for wet etching is formed on the layer 21c, and this layer can be a photoresist, or be deposited by a low temperature (less than 400°C) process (less than 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More