LDMOS chip light doped drift region structure and forming method

A lightly doped, drift region technology, applied in the fields of communication and radar, can solve the problems of low frequency gain of LDMOS devices, deterioration of device frequency and power characteristics, and total reduction of LDD impurities, so as to improve device breakdown voltage, Improved frequency and power performance, optimized positive ion distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

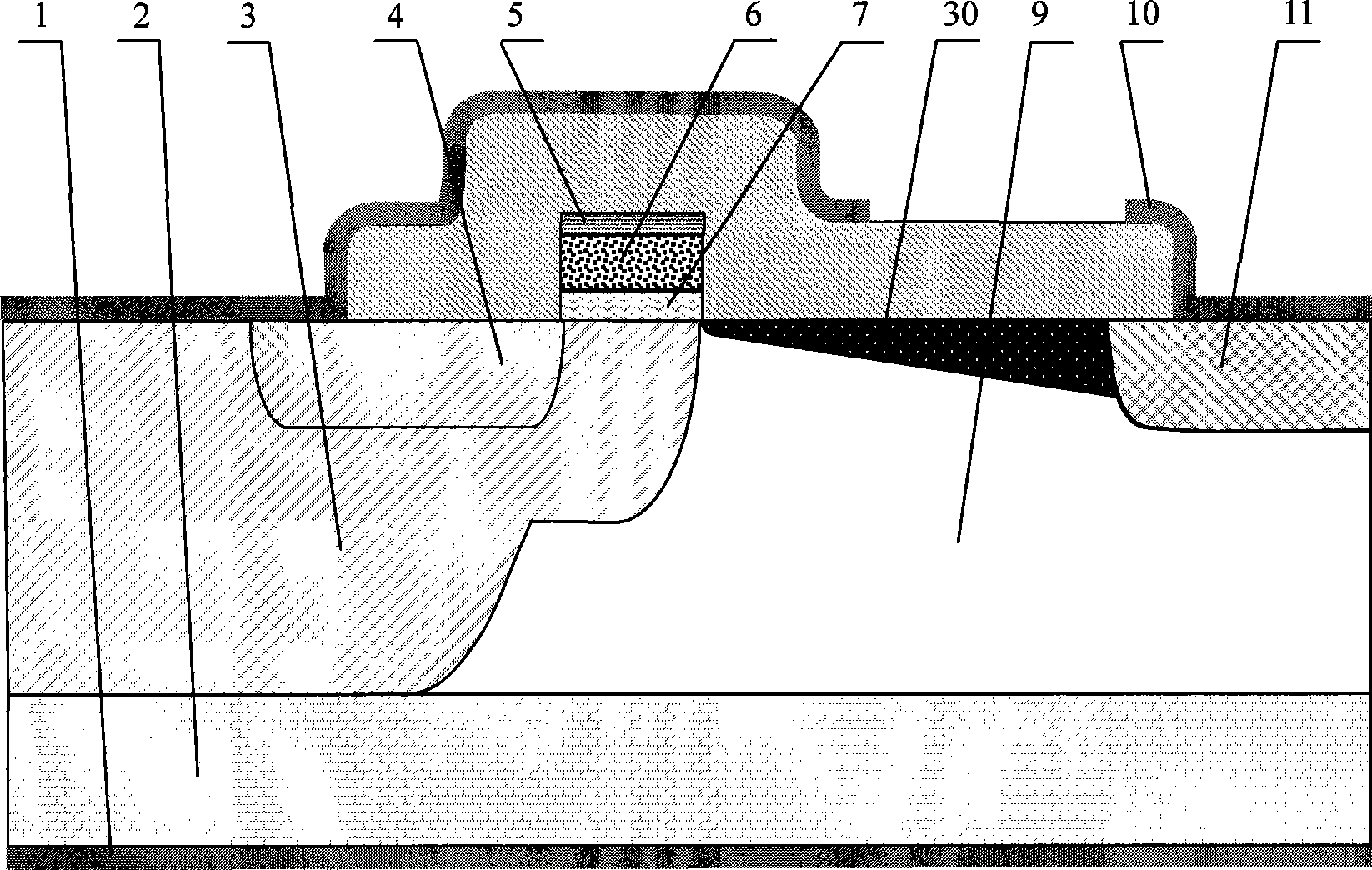

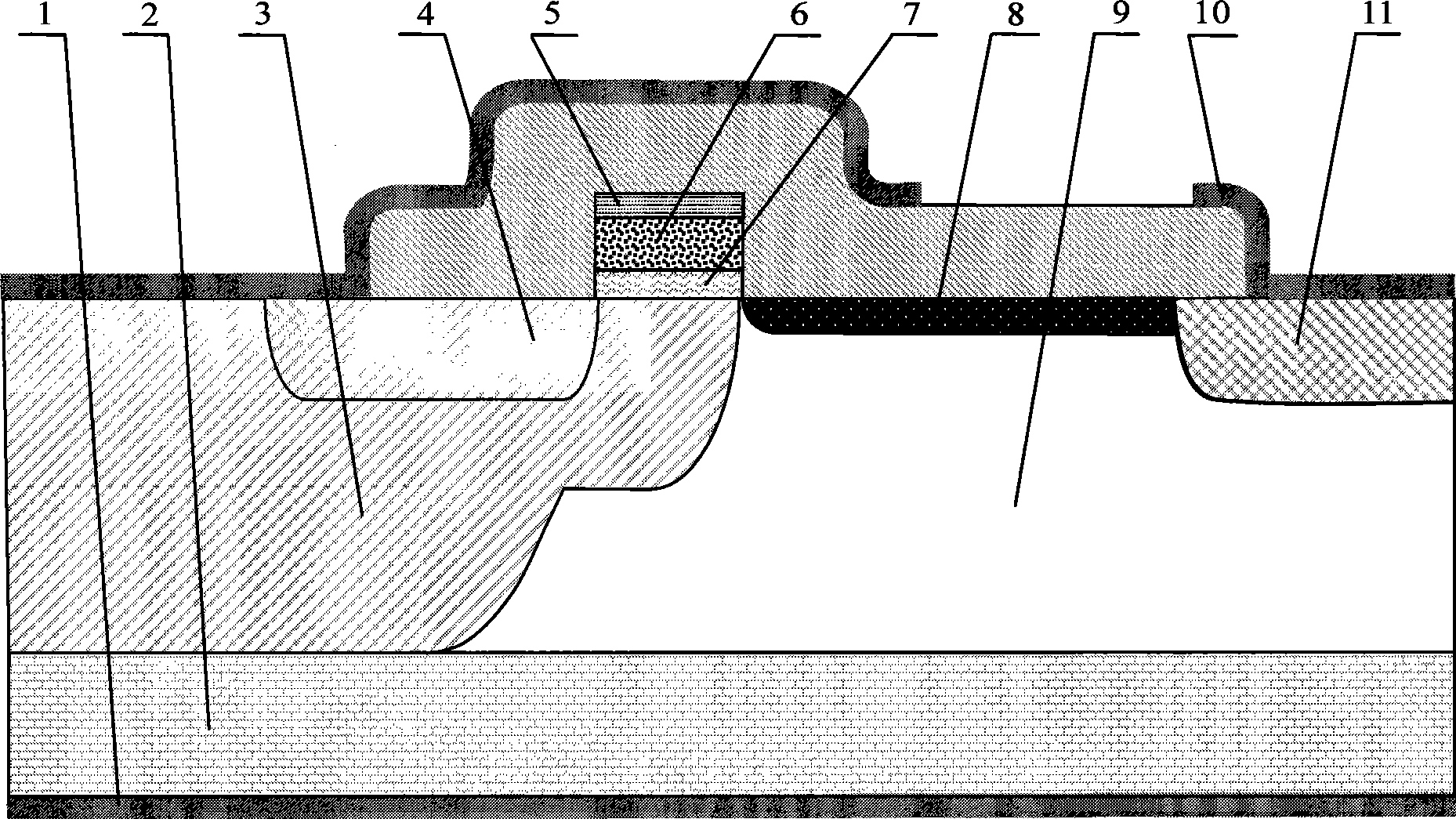

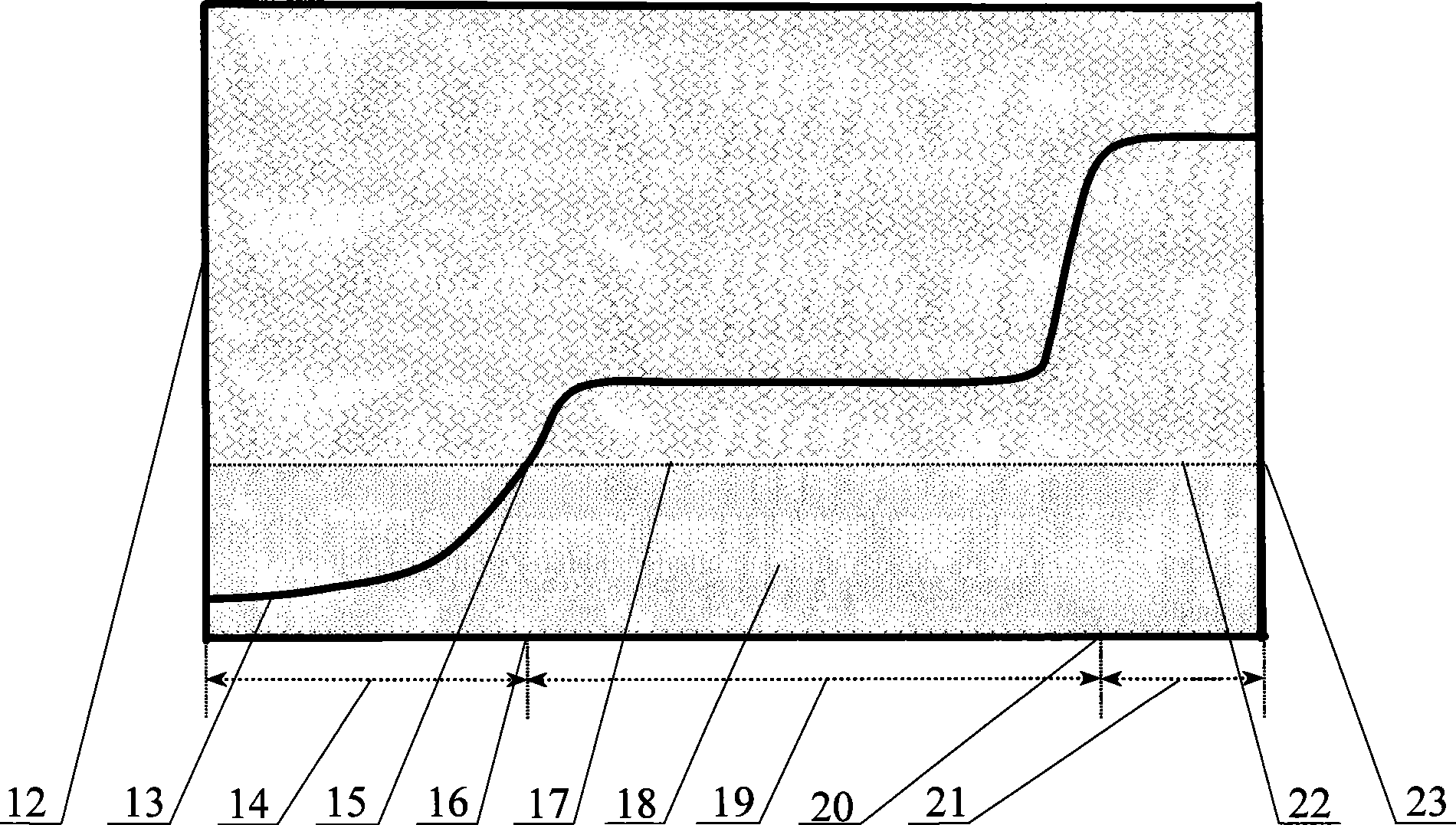

[0021] As shown in Figure 5, the structure of the present invention includes source 1, P+ substrate 2, P-type double diffusion region 3, N-type source region 4, metal silicide and gate 5, gate polysilicon 6, gate oxide 7, Conventional lightly doped drift region (LDD) 30, P-type epitaxy 9, drain 10, N-type drain 11, etc., P-type double diffusion region 3 forms a channel region under the gate oxide 7, and LDD 30 is located in the channel Between the channel region and the N-type drain region 11, the LDMOS chip structure of the present invention is characterized in that the LDD 30 formed between the channel region and the N-type drain region 11 has a non-uniform doping concentration, and the doping concentration is in the vertical direction (from the chip From the upper surface to the lower surface to the bottom of the censer) and laterally (the side close to the gate area to the side close to the drain area) simultaneously form a concentration gradient. As shown in Figure 6, 12 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More