Analog probability AND gate circuit designed by CMOS transistor

A transistor and gate circuit technology, applied in the field of signal and information processing and integrated circuit design, can solve the problems of complex circuit design, easy to be interfered by noise, inaccurate and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

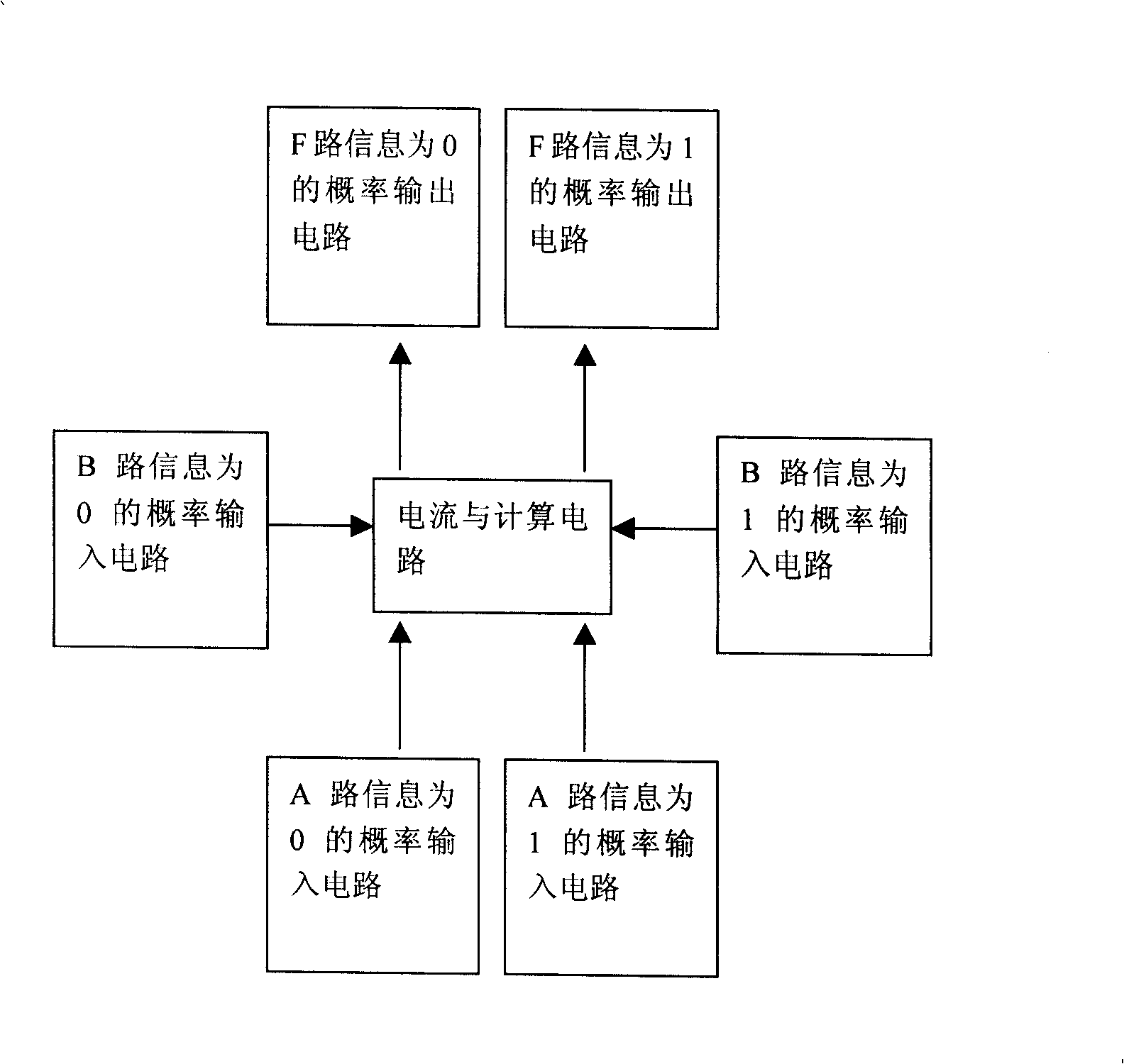

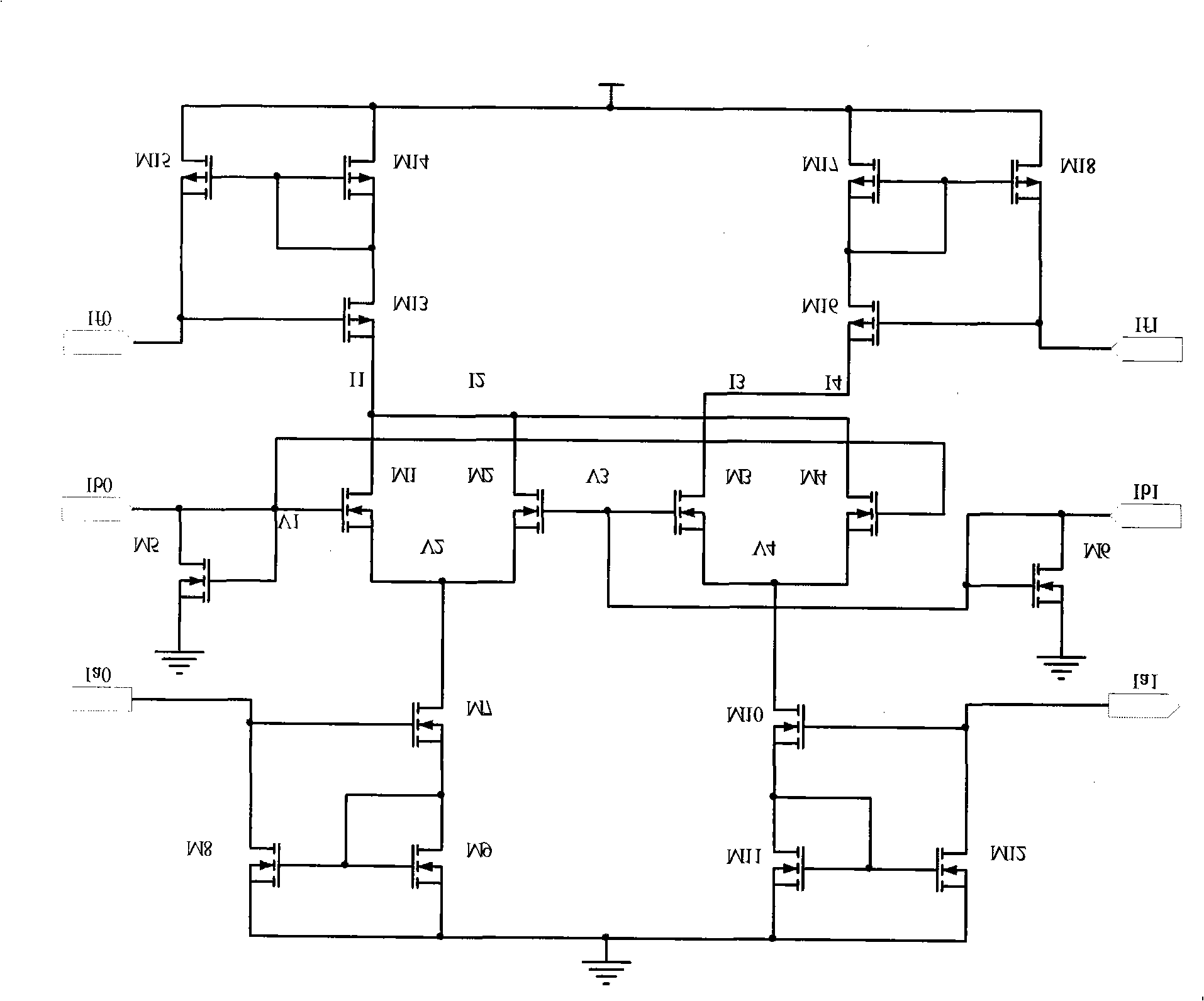

[0012] The purpose of the present invention is achieved through the following technical solutions: mainly composed of current input, output circuit and analog multiplier circuit. The input and output current values are used to represent the input and output probability values, and the calculation of probability is realized through different structural forms of the circuit. Using MOS transistors, the current input circuit representing the A and B circuits, the current output circuit representing the F circuit, and the analog circuit for probability and calculation using the current value are designed. Functionally, the output probability value is the AND result of the two input probability values.

[0013] The advantages of the present invention are:

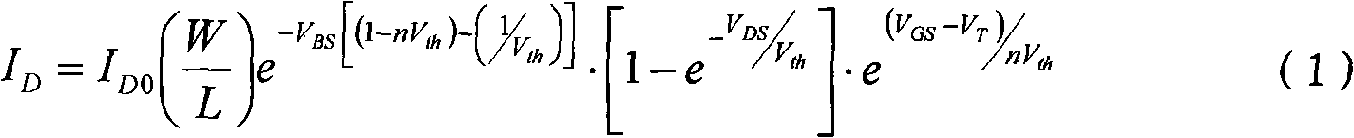

[0014] 1. The MOS tube of the analog multiplier unit works in a sub-threshold state, and the voltage and current have an exponential characteristic similar to that of a bipolar transistor. The circuit structure for realizing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More